Fターム[5J056EE08]の内容

Fターム[5J056EE08]に分類される特許

61 - 80 / 232

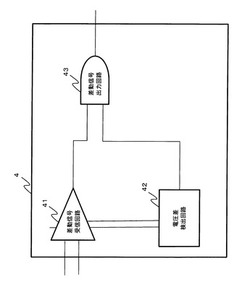

信号中継回路、信号中継装置及び信号中継方法

【課題】回路の誤作動を防止することができる信号中継回路、信号中継装置及び信号中継方法を提供すること

【解決手段】本発明にかかる信号中継回路は、2つの入力信号の電圧差に基づいて差動信号を生成する差動信号受信回路41と、差動信号受信回路41に入力される2つの入力信号の電圧差の有無を検出する電圧差検出回路42と、電圧差検出回路42により電圧差が検出されない場合には、所定の値を有する信号を出力し、電圧差検出回路42により電圧差が検出される場合には、差動信号受信回路41により生成された差動信号を出力する差動信号出力回路43と、を備えるものである。

(もっと読む)

インピーダンス調整回路

【課題】伝送経路の入力バッファ端のインピーダンスの最適化を実現可能なインピーダンス調整回路を提供すること。

【解決手段】本発明に係るインピーダンス調整回路100は、入力信号がVREFA6を超えたことを検出する第1の入力バッファ4と、入力信号がVREFA6より高いVREFA7を超えたことを検出する第2の入力バッファ5と、第1の入力バッファ4の出力に基づく計数を行うカウンタ回路A10と、第2の入力バッファ5の出力に基づく計数を行うカウンタ回路B11と、カウンタ回路A10のカウンタによる計数結果とカウンタ回路B11による計数結果とに基づいて、伝送路の終端に設けられる終端抵抗3のインピーダンスを制御する終端抵抗制御回路19と、を備える。

(もっと読む)

半導体集積回路

【課題】電源線のレイアウト面積を広げることなく、コア回路とバイアス供給回路との間

の電圧降下を抑え、かつ、コア回路間の高速信号ノードを短縮できるようにする。

【解決手段】Si基板11にトランジスタQ及び抵抗素子Rを有して高電位側の電源線と

低電位側の配線D1とバイアス供給用の配線D2とに接続されてトランジスタ動作をする

コア回路1と、Si基板11に設けられてコア回路1にバイアスを供給するバイアス供給

回路とを備え、コア回路1の中の定電流源用のトランジスタQに、その一端が接続された

抵抗素子Rの他端がバイアス供給用の配線D2に接続され、この配線D2が接続された抵

抗素子Rの他端がコンタクトホール35を介してバイアス供給用の配線D2よりも上層の

低電位側の配線D1に接続されるものである。

(もっと読む)

半導体集積回路装置

【課題】小さい面積で十分な遅延時間を確保する。

【解決手段】 入力に基づいて充電点に充電を行う第1のトランジスタと前記入力に基づいて放電点から放電を行う第2のトランジスタとにより構成される第1のインバータ(PT21,NT21)と、前記充電点と前記放電点との間に、ドレイン・ソース路が並列に設けられたP型の第3のトランジスタ及びN型の第4のトランジスタ(PT22,NT22)と、前記充電点又は前記放電点の電位を反転させて前記第3及び第4のトランジスタのゲートに供給して、前記充電点又は前記放電点から前記入力の遅延信号を得る第2のインバータ(INV21)とを具備したことを特徴とする。

(もっと読む)

半導体集積回路

【課題】 半導体集積回路の消費電流を削減する。

【解決手段】 直列に接続された第1、第2および第3インバータは、第1および第2電源線の間に接続される。第1インバータは入力信号を受ける。第1トランジスタは、第1および第2インバータとの間に配置され、ゲートに第1電源電圧が供給される。第2トランジスタは、第2および第3インバータとの間に配置され、ゲートに第2電源電圧が供給される。第1スイッチは、スタンバイ信号に基づいて第1または第3電源電圧を供給する。第2スイッチは、スタンバイ信号に基づいて第2または第4電源電圧を供給する。第3トランジスタは、第2インバータの入力と第1スイッチとの間に配置され、ゲートに第2インバータの出力が供給される。第4トランジスタは、第3インバータの入力と第2スイッチとの間に配置され、ゲートに第3インバータの出力が供給される。

(もっと読む)

半導体記憶装置

【課題】Duty誤差を低減でき、高速なデータ入出力に有利な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、電気的に回路閾値を調節可能な第1インバータINV1−1を備える入力バッファ12と、前記第1インバータと共通の回路構成の第2インバータINV1−2を備え、前記第2インバータの入力と出力とが短絡されることにより前記第1インバータの回路閾値を検出する回路閾値モニタ13と、前記回路閾値モニタが検出した回路閾値に対応するパラメータ値を記憶するメモリ11−2と、前記第1インバータに与えられる前記パラメータ値を、前記メモリから読み出すデータ読み出し回路15とを具備する。

(もっと読む)

ターミネーション回路及びそれを備えるインピーダンス整合装置

【課題】回路面積を増加させることなく、多様なターミネーションインピーダンス値を提供するターミネーション回路及びこれを備えるインピーダンス整合装置を提供すること。

【解決手段】本発明に係るインピーダンス整合装置は、インピーダンス値を較正するためのインピーダンス調整コードを生成するキャリブレーション回路310と、インピーダンス値設定情報に応じて前記インピーダンス調整コードを変更し、変更された前記インピーダンス調整コードを出力するコード変更部320と、変更された前記インピーダンス調整コードに応じて決定されるインピーダンス値でインタフェースノードをターミネーションするターミネーションインピーダンス部330、340と、を備える。

(もっと読む)

半導体装置及び半導体装置の動作方法

【課題】電源電圧を変更することなく、広い温度範囲でリーク電流を抑えて動作する半導体装置を提供する。

【解決手段】しきい値電圧が第1電圧である第1トランジスタを含む高VT部7と、しきい値電圧が第1電圧よりも低い第2電圧である第2トランジスタを含む低VT部8と、温度を測定し、温度が所定の温度より高い高温状態であるか、温度が所定の温度よりも低い低温状態であるかを判定し、高温状態を示す信号又は低温状態を示す信号を出力する温度検知部6と、高温状態を示す信号、又は低温状態を示す信号を受信し、高温状態を示す信号に基づいて高VT部7を動作させ、低温状態を示す信号に基づいて低VT部8を動作させる制御を行う制御部9とを具備する。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

入力インターフェイス回路

【課題】簡単な構成で、電源電位より低い入力信号電圧であっても誤動作が起き難い、安価な入力インターフェイス回路を提供する。

【解決手段】PチャネルMOSトランジスタM1とNチャネルMOSトランジスタM2が直列接続され、ゲート端子Gが共通接続されてなるCMOSインバータC10を有した入力インターフェイス回路I10であって、共通接続されてなるゲート端子Gを入力端子とし、電源端子と接地端子の間で、閾値電圧を有する半導体素子S10とCMOSインバータC10とが直列接続されてなり、電源端子と接地端子の間で、抵抗R10と第2NチャネルMOSトランジスタM3とが直列接続されてなり、第2NチャネルMOSトランジスタM3のゲート端子Gが、直列接続点P1に接続され、直列接続点P2から出力が取り出される入力インターフェイス回路I10とする。

(もっと読む)

単位回路および電子回路

【課題】出力回路における各トランジスタのゲート・ソース間に印加される電圧を制限するための構成や単位回路へ入力される制御信号の振幅を小さくするための構成を簡素化する。

【解決手段】単位回路Jは、電源線101と接地線103との間に直列に接続された第1のPチャネルトランジスタ、第2のPチャネルトランジスタ、第1のNチャネルトランジスタ、および第2のNチャネルトランジスタとを備える。そして、第1のPチャネルトランジスタがオン状態のときにその電位がVDDとなり、第1のPチャネルトランジスタがオフ状態のときにその電位がVREF+Vtp2となる第1出力信号V1を第1出力端子から出力し、第2のNチャネルトランジスタがオン状態のときにその電位がGNDとなり、第2のNチャネルトランジスタがオフ状態のときにその電位がVREF−Vtn1となる第2出力信号V2を第2出力端子から出力する。

(もっと読む)

レベルシフタ、集積回路、システム、およびレベルシフタの動作方法

【課題】 レベルシフタ、集積回路、システムおよびレベルシフタの動作方法を提供する。

【解決手段】 第1電圧状態から第2電圧状態への第1状態遷移を含む入力電圧信号を受けるように構成された入力端、第3電圧状態から入力電圧信号の第1状態遷移に対応した第2電圧状態への第2状態遷移を有する出力電圧信号を出力するように構成された出力端、及び入力端と出力端の間に結合され、第1トランジスタと第2トランジスタを含み、第1電圧状態と第2電圧状態の電圧レベルの約平均値に対応した時間からほぼ直ちに、第2電圧状態がトランジスタのゲートに実質的に印加されることがなくなり、第1トランジスタを実質的にオフにするドライバ段を含むレベルシフタ。

(もっと読む)

半導体装置

【課題】出力バッファの出力電流が一定の範囲内に収まるように制御できる半導体装置を提供する。

【解決手段】出力バッファ1と、出力バッファと直列に接続された電流制御トランジスタM0と、電流制御トランジスタを介して出力される出力電流をモニタして電流制御トランジスタのオン抵抗を制御する出力電流制御回路2と、を備える。温度や電源電圧の変動等により出力バッファ自体のオン抵抗が変動したとしても、出力バッファの出力電流は、電流制御トランジスタにより決まり、電流制御トランジスタに流れる電流は出力電流制御回路によって一定の範囲内に収まるように制御される。出力バッファ自体の高速なスイッチング動作が損なわれることもない。

(もっと読む)

高周波スイッチ及び受信回路

【課題】簡単な構成でセルフミキシング信号の発生を低減する高周波スイッチ及びこれを用いた受信回路を提供する。

【解決手段】ゲート端子が入力端子側に接続され、ドレイン端子が出力端子側に接続され、ソースが接地された電界効果トランジスタと、前記電界効果トランジスタのゲート端子側に接続されるゲートバイアス電圧調整手段とドレイン端子側に接続されるドレインバイアス電圧調整手段の少なくともいずれか一方を備え、前記ゲート端子と入力端子との間及び前記ドレイン端子と出力端子との間の少なくともいずれか一方に整合回路を備え、導通状態における反射特性と前記遮断状態における反射特性とが略等しくなるように、スイッチを構成している。

(もっと読む)

バッファ回路

【課題】低電圧と高電圧とを相反する論理信号として出力し、前記高電圧として、異なる2以上の電圧を出力可能であって、安定して動作するバッファ回路。

【解決手段】論理制御回路と、第1の高電圧VDDLを与える電源と出力端子との間に設けられ、ゲートに前記論理制御回路から出力された第1の高電圧VDDLレベルの制御信号が入力され、バックゲートに第1の高電圧VDDLが与えられた第1のMOSトランジスタM9と、第2の高電圧VDDHを与える電源と出力端子との間に設けられ、ゲートに論理制御回路から出力された第2の高電圧VDDHレベルの制御信号が入力され、バックゲートに第2の高電圧VDDLが与えられた第2のMOSトランジスタM11と、第1のMOSトランジスタM9と出力端子との間に設けられ、第2の高電圧VDDLレベルの制御信号によりオンオフが制御される第1のスイッチ回路SW1と、を備えるバッファ回路。

(もっと読む)

半導体装置及びそのデータ出力方法

【課題】本発明は、より安定的なデータ出力動作を実現する半導体装置及びそのデータ出力方法を提供する。

【解決手段】本発明の半導体装置は、イネーブル信号とデータの入力を受けてプルアップソース信号とプルダウンソース信号を生成し、前記プルアップソース信号又は前記プルダウンソース信号の生成タイミングを遅延させる駆動制御部;前記プルアップソース信号と前記プルダウンソース信号を駆動して駆動データを生成するドライバ;及び前記ドライバの出力端に接続され、可変的な抵抗値を有するPOD(Pseudo Open Drain)インピーダンス制御部;を含む。

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

ドライバ回路

【課題】出力信号の立ち下がりのスロープ特性をその場で可変できる機能を有するドライバ回路を提供する。

【解決手段】入力信号TXDを受け、駆動出力ノードN1、N2から駆動信号V1、V2を出力する駆動制御回路11、12と、駆動信号V1、V2を受けて駆動されるMOSトランジスタM7、M8を有し、差動出力信号Vdiffを外部負荷に送出する出力バッファ回路13と、駆動制御回路11、12に付加され、入力信号TXDを受け、該入力信号の論理レベルが所定の方向に変化した時にMOSトランジスタM7、M8がオン状態からオフ状態に変化する動作の開始時間を短縮する動作開始加速回路14、15と、動作開始加速回路14、15に付加され、選択信号Vselに応じてMOSトランジスタM7、M8がオン状態からオフ状態に変化する動作の終了時間を可変する動作終了可変回路16、17と、を具備する。

(もっと読む)

半導体集積回路

【課題】差動アンプ回路の出力信号の出力をより正確に制御することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第4のMOSトランジスタと第5のMOSトランジスタとの間の接点の第1の電圧に応じた信号とイネーブル信号とが入力され、イネーブル信号が第1のレベルであり且つ第1の電圧が規定電圧以上の場合に差動アンプ回路の出力信号を出力端子に出力するための第1の信号を出力し、イネーブル信号が第2のレベルまたは第1の電圧が規定電圧未満の場合に第2の信号を出力する演算回路と、差動アンプ回路の出力信号と演算回路が出力した信号とが入力され、第1の信号が入力された場合には、出力信号を出力端子に出力し、第2の信号が入力された場合には、出力端子へ或る論理に固定した信号を出力する出力バッファ回路と、を備える。

(もっと読む)

半導体装置

【課題】Pチャンネル型MOSトランジスタをOFFさせる時に、駆動信号生成回路内のプルアップトランジスタと他の素子に流れる貫通電流を抑制できる半導体装置を提供する。

【解決手段】本実施形態の半導体装置は、従来の半導体装置のプルアップトランジスタ20に代えて、NAND素子7を設けた。その結果、プルアップトランジスタ20を排除したことから、プルアップトランジスタ20に起因する従来の半導体装置において課題であった、Pチャンネル型MOSトランジスタ1のOFF時に駆動信号生成回路内のプルアップトランジスタ20と他の論理素子とに生じる貫通電流を抑制できる。

(もっと読む)

61 - 80 / 232

[ Back to top ]