Fターム[5J056EE15]の内容

Fターム[5J056EE15]に分類される特許

61 - 80 / 261

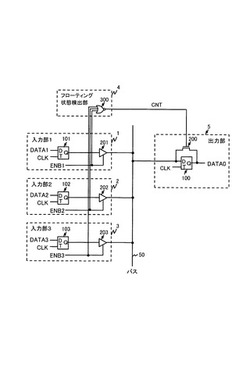

バス回路

【課題】バス面積を削減し、バス配線容量の増加を抑え、バスのフローティング状態を回避する際の消費電力を低減するバス回路を提供すること。

【解決手段】入力信号と制御信号がそれぞれ入力される複数の入力部と、複数の入力部の出力を互いに接続したバスと、バスからのバス信号を入力として信号を保持するラッチ回路を有する出力部とを備えるバス回路である。バス回路は、バスがフローティング状態となる場合に、出力部のラッチ回路に保持された信号をバスに出力する。

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】半導体装置側において自動的にキャリブレーション動作を行う。

【解決手段】出力バッファ71のインピーダンスを調整するキャリブレーション回路100と、オートリフレッシュコマンドARが所定回数発行されたことに応答してキャリブレーション回路100を活性化させるキャリブレーション起動回路200とを備える。本発明によれば、コントローラ側からキャリブレーションコマンドを発行することなく、半導体装置側にて自動的にキャリブレーション動作を行うことが可能となる。しかも、オートリフレッシュコマンドARが所定回数発行されたことに応答してキャリブレーション動作を行っていることから、定期的なキャリブレーション動作が確保されるとともに、キャリブレーション動作中にコントローラからリード動作やライト動作を要求されることもない。

(もっと読む)

半導体装置及び半導体装置の電源制御方法

【課題】1つの回路ブロックに対して設けた複数の電源スイッチを順次オンさせていく構成において、スイッチオンのタイミングを適切に制御可能な半導体装置を提供する。

【解決手段】半導体装置は、内部回路と、内部回路へ電流を供給する複数の並列な経路にそれぞれ設けられ、導通状態又は非導通状態に制御される複数の電源スイッチと、内部回路への電源を遮断する指示又は電源を供給する指示を行なう命令部と、内部回路に電源スイッチを介して供給される電流が定常状態であるか否かを検知して検知結果を出力する変動検知部と、命令部の電源供給指示に応答して、複数の電源スイッチを順次導通状態にして内部回路への電流供給量を増やしていく際に、複数の電源スイッチを導通させるタイミングを検知結果に応じて制御する論理回路とを含む。

(もっと読む)

供給ノイズおよび終端ノイズの低減方法およびシステム

【課題】 SSNに関連する問題を軽減するシステムおよび方法を提供すること。

【解決手段】 シングルエンドの通信チャネルを介して第1の集積回路(IC)が第2のICと通信する通信システムを開示する。双方向基準チャネルは、第1のICおよび第2のIC間に延在し、両エンドで終端される。基準チャネルの各エンドにおける終端インピーダンスは、信号を異なる方向に通信するための異なるモードをサポートする。基準チャネルの終端インピーダンスは、それぞれの信号方向に最適化されることができる。

(もっと読む)

半導体集積回路

【課題】PKGの設計期間を遅延させることなくクロストーク耐性を向上させることが可能な半導体集積回路を提供する。

【解決手段】複数の信号配線を有するChip20において、一の信号配線と前記一の信号配線に隣接する一方の隣接信号配線と前記一の信号配線に隣接する他方の隣接信号配線との間で生じるクロストークの発生量を抑制するための補正係数31と、前記一の信号配線に送出される一の信号、前記一方の隣接信号配線に送出される一方の隣接信号、および前記他方の隣接信号配線に送出される他方の隣接信号の組み合わせパターンと、に基づいて、前記一の信号のスルーレートの低減度合を示す補正量を演算する補正量演算部42a〜42cと、前記補正量に基づいて、前記一の信号のスルーレートを調整するドライバ41a〜41cと、を備える。

(もっと読む)

液晶表示装置及び電子機器

【課題】 一導電型のTFTのみを用いて回路を構成することにより工程削減が

可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提

供する。

【解決手段】 出力ノードに接続されているTFT203のゲート−ソース間に

容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態

とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT20

3のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い

電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることな

く、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

半導体装置

【課題】出力端子と単位バッファとの間の寄生抵抗に起因するインピーダンス誤差を低減する。

【解決手段】出力端子DQと、単位バッファ111〜11nと、単位バッファ111〜11nと出力端子DQとをそれぞれ接続する複数の出力配線経路とを備える。各出力配線経路は、それぞれ対応する単位バッファに個別に割り当てられた個別出力配線部161P〜16nP,161N〜16nNを有しており、これら出力配線経路に対応する単位バッファは、該出力配線経路によって共有された共通出力配線部であって、個別出力配線部よりも抵抗値の高い共通出力配線部を介することなく出力端子DQに接続されている。これにより、出力端子DQと単位バッファ111〜11nとの間の寄生抵抗によるインピーダンス誤差が抑制される。

(もっと読む)

入力インターフェース回路

【課題】有効なセットアップ特性及びホールド特性を良好に確保することが可能な入力インターフェース回路を提供すること。

【解決手段】本発明に係る入力インターフェース回路100は、データが外部入力される信号端子に接続される入力初段回路と、外部入力されるクロックと、入力初段回路に含まれるラッチ回路3、4へのラッチタイミング信号とを同位相に調整する位相調整回路6と、を備える。位相調整回路6は、クロックと当該クロックから擬似する擬似遅延回路の出力との比較結果に基づいてクロックツリー回路7を通過してラッチ回路3、4へと供給されるラッチタイミング信号の遅延時間を調整する。

(もっと読む)

半導体装置

【課題】複数の出力回路の出力インピーダンスのバラツキを抑える。

【解決手段】半導体装置であって、複数の出力回路と、前記複数の出力回路の出力インピーダンスを基準値に設定するためのキャリブレーション信号を生成するキャリブレーション回路とを有する。前記複数の出力回路は、それぞれ、前記キャリブレーション信号を補正する補正回路と、その出力インピーダンスを前記補正回路で補正された前記キャリブレーション信号に応じた値にする出力バッファとを有する。

(もっと読む)

半導体集積回路、半導体記憶装置、及びインピーダンス調整方法

【課題】自律型インピーダンス調整回路の消費電力を低減する。

【解決手段】本発明による半導体集積回路(100)は、レプリカドライバ(P40、N40)及び出力ドライバ(20)の駆動能力を変更するために逐次出力されるコンパレータ(P10、N10)の出力(カウントデータ)に応じて、ドライバの駆動能力の変更を一時的に停止する。

(もっと読む)

出力ドライバ、出力ドライバを含むメモリ、メモリコントローラ及びメモリシステム

【課題】プリアンブルに続く最初のハイレベル又はローレベルの区間の長さを、その後のクロッキング部分のハイレベル又はローレベルの区間の長さに一致させる。

【解決手段】 出力ドライバは、第1の電源と出力端子との間に接続される第1のドライバと、第2の電源と出力端子との間に接続される第2のドライバとを有する。第1のドライバ及び第2のドライバの一方は、互いに並列接続された2つの駆動部を備える。これら2つの駆動部の各々と、第1のドライバ及び第2のドライバの他方とは、それぞれ独立した入力信号に応じて動作する。

(もっと読む)

信号伝送装置

【課題】送信端の出力におけるバイアス低下を防ぐ。

【解決手段】入力信号を正相入力端子1、逆相入力端子2で共通に入力し、互いに同相の出力信号を伝送路に出力する第1および第2の送信部と、第1および第2の送信部の出力端間を接続する容量素子14、15と、伝送路とインピーダンスマッチングすると共に、第2の送信部の直流負荷として接続される抵抗素子12、13と、を備え、第1の送信部は、伝送路を介した受信側の入力段の入力抵抗21、22を直流負荷として接続する。ここで、第1の送信部は、差動対となるNMOSトランジスタ8、9、およびこの差動対に電流を供給する定電流源6から構成され、第2の送信部は、差動対となるNMOSトランジスタ10、11、およびこの差動対に電流を供給する定電流源7から構成される。

(もっと読む)

2つのマスタと1つ以上のスレーブとの間の信号伝送のための電気回路

2つのマスタ(11、12)と1つ以上のスレーブ(13、14)との間の信号伝送のための電気回路(10)が記載される。2つのマスタ(11、12)と1つ以上のスレーブ(13、14)とは、バスシステム(15)を介して互いに接続される。2つのマスタ(11、12)によって、1つ以上のスレーブ(13、14)により受信されうるマスタデータ信号(MO)が少なくとも1つずつ生成可能である。各マスタデータ信号(MO)が印加される2つのマスタ(11、12)の出力口には、三状態ゲート(16)が1つずつ存在する。三状態ゲート(16)は、閉回路又は開回路として作動可能である。三状態ゲート(16)は、2つのマスタの一方(11)に割り当てられた三状態ゲート(1611)が閉回路として作動し、2つのマスタの他方(12)に割り当てられた三状態ゲート(1612)が開回路として作動するように、駆動される。 (もっと読む)

送信回路

【課題】プリエンファシスと非プリエンファシスの2状態のデータを出力する送信回路において、データ変化点の波形のエッジに起因する電源変動、及びプリエンファシスと非プリエンファシスに起因する電源変動を抑制する。

【解決手段】図Aに示す第1回路、図Bに示す第2回路からなる。第1回路の第1回路の入力回路601g〜jには第1信号601n,601qと第1プリエンファシス信号601p,601rが入力される。第2回路の入力回路602g〜jには第2信号602n,602qと第2プリエンファシス信号602p,602rが入力される。第2信号は第1信号が変化するときは変化せずに、第1信号が変化しない時は変化する。第1回路の出力回路601a,601bと第2回路の出力回路602a,602bのどちらかがプリエンファシス状態となるので、出力回路全体で流れる電流値は一定となる。

(もっと読む)

半導体集積回路

【課題】電源線のレイアウト面積を広げることなく、コア回路とバイアス供給回路との間

の電圧降下を抑え、かつ、コア回路間の高速信号ノードを短縮できるようにする。

【解決手段】Si基板11にトランジスタQ及び抵抗素子Rを有して高電位側の電源線と

低電位側の配線D1とバイアス供給用の配線D2とに接続されてトランジスタ動作をする

コア回路1と、Si基板11に設けられてコア回路1にバイアスを供給するバイアス供給

回路とを備え、コア回路1の中の定電流源用のトランジスタQに、その一端が接続された

抵抗素子Rの他端がバイアス供給用の配線D2に接続され、この配線D2が接続された抵

抗素子Rの他端がコンタクトホール35を介してバイアス供給用の配線D2よりも上層の

低電位側の配線D1に接続されるものである。

(もっと読む)

半導体記憶装置

【課題】Duty誤差を低減でき、高速なデータ入出力に有利な半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、電気的に回路閾値を調節可能な第1インバータINV1−1を備える入力バッファ12と、前記第1インバータと共通の回路構成の第2インバータINV1−2を備え、前記第2インバータの入力と出力とが短絡されることにより前記第1インバータの回路閾値を検出する回路閾値モニタ13と、前記回路閾値モニタが検出した回路閾値に対応するパラメータ値を記憶するメモリ11−2と、前記第1インバータに与えられる前記パラメータ値を、前記メモリから読み出すデータ読み出し回路15とを具備する。

(もっと読む)

ターミネーション回路及びそれを備えるインピーダンス整合装置

【課題】回路面積を増加させることなく、多様なターミネーションインピーダンス値を提供するターミネーション回路及びこれを備えるインピーダンス整合装置を提供すること。

【解決手段】本発明に係るインピーダンス整合装置は、インピーダンス値を較正するためのインピーダンス調整コードを生成するキャリブレーション回路310と、インピーダンス値設定情報に応じて前記インピーダンス調整コードを変更し、変更された前記インピーダンス調整コードを出力するコード変更部320と、変更された前記インピーダンス調整コードに応じて決定されるインピーダンス値でインタフェースノードをターミネーションするターミネーションインピーダンス部330、340と、を備える。

(もっと読む)

半導体集積回路装置及び電源システム

【課題】パワースイッチをオンとする際に発生する電源ノイズが許容値を超えないようにし、かつ、内部回路に与える電源電圧の立ち上がり時間を短縮することができるようにした半導体集積回路装置を提供する。

【解決手段】信号処理回路15に対する電源投入時に、パワースイッチをなすNMOSトランジスタ21−1〜21−4、22−1〜22−4のうち、まず、NMOSトランジスタ21−1〜21−4をオンとする。その後、信号処理回路15が出力端子20−1に出力する出力信号OUTの電圧変化を検出し、電源ノイズがピーク値に達したことが検出されると、NMOSトランジスタ22−1〜22−4をオンとする。

(もっと読む)

高速多重化回路

【課題】高速動作時の出力波形品質を改善する。

【解決手段】高速多重化回路は、データ信号列(D1P,D1N),(D2P,D2N)毎に設けられ、入力されたデータ信号列を共通に接続された信号出力端子に選択的に出力する第1のトランジスタQ1P,Q1N,Q2P,Q2Nと、トランジスタQ1P,Q1Nから構成される差動対またはトランジスタQ2P,Q2Nから構成される差動対のいずれか一方をクロック信号CK1,CK2に応じてオンにする第2のトランジスタQ3,Q4と、トランジスタQ1P,Q1N,Q2P,Q2N,Q3,Q4にコレクタ電流を流す電流源となる第3のトランジスタQ6,Q7と、第3のトランジスタQ6,Q7のコレクタとエミッタ側の電源電圧VEEとの間に挿入されたコンデンサC1とを備える。

(もっと読む)

スイッチト出力段のための短絡保護

デバイスのダメージを引き起こしうる短絡条件における過度の出力電流からスイッチング出力段を保護するための、スイッチ型出力段における短絡保護が説明される。この目的を達成するための設計技術は、ドレイン電圧を実質的に等しくするための回路と組み合わせて、スケールされたトランジスタをスイッチングトランジスタと並列に置くことによって、それらスイッチングトランジスタにおける電流を測定することを含む。短絡保護のための様々な技術は、(a)トランジスタと演算増幅器とを組み合わせて使用すること、(b)演算増幅器の代わりに単一のトランジスタを使用すること、(c)過電流検出信号を生成するための回路を使用すること、(d)出力電流を低減するために、ドライバに過電流検出信号を提供すること、(e)出力電流をフィードバック調整するためにインバータを使用すること、(f)通常動作中に電流調整器をバイパスするためにスイッチを使用すること、および(g)過電流状態において、このスイッチを自動的に開くこと、を具備する。  (もっと読む)

(もっと読む)

61 - 80 / 261

[ Back to top ]