Fターム[5J056EE15]の内容

Fターム[5J056EE15]に分類される特許

21 - 40 / 261

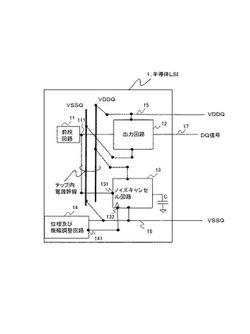

半導体装置

【課題】出力回路のSSN(Simultaneous Switching Noise)の振動ノイズの低減を可能とする半導体装置の提供。

【解決手段】第1及び第2の電源線と、前記第1の電源線VDDQと前記第2の電源線VSSQとの間に配置された出力回路12と、前記第1の電源線と前記第2の電源線との間に配置されたノイズキャンセル回路13とを備え、前記ノイズキャンセル回路13は、前記出力回路の前記出力ノードの論理レベルへの切り替え時に発生する所定の周期で指数関数的に減衰振動する電源ノイズに対して、前記電源に、前記振動から半周期分遅れ、前記振動と逆向きに減衰振動する電源ノイズを発生し、互いに打ち消し合わせる。

(もっと読む)

出力バッファ回路

【課題】 誘導性負荷を駆動する出力バッファ回路の電力損失を低減する。

【解決手段】 誘導性負荷2から出力バッファ回路100に電流が流入している場合、スルーレート制御部140は、出力バッファ回路100の出力信号VOUTの立ち上がり過程において低いスルーレートから高いスルーレートへ変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において高いスルーレートから低いスルーレートに変化させる制御を行う。また、出力バッファ回路100から誘導性負荷2に電流が流出している場合に、スルーレート制御部140は、出力信号VOUTの立ち上がり過程において高いスルーレートから低いスルーレートに変化させる制御を行うとともに、出力信号VOUTの立ち下がり過程において低いスルーレートから高いスルーレートに変化させる制御を行う。

(もっと読む)

可変インピーダンス装置及び無線システム

【課題】 選択する容量の数に関わらずにそのオン抵抗を一定に保つことができる可変インピーダンス装置及びそれを用いた無線システムを提供する。

【解決手段】 一対の入出力端子101、102と、一対の入出力端子間に並列に接続された複数の回路ブロックBL1〜BL4と、を備え、回路ブロックは、一対の入出力端子の一方に一端が接続された容量性回路要素C1〜C4と、容量性回路要素の他端と一対の入出力端子の他方との間に互い並列に接続された回路ブロックの数以上の数のスイッチ素子SW1−1〜SW4−4を備えるスイッチ回路SW1〜SW4と、を備える。

(もっと読む)

タイミング制御回路、タイミング制御方法、及びシステム

【課題】タイミングマージンの減少を抑制すること。

【解決手段】システム装置21に形成された制御回路36は、可変容量35の容量値を制御し、トレーニング回路45にタイミングトレーニングを実行させる。トレーニング回路45は、メモリ12がデータDQに基づく正常なデータを書き込むことができる設定値の最大値と最小値を出力する。制御回路36は、その最大値及び最小値に基づいてデータDQのウインドウ幅を算出し、より大きなウインドウ幅に対応する容量値を可変容量35に設定する。

(もっと読む)

プリエンファシス回路及びこれを備えた差動電流信号伝送システム

【課題】プリエンファシス回路及びこれを備えた差動電流信号伝送システムを提供する。

【解決手段】本発明はプリエンファシス回路に関し、より詳細にはプリエンファシス回路を動作させるために必要なスイッチングトランジスタの数を減らして寄生抵抗及び寄生キャパシタを減少させ、それぞれのスイッチングトランジスタを制御するそれぞれのプリエンファシス制御信号を供給することによって望まない電流の発生を防止できるプリエンファシス回路及びこれを備えた差動電流信号伝送システムに関する。

(もっと読む)

クロックバッファ回路及びクロック分配回路

【課題】クロック源の消費電力を増大させることなく、動作クロック周波数に応じて駆動能力を変化させることにより消費電力低減可能なクロックバッファ回路を提供すること。

【解決手段】クロック信号を伝達するバッファ部102と、クロック信号の参照クロック信号に対する逓倍数をカウントし、バッファ部102に対して逓倍数に基づいたイネーブル信号を出力する駆動能力切替部101と、を備え、バッファ部102は、当該バッファ部102の入力に接続された入力インバータ7と、イネーブル信号によりオンオフが可能であって、それぞれの出力が当該バッファ部の出力に共通に接続された複数の出力インバータ13〜28と、を備え、入力インバータ7が1個のCMOSインバータからなるクロックバッファ回路。

(もっと読む)

半導体集積回路

【課題】

CMOS回路に中間電圧の入力信号が長時間連続して入力された場合にも貫通電流の発生を短時間にとどめることができる半導体集積回路を提供する。

【解決手段】

本発明の一実施態様に係る半導体集積回路は、入力端子と、出力端子と、ゲートが前記入力端子に接続されソースが高電位電源配線に接続された第1PMOSトランジスタ及びゲートが前記入力端子に接続されソースが低電位電源配線に接続された第1NMOSトランジスタを含み、当該第1PMOSトランジスタと当該第1NMOSトランジスタとが同時に導通しないように構成された第1CMOS回路と、入力端が前記第1CMOS回路に接続され出力端が前記出力端子に接続された第2CMOS回路と、この第2CMOS回路の出力端とと高電位電源配線及び高電位電源配線との間にそれぞれ配置された第2PMOSトランジスタと第2NMOSトランジスタと、を備える。

(もっと読む)

ドライバ回路およびそれを用いた試験装置

【課題】ポジティブエッジの波形、ネガティブエッジの波形の少なくとも一方を調節可能なドライバ回路を提供する。

【解決手段】分岐回路10は、送信すべき入力信号SINを複数の経路12に分岐する。各タイミング調節回路20は、それぞれが対応する経路に分岐された送信すべき信号Saのポジティブエッジおよびネガティブエッジの少なくとも一方に遅延を与える。合成出力回路30は、複数のタイミング調節回路20の出力信号Sbを合成し、合成された信号SOUTを伝送線路3に出力する。

(もっと読む)

半導体装置

【課題】電源分離領域内の配線密度を低下させる。

【解決手段】動作モードに応じて電源電圧が供給される電源線VVDDと、常に電源電圧が供給される電源線VDDと、通常モードで電源線VVDDを電源線VDDに接続するか、またはスリープモードで電源線VVDDを接地電位とするか、を切り替える電源切替回路(104、111、110が相当)と、電源線VVDDから電源供給されスリープモードでは動作を停止する第1回路ブロック101と、電源線VDDからの電源供給によって常に動作可能とする第2回路ブロック103と、電源線VVDDの電位が接地電位近傍にあるか否かにそれぞれ応じて、第2回路ブロック103の入力端をハイレベルにするか、第1回路ブロック101の出力信号を第2回路ブロック103に伝達可能とするか、を制御する入力制御回路(114、118が相当)と、を備える。

(もっと読む)

レベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置

【課題】向上された信頼性を有するレベル変換器、それを含むシステムオンチップ、及びそれを含むマルチメディア装置が提供される。

【解決手段】本発明のレベル変換器は、入力ノードを通じて受信される第1電圧ドメインの入力クロックに応じて第2電圧ドメインの出力クロックを発生する第1及び第2電圧変換回路を含み、第1及び第2電圧変換回路は同一の構造を有し、入力ノード及び出力ノードの間に並列に連結される。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】デエンファシス機能を有する出力バッファ回路において、デエンファシス設定を行うと、デエンファシス非設定時には発生しなかったACコモンモードノイズの発生や、デエンファシス強度の低下が起きる。

【解決手段】電流補正回路により、デエンファシス機能を実現するための2つのバッファ回路に供給する電流を補正する。この補正回路により、デエンファシス設定時のACコモンモードノイズの発生を抑制し、デエンファシス強度の低下を防止する。

(もっと読む)

半導体装置及び電子機器

【課題】一導電型のTFTのみを用いて回路を構成することにより工程削減が可能であり、かつ出力信号の電圧振幅が正常に得られる表示装置の駆動回路を提供する。

【解決手段】出力ノードに接続されているTFT203のゲート−ソース間に容量205を設け、TFT201、202からなる回路は、ノードαを浮遊状態とする機能を有する。ノードαが浮遊状態のとき、容量205によるTFT203のゲート−ソース間の容量結合を利用してノードαの電位をVDDよりも高い電位とし、これによって、TFTのしきい値に起因する振幅減衰が生ずることなく、正常にVDD−GND間の振幅を持った出力信号を得ることが出来る。

(もっと読む)

半導体デバイス回路

【課題】MTCMOS回路を用いた半導体デバイス回路において、アクセススピードを損なわず、スタンバイ電流が少なく、スタンバイ状態からの復帰が早い半導体デバイス回路を提供する。

【解決手段】第1のPMOSFETと第1のNMOSFETとを含む機能回路を備えた半導体デバイス回路において、アクティブモード時に第1のPMOSFETを電源電圧源に接続し、スタンバイモード時に電源電圧源に接続しないように制御する第2のPMOSFETと、アクティブモード時に第1のNMOSFETを接地側電圧源に接続し、スタンバイモード時に接地側電圧源に接続しないように制御する第2のNMOSFETと、電源電圧源に接続されかつ第1のPMOSFETに並列に接続されその出力信号を保持する第3のPMOSFETと、接地側電圧源に接続されかつ第1のNMOSFETに並列に接続されその出力信号を保持する第3のNMOSFETとを備えた。

(もっと読む)

同期回路

【課題】小面積で広帯域特性及び低位相雑音特性を得ることが可能な同期回路を提供する。

【解決手段】位相検出器11は、参照信号と帰還信号との位相差を検出する。電圧生成器12,13は、位相検出器の出力信号に基づき電圧を発生する。パルス発生器16は、参照信号に基づきパルス信号を生成する。電圧制御発振器14は、パルス信号に同期して、発振信号を発振する。分周器15は、電圧制御発振器からの信号を分周し、帰還信号を生成する。電圧制御発振器14は、電圧発生回路から供給される電圧レベルをシフトするレベルシフト回路14cと、電圧発生回路からの電圧とレベルシフト回路からのレベルシフトされた電圧により駆動される複数のインバータ回路14a、14bからなるリング発振器とにより構成され、インバータ回路の1つにパルス信号が供給される。

(もっと読む)

出力バッファ回路

【課題】プリエンファシス機能を有する出力バッファ回路の出力インピーダンスを、調整可能なプリエンファシス量とプリエンファシスタップ数、及び動作タイミングに依らず一定で、伝送線路の特性インピーダンスと整合して出力バッファの出力端子で再反射することなく、高速動作可能な出力バッファ回路を提供する。

【解決手段】インバータ1〜3と、一定の時間遅延させる遅延回路1〜3と、バッファ1〜3とを備え、伝送径路に論理信号を送信し、伝送径路の信号減衰量に応じて、送信側で4種以上の信号電圧を有する波形を生成する機能を有する出力バッファ回路で、プリエンファシス量を可変とし、バッファのオン抵抗Rsを一定とする。バッファの前段にセクレタ回路1〜3を有し、インバータは、セレクタ論理によりバッファに入力する信号を選択可能で、データ信号を反転し、セレクタ論理のセレクト信号により、プリエンファシス量とプリエンファシスタップ数を調整する。

(もっと読む)

半導体装置

【課題】入力信号に基づいて位相の一致した相補の出力信号を生成する。

【解決手段】入力信号INTを受けて反転信号INBを出力するインバータ11と、反転信号INBを受けて内部信号INTTを出力するインバータ12と、反転信号INBを電源とし、入力信号INTを受けて内部信号INBBを出力するインバータ21と、を備える。本発明によれば、一方の信号パス上の信号を他方の信号パスに含まれるインバータの電源として用いていることから、調整用の容量や抵抗を付加することなく、一対の出力信号の位相を正確に一致させることが可能となる。

(もっと読む)

差動出力回路

【課題】出力信号の波形品質を改善する。

【解決手段】制御部(102)は、スイッチング素子(SW1,SW4)がオン状態であるとともにスイッチング素子(SW2,SW3)がオフ状態である第1の出力状態と、スイッチング素子(SW1,SW4)がオフ状態であるとともにスイッチング素子(SW2,SW3)がオン状態である第2の出力状態とを切り替える。また、制御部(102)は、第1の出力状態から第2の出力状態に切り替える場合には、スイッチング素子(SW2,SW3)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW1,SW4)をオン状態からオフ状態に切り替える。さらに、制御部(102)は、第2の出力状態から第1の出力状態に切り替える場合には、スイッチング素子(SW1,SW4)をオフ状態からオン状態に切り替えてから可変遅延時間が経過した後に、スイッチング素子(SW2,SW3)をオン状態からオフ状態に切り替える。

(もっと読む)

半導体装置及び制御方法

【課題】メモリの出力バッファの平均電流値を低減し、消費電流を抑制すること。

【解決手段】本発明に係る半導体装置は、メモリリードアドレスDの連続性を判定し、判定結果Hを出力するアドレス連続性判定回路23と、判定結果Hに基づいて、メモリリードアドレスDに対応するリードデータを出力するメモリの出力バッファ22の駆動能力を制御する駆動能力切り替え制御回路24と、CPUの要求リードアドレスAに対応するリードデータが当該CPUへ到達するまでの期間に、CPU要求リードアドレスAに連続する予想アドレスを生成するアドレス生成部12と、予想アドレスに対応するリードデータを格納するプリロードバッファ14を備える。

(もっと読む)

差動増幅器

【課題】負荷側に出力を電流で受け渡すカレントミラー回路を備える差動増幅器の動作を高速化する。

【解決手段】差動増幅器を構成し、差動増幅器に対する2つの入力の内のそれぞれ1つが与えられる各トランジスタの端子の内で、差動増幅器の出力点となりうるそれぞれの端子の間に接続される回路素子を備える差動増幅器は、カレントミラー回路においてモニタ電流が流れるトランジスタに接続されるとともに、カレントミラー回路においてコピー電流が流れる第1のトランジスタと、前記出力が受け渡される負荷としての抵抗との間に接続される前記2つの入力のうちいずれか1つが与えられるトランジスタへの入力がLの時にオフとなる第2のトランジスタと、第1のトランジスタと第2のトランジスタとの接続点とアースとの間に接続される電流源とをさらに備えることにより、上記課題の解決を図る。

(もっと読む)

半導体装置及びこれを搭載する回路基板

【課題】出力バッファのインピーダンスを調整するためのキャリブレーション動作を高精度に行う。

【解決手段】キャリブレーション端子ZQに接続されたレプリカバッファ110と、端子ZQの電位と基準電位Vrefとの比較結果に応じてレプリカバッファ110のインピーダンスを変化させるインピーダンス調整回路180と、レプリカバッファ120とレプリカバッファ130の接続ノードAの電位と端子ZQの電位との比較結果に応じてレプリカバッファ130のインピーダンスを変化させるインピーダンス調整回路190とを備える。本発明によれば、レプリカバッファ110,130のいずれに対してもZQ端子の電位を基準としてインピーダンス調整が行われることから、一方のレプリカバッファの調整誤差が他方のレプリカバッファの調整誤差に重畳することがない。

(もっと読む)

21 - 40 / 261

[ Back to top ]