Fターム[5J056EE15]の内容

Fターム[5J056EE15]に分類される特許

101 - 120 / 261

電力調整装置およびLEDドライバ

【課題】制御信号を用いて電力を多段階制御する電子機器、および2段階制御する電子機器の何れにも適用可能でありながら、極力簡易な制御信号が与えられるだけで適切に電力を調整し得る電力調整装置を提供する。

【解決手段】第1状態または第2状態をとる制御信号を受付け、制御信号に基づいて、所定装置に供給される電力を調整するものであって、制御信号が第1状態から第2状態に遷移した場合、遷移時点から所定の判定時間が経過するまでに、制御信号が第1状態に戻ったかを判定する機能と、戻った場合には、第1方式によって電力を現状と異なる値に調整し、戻らなかった場合には、第2方式によって電力を現状と異なる値に調整する機能を備え、第1方式は、制御信号に基づき、電力を2段階以上に設定された各値の何れかに調整する方式であり、第2方式は、電力を所定値に調整する方式である電力調整装置とする。

(もっと読む)

レベルシフト回路

【課題】外的要因による誤動作を防止して確実な信号伝達を行うレベルシフト回路。

【解決手段】第1電圧レベルを第1電圧レベルとは異なる第2電圧レベルに変換するレベルシフト回路であって、第2電圧レベルの論理電圧状態をセットするセット信号を送信するセットレベル回路21と、第2電圧レベルの論理電圧状態をリセットするリセット信号を送信するリセットレベル回路22と、第2電圧レベルでセット信号及びリセット信号を検出するための基準値を設定する基準レベル回路C3とを有し、セットレベル回路とリセットレベル回路と基準レベル回路との各々は、それぞれコンデンサC1〜C3を介して第1電圧レベルから第2電圧レベルに信号を伝達する。

(もっと読む)

相互接続構造および論理回路装置

【課題】外部配線と複数の論理セルを含む論理セル群とを相互に接続する相互接続構造、および相互接続構造を有する論理回路装置に関し、論理のファンクション表現の柔軟性を低下させることなく配線リソースのオーバヘッドを低減させることを目的とする。

【解決手段】論理回路装置における相互接続部1が、外部配線と論理セル群2の入力線と相互接続関係を規定する接続規定手段を有し、論理セル群の複数の論理セルの中で対象となるファンクションを考慮して、論理のファンクション表現に関する柔軟性を保ちつつ、相互接続部の入力線の数が相互接続部の出力線の数より少ない構成、および、接続規定手段により規定される組み合わせ数が相互接続部の入出力の全ての組み合わせ数より少ない構成の少なくとも一方が実現されるように構成される。複数の論理回路装置のクラスタ化により形成されるクラスタ構造を有する論理回路装置も提供される。

(もっと読む)

半導体集積回路装置

【課題】I/O処理性能の向上と消費電力の低減またはコストの低減が実現可能な半導体集積回路装置を提供する。

【解決手段】例えば、複数の半導体チップCHIP0〜CHIPnが積層搭載され、互いのデータ送受信端子P_DIOが貫通ビアTSVを介してバス接続された半導体集積回路装置を設け、CHIP0〜CHIPnの内部コア回路の電源電圧のうち最も低い電源電圧を用いてこのバスを介したデータ送受信を行わせる。これに伴い、この最も低い電源電圧となるCHIPnの電源電圧端子P_VDDnを、貫通ビアTSVを介して他の半導体チップCHIP0,CHIP1のデータ送受信回路用の電源電圧端子P_VDDL0,P_VDDL1に接続する。

(もっと読む)

差動出力バッファ

【課題】 広範囲な電源電圧仕様に対して、安定した出力振幅およびその出力振幅の中心電圧を出力することができる差動出力バッファを提供する。

【解決手段】 ドレインが電源電圧VDDに接続されるとともにゲートに出力差動信号OUTP,OUTNの出力コモンモード(VOC)を規定する第1の基準信号VREF1が入力されるデプレッション型NMOSトランジスタ11と、ソース双方がデプレッション型NMOSトランジスタ11のソースに接続されるとともに各ゲートに各差動信号INN,INPが入力されるPMOSトランジスタ12,14と、各ゲートおよび各ドレインが各PMOSトランジスタ12,14の各ゲートおよび各ドレインにそれぞれ接続されるとともに各ゲートに各差動信号INN,INPが入力されるNMOSトランジスタ13,15と、NMOSトランジスタ13,15双方のドレインとグランドGNDとの間に接続されたNMOSトランジスタ16とを備えた。

(もっと読む)

半導体集積回路及びLSIシステム

【課題】CMOS論理回路を小さいスイッチで高速動作させることができ、サブスレッショルドリーク電流を効果的に低減可能な半導体集積回路及びLSIシステムを提供すること。

【解決手段】半導体集積回路は、CMOS論理回路と、CMOS論理回路の電圧供給源とCMOS論理回路の電源端の間に設けられた、第1のMOSFETを有するスイッチ回路と、第1のMOSFETと逆チャネルの第2のMOSFETと、第2のMOSFETのドレインに接続された第1の抵抗と、第1の抵抗及び第1のMOSFETのソースに接続された第2の抵抗と、を有するデジタルアナログ変換回路とを備える。第1のMOSFETのバックゲートと、第1の抵抗と第2の抵抗の接続点が接続される。また、第1のMOSFETのゲートに供給される制御信号と第2のMOSFETのゲートに供給される制御信号が共通である。

(もっと読む)

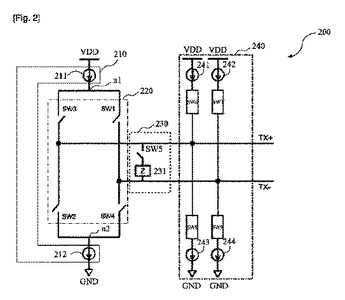

送信装置

【課題】スルーレートを改善することができる送信装置を提供する。

【解決手段】送信装置1は、データ変換回路11,駆動回路20,主出力バッファ回路31および副出力バッファ回路32を備える。駆動回路20は、EN信号が非有意値であるときにスイッチSW31,SW32,SW41,SW42,SW30及びSW40をオフ状態とし、EN信号が有意値であるときにスイッチSW30およびスイッチSW40をオン状態とし、DIN信号がHレベルであってEN信号が有意値であるときにスイッチSW31及びSW42をオン状態とするとともにスイッチSW32及びSW41をオフ状態とし、DIN信号がLレベルであってEN信号が有意値であるときにスイッチSW31及びSW42をオフ状態とするとともにスイッチSW32及びSW41をオン状態とする。

(もっと読む)

データ伝送回路、画像形成装置

【課題】データ同士のスキューを可及的に低減できるデータ伝送回路を提供する。

【解決手段】例えば複合機1の主電源がオンされると、或いは、画像形成動作を実施しない期間の或るタイミングで、当該複合機1のモードを、各差動ドライバ部205〜207のドライブ能力の設定処理を実施するキャリブレーションモードに設定するモード設定部46と、前記差動ドライバ205〜207のドライブ能力の段階を順番に切り替えていくドライブ能力設定部48と、前記ドライブ能力の各段階において、予め定められた補正用信号がパラシリ変換部201〜203から出力されるように送信制御回路200に指示を与え、前記補正用信号を前記シリパラ変換部307〜309で受信したタイミングを、受信制御回路300を用いて検出する検出部47とを備えた。

(もっと読む)

I2Cインタフェースを有するシステム及びその方法

【課題】本発明の目的は、I2Cインタフェースを有するシステムを提供することである。

【解決手段】本発明の第1の態様によると、マスター装置と前記マスター装置により制御されるスレーブ装置との間のインタフェースをとるI2Cインタフェースを有するシステムが提供される。前記マスター装置は第1のデータ・バスと接続され第1の駆動電圧で動作し、前記スレーブ装置は第2のデータ・バスと接続され第2の駆動電圧で動作し、前記システムは、それぞれ前記第1及び第2の駆動電圧の間のレベルシフト機能を有する第1及び第2の双方向デジタル入出力回路、及び前記第1及び第2の双方向デジタル入出力回路を制御するシーケンサ回路、を有し、前記シーケンサ回路は、前記第1及び第2の双方向デジタル入出力回路の出力に基づき、データの伝達方向を前記マスター装置から前記スレーブ装置へ、又は前記スレーブ装置から前記マスター装置へ切り替える。

(もっと読む)

ドライバ回路

【課題】高速なデータパターンの時のみ周波数特性を改善して、所望の振幅を得ることが可能な送信側ドライバ回路を提供する。

【解決手段】第1のプルアップ抵抗回路P41、第3のプルアップ抵抗回路P43、第1のプルダウン抵抗回路N41、第3のプルダウン抵抗回路N43の抵抗値を第1の制御信号(SDATAP、SDATAM、DEMPHPP、DEMPHMN、DEMPHPN、DEMPHMP)に応じて変化させ、第2のプルアップ抵抗回路P42、第4のプルアップ抵抗回路P44、第2のプルダウン抵抗回路N42、第4のプルダウン抵抗回路N44の抵抗値を第2の制御信号(EMPHPP、EMPHPMN、EMPHPN、EMPHMP)に応じて変化させる

(もっと読む)

電気的に画素化された発光素子

電気的に画素化された発光素子、電気的に画素化された発光素子を形成するための方法、電気的に画素化された発光素子を含むシステム、電気的に画素化された発光素子の使用方法。 (もっと読む)

半導体集積回路

【課題】CPUの動作に支障を来すこと無く、消費電力を削減することが可能な半導体集積回路を提供する。

【解決手段】CPU10と別に設けられた電源制御回路40は、半導体チップ1上に設けられたCPU10からの信号(例えばアイドル信号Si)を検出する。電源制御回路40は、この信号に応じて、CPU10に対してスイッチ素子30_1を制御して電源電圧Vpの供給を制御する。この制御により、CPU10の動作に支障をきたすことなく、効率よく電源制御が行える。

(もっと読む)

電流変動制御装置、半導体集積回路、電流変動制御方法および電流変動制御プログラム

【課題】面積を小さくでき、かつ、消費電流の変化を抑制して安定した動作を行う半導体集積回路の全体消費電流を制御する電流変動制御装置を提供する。

【解決手段】電流変動制御装置は、本来的用途に応じて設けられている複数の既存内部回路Bを選択的に活性化させて調整用の消費電流を生じさせる電流制御回路と、内部回路Aのリセット解除およびリセット投入を制御するリセット制御信号を出力するとともに電流制御回路に動作許可を与える動作許可信号を出力するリセット制御回路と、を備える。電流制御回路は、既存内部回路Bに活性化制御信号を出力し、内部回路Aのリセット解除前に既存内部回路Bを順次選択して活性化させることによりこれら既存内部回路Bによる調整用消費電流を徐々に上昇させ、内部回路Aのリセット解除時に既存内部回路Bの活性化を停止させる。

(もっと読む)

出力回路

【課題】より精度よく外部インピーダンスとの整合をとることができる半導体集積回路の出力回路を提供する。

【解決手段】出力回路は、トランジスタN00〜N7を含むトランジスタ回路が出力端子3に複数段並列に接続されてなり、各トランジスタ回路に含まれるトランジスタのゲートへの入力信号G0〜G7により出力インピーダンスの調整が可能な出力回路であって、複数段のトランジスタ回路に含まれる、少なくとも2段のトランジスタ回路のインピーダンスを互いに異ならせる。

(もっと読む)

差動電流駆動方式の送信部、差動電流駆動方式の受信部及び前記送信部と前記受信部を具備する差動電流駆動方式のインターフェースシステム

本発明は、伝送ラインに流れる電流の方向を調節することでデータを受信部に送信する差動電流駆動方式の送信部、差動電流駆動方式の送信部及び前記差動電流駆動方式の送信部と差動電流駆動方式の送信部を具備する差動電流駆動方式のインターフェースシステムに対して開示する。前記差動電流駆動方式の送信部は、電流源、電流方向選択ブロック及び平衡スイッチブロックを具備する。前記電流源は伝送ライン対に電流を供給するか、または前記伝送ライン対から流れる電流をシンクする。前記電流方向選択ブロックは、前記伝送ライン対のうちで一つの伝送ラインに前記電流源から流れる電流を伝達して、残り一つの伝送ラインに流れる電流を前記電流源に伝達する。平衡スイッチブロックは前記伝送ライン対を平衡状態に初期化する。  (もっと読む)

(もっと読む)

半導体装置及びこれを備えるデータ処理システム

【課題】チップ面積の大幅な増大をもたらすことなく、出力バッファのスルーレートを自動的に調整する。

【解決手段】インピーダンス調整信号ZQP,ZQNに基づいてインピーダンスを調整可能な出力バッファ100と、インピーダンス調整信号ZQP,ZQNに基づいて出力バッファ100のスルーレートを調整するスルーレート制御回路400とを備える。スルーレート制御回路400は、インピーダンス調整信号ZQP,ZQNが相対的に低いインピーダンスを指定している場合にはスルーレートを相対的に高く設定し、インピーダンス調整信号がZQP,ZQN相対的に高いインピーダンスを指定している場合にはスルーレートを相対的に低く設定する。これにより、スルーレートを測定するための専用回路が不要となる。

(もっと読む)

ヒューズ装置

【課題】切断したヒューズにグローバックが発生した場合にも、正確なヒューズデータを生成し得るヒューズ装置を提供する。

【解決手段】切断したグローバック検出用ヒューズf0の抵抗値と、第一の基準抵抗R0の抵抗値の差に基づく検出信号Xを生成するグローバック検出部11と、検出信号Xに基づいて抵抗値が変化する第二の基準抵抗TN9の抵抗値と、ヒューズデータ生成用ヒューズf1,f2,fnの抵抗値との比較結果をヒューズデータDAとして出力するヒューズ部13aとを備えた。

(もっと読む)

半導体集積回路

【課題】電源ノイズを抑制する。

【解決手段】電源電圧Vddまたは基準電圧Vssが印加される主配線(第1基準電圧幹線VSS1)と、複数の副配線(基準電圧枝線VSSB)と、複数の基準電圧枝線VSSBに接続されている複数の回路セル(不図示)と、入力される制御信号に応じて、複数の基準電圧枝線VSSBのうち、所定の回路セルが接続されている基準電圧枝線VSSBと第1基準電圧幹線VSS1との接続および遮断を制御する電源スイッチセルSW1,SW2,…と、複数の基準電圧枝線VSSBを相互に接続する補助配線50と、を有する。

(もっと読む)

出力バッファ回路及び半導体装置

【課題】インピーダンスコードを更新して出力インピーダンスの調整を行う際、インピーダンスコードの更新に影響されない安定した出力を得ることが可能な出力バッファ回路及び半導体装置を提供すること。

【解決手段】pチャネルMOSFET及びnチャネルMOSFETを備える複数のドライバ回路が並列に接続されたバッファ部を備え、ドライバ回路の動作数により出力インピーダンスを調整するためのインピーダンスコードが供給される出力バッファ回路において、ドライバ回路のドライブ状態を示す状態情報信号に応じて、システムクロックに同期して、pチャネルMOSFET及びnチャネルMOSFETに対してインピーダンスコードを更新するコード更新制御回路を備える構成とする。

(もっと読む)

ターミネーション抵抗回路

【課題】回路の面積を増大させることなく、高い分解能及び広い抵抗値の範囲を有するターミネーション抵抗回路を提供すること。

【解決手段】本発明に係るターミネーション抵抗回路は、キャリブレーションコードが所定値を有すると、論理値が、前記キャリブレーションコードが前記所定値と異なる値を有する場合の論理値から変化する制御信号を生成する制御信号生成部と、前記キャリブレーションコードに応答してそれぞれオン/オフされる、相互に並列接続された複数の並列抵抗と、前記制御信号に応答してターミネーション抵抗回路全体の抵抗値を変更する抵抗値変更手段とを備える。

(もっと読む)

101 - 120 / 261

[ Back to top ]