Fターム[5J067KA68]の内容

Fターム[5J067KA68]に分類される特許

41 - 60 / 334

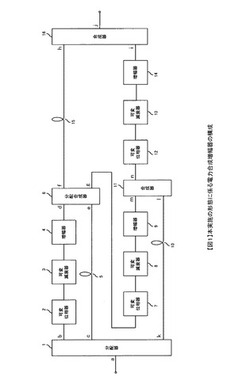

電力合成増幅器

【課題】 誤差増幅器から出力される歪成分の信号を全て無駄なく有効利用して、電力効率を向上させることができ、広帯域の信号に適用可能な電力合成増幅器を提供する。

【解決手段】 入力信号を3分配する分配器1と、位相及び振幅を調整した第1の分配信号を増幅する第1の増幅器4と、第2の分配信号と第1の増幅器4の出力とを逆位相で合成して歪成分を出力する分配合成器6と、歪成分を増幅する第2の増幅器9と、第2の増幅器9の出力と第3の分配信号とを合成する第1の合成器11と、第1の合成器11の出力を増幅する第3の増幅器14と、分配合成器6から出力される第1の増幅器4の出力信号と、第3の増幅器14の出力信号について、歪成分を逆相で合成して相殺し、信号成分を同相で合成して増幅器出力とする第2の合成器16とを備え、分配器1と、分配合成器6と、第1及び第2の合成器とをウィルキンソンカプラで構成した電力増幅器としている。

(もっと読む)

広帯域電力増幅器

【課題】出力特性の平坦度が良好な広帯域増幅器を提供する。

【解決手段】第1中心周波数有する第1増幅ユニットと、第1増幅ユニットに並列に配置され、第1中心周波数よりも高い第2中心周波数を有する第2増幅ユニットと、第1増幅ユニットの入力と第2増幅ユニットの入力に接続された電力分配器と、第1増幅ユニットの出力と第2増幅ユニットの出力に接続された電力合成器とを備える広帯域増幅器。

(もっと読む)

アナログ回路

【課題】高い歩留りを得ながらゲートスロープを抑制することができるアナログ回路を提供する。

【解決手段】アナログ回路には、発振トランジスタ27と、発振トランジスタ27に対する負性抵抗を変更する負性抵抗変更回路と、が設けられている。負性抵抗変更回路には、可変抵抗回路及び可変容量回路が含まれている。可変抵抗回路には、抵抗体29、抵抗体31及びトランジスタ(スイッチ)35が含まれ、可変容量回路には、キャパシタ30及び可変容量ダイオード36が含まれている。

(もっと読む)

分布増幅器及び分布ミキサ

【課題】異なる周波数帯の分波を可能とする分布増幅器を提供する。

【解決手段】本発明の分布増幅器は、第1,第2,第3伝送線路の一端を第1接続点で接続し、第1伝送線路の他端を第1入力端、第2伝送線路の他端を第2入力端とする入力疑似線路と、第4,第5,第6伝送線路の一端を第2接続点で接続し、第4伝送線路の他端を第1出力端、第5伝送線路の他端を第2出力端とする出力疑似線路と、入力端子が第1接続点、出力端子が第2接続点に接続された増幅部からなる単位増幅器と、第1帯域で左手系、第1帯域より高い第2帯域で右手系特性となるCRLH線路から構成され、信号入力端子を初段の第1入力端に接続し、第2入力端を次段の第1入力端に接続し、最終段の第2入力端を終端回路に接続し、第1信号出力端子が初段の第1出力端に、第2出力端がCRLH線路の第1入出力端子に、CRLH線路の第2入出力端子が次段の第1出力端に、最終段の第2出力端が第2信号出力端子にそれぞれ接続されている。

(もっと読む)

高周波多段能動回路

【課題】シャントの寄生キャパシタンス成分を相殺することができ、高域周波数帯における特性劣化を抑圧することができる高周波多段能動回路を得る。

【解決手段】高周波多段能動回路の段間インピーダンス整合回路20として、誘電体基板21上において一対の長さ1/4波長未満のくし型の導体電極パターンを対向して形成されるインターデジタルキャパシタを含み、かつこのインターデジタルキャパシタのくし型電極23a、23bの要部に誘導性スタブを接続し、かつこの誘導性スタブを介して能動デバイス10、30へのバイアス電圧を印加した。

(もっと読む)

高周波半導体増幅装置

【課題】発振対策を容易に講ずることができる高周波半導体増幅装置を提供すること。

【解決手段】パッケージ14内部に、半導体増幅素子11、入力整合回路基板17の表面上に形成された入力整合回路パターン15、および出力整合回路基板24の表面上に形成された出力整合回路パターン23を、パッケージ14内部に有する高周波半導体装置であって、出力整合回路基板24の表面上には、出力整合回路基板24の表面上に、出力整合回路パターン23に接続するように形成された出力信号ライン25に対して、容易に電気的に接続・切断可能な減衰器29が形成されている。

(もっと読む)

高周波回路

【課題】低周波発振と高周波発振とを共に抑制することができる高周波回路を提供する。

【解決手段】高周波回路は、複数のトランジスタ12、複数の入出力整合回路14−1,14−2、複数の抵抗体18、低周波発振抑制回路17を含む。複数のトランジスタは、半導体基板11上に並列に配列形成される。複数の入出力整合回路は、それぞれ第1の絶縁基板13−1上、第2の絶縁基板13−2上に、複数のトランジスタにそれぞれ接続されて設けられている。低周波発振抑制回路は、所望の周波数帯域を透過帯域として有し、並列に配列形成された複数のトランジスタのうち、両側のトランジスタのゲート端子に接続される。複数の抵抗体は、複数の入出力整合回路間のうち、トランジスタに最も近い位置に形成されるとともに、透過帯域の最も低い周波数の発振に対して低周波発振抑制回路を作用させることが可能な長さで、複数の入出力整合回路間に形成される。

(もっと読む)

高周波モジュール

【課題】高温通電時には、バイアスジャンプを回避することができ、実運用時には、外部電源を製品によらず共通化することができる。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、入力整合回路17に接続された高温動作用ゲートバイアス回路60および運用時用ゲートバイアス回路70と、高温動作用ゲートバイアス回路60に接続された高温動作用ゲートバイアス端子31aと、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1。

(もっと読む)

高周波モジュールおよびその動作方法

【課題】高温通電時にはバイアスジャンプを回避し、実運用時には外部電源を製品によらず共通化し、かつ端子数を削減する。

【解決手段】半導体装置24と、入力整合回路17と、出力整合回路18と、運用時用ゲートバイアス回路70と、運用時用ゲートバイアス回路70に接続された運用時用ゲートバイアス端子41aと、入力整合回路17に接続された高周波入力端子兼高温動作時用ゲートバイアス端子21aと、出力整合回路18に接続されたドレインバイアス回路80と、ドレインバイアス回路80に接続されたドレインバイアス端子41bと、出力整合回路18に接続された高周波出力端子21bとを備え、1つのパッケージに収納された高周波モジュール1およびその動作方法。

(もっと読む)

III族窒化物系高電子移動度トランジスタを含む低雑音増幅器

【課題】高い入力電力耐性と、低い雑音指数の両者を達成する低雑音増幅器を提供すること。

【解決手段】低雑音増幅器は、第一のIII族窒化物系トランジスタと、第一のIII族窒化物系トランジスタに結合された第二のIII族窒化物系トランジスタとを含んでいる。第一のIII族窒化物系トランジスタは、入力信号に対する第一増幅段を提供するように構成され、第二のIII族窒化物系トランジスタは、入力信号に対する第二増幅段を提供するように構成される。

(もっと読む)

電力合成分配器および電力合成分配器を用いた送信機

【課題】複数の増幅器のうちの一部が故障しても、電力合成分配器の分配損、合成損を最小とする。

【解決手段】複数の並列接続された第1の分岐側端子(113、114)と1つの第1の合成側端子(115)が第1の電力合成点(116)を介して接続された第1の分岐回路(127)と、複数の並列接続された第2の分岐側端子(133、134)と1つの第2の合成側端子(135)が第2の電力合成点(136)を介して接続された第2の分岐回路(137)とを有し、第1の合成側端子と複数の第2の分岐側端子が接続された電力合成あるいは電力分配を行う電力合成分配器において、第1の電力合成点から第2の電力合成点までの長さが1/2波長の整数倍である。

(もっと読む)

バイアス回路

【課題】バイアス回路を組み込んだ通信機器や電子機器の小型化を促進させるため、1つのチップにて構成することができるバイアス回路を提供する。

【解決手段】RFチョークとバイパスコンデンサとを有するバイアス回路において、少なくとも下面もしくはその内部にグランド電極40が形成された誘電体基板30と、前記誘電体基板30の表面に形成された入力端子32及び出力端子34と、前記誘電体基板30内もしくは表面に形成され、一端が前記入力端子32に接続され、且つ、他端が前記出力端子34に接続され、前記RFチョークを形成するRFチョーク形成電極36と、前記誘電体基板30内に、前記グランド電極40に対向して形成され、且つ、一端が前記出力端子34に接続され、前記バイパスコンデンサを形成するためのコンデンサ形成電極38とを有する。

(もっと読む)

高周波増幅器

【課題】高利得の増幅器であっても空間ループを原因とした異常発振を確実に防止することができる高周波増幅器を提供する。

【解決手段】誘電体基板2上に形成されたマイクロストリップ線路3と、このマイクロストリップ線路3に接続された増幅素子1と、誘電体基板2上に載置された増幅素子1を収容する収容部7aが形成された金属筐体7と、この金属筐体7の収容部7aに嵌合するとともに、増幅素子1と対向する面側に第1の溝部8bが形成された金属体8と、金属体8の第1の溝部8bに嵌挿される第1の導電性ラバー9とを備え、金属筐体7の収容部7aに金属体8を嵌合した時、第1の導電性ラバー9が誘電体基板2上に実装されている増幅素子1を押圧して、増幅素子1上の空間ループを遮断する。

(もっと読む)

ドハティ増幅器及び高周波伝送線路

【課題】インピーダンス変換の特性を低損失で容易に調整し、高周波大電力への耐用性が高く、小型化を実現するドハティ増幅器及び高周波伝送線路を提供する。

【解決手段】誘電体101は、厚さHAとHBの2層からなり、基板を構成する。2層の誘電体101の間には電極層102が積層されている。また、誘電体101の一面には、マイクロストリップ線路103が配設され、他面がグランド(GND)に接地されている。電極層102とGNDとはスイッチ104を介して接続されており、制御部105がスイッチ104を制御して、電極層102とGNDとの接続と開放を切り替える。

(もっと読む)

高周波モジュール筐体構造

【課題】筐体内の空間を導波管モードで伝播する高調波信号と結合して吸収できる終端器装荷アンテナを備えた高周波モジュール筐体構造を得ること。

【解決手段】出力段にマイクロ波増幅器が配置される高周波モジュール筐体において、前記高周波モジュール筐体内の空間を導波管モードで伝播する高調波信号の筐体共振による複数の電界集中箇所の少なくとも1つの電界集中箇所の付近に対応する該高周波モジュール筐体の天井面上所定位置に前記高調波信号と結合できるように配置されたアンテナと、前記アンテナに装荷され、該アンテナに誘起された高調波信号のエネルギーを熱ネルギーに変換して吸収する終端器とを備えた。

(もっと読む)

増幅器

【課題】広帯域特性の改善と隣接セルからの干渉問題の抑制を両立できる増幅器を得る。

【解決手段】3セル以上のユニットセルトランジスタ(11)が等間隔に配置されたマルチセルトランジスタ(10)と、スリット(23)で区切られたオープンスタブ(22)により、基本波の整数倍の周波数で短絡状態を形成するように各ユニットセルトランジスタに対応して設けられた高調波処理回路(21)を複数有し、各高調波処理回路がトーナメント構成となるように線路構成された出力整合回路(20)とを備えた増幅器であって、各高調波処理回路(21)は、マルチセルトランジスタを構成する各ユニットセルトランジスタのゲートまたはドレイン端子の少なくとも一方から、電気長で1/2波長未満の距離に配置され、オープンスタブ(22)が、主線路と平行して片側に1本で配置されている。

(もっと読む)

電力増幅器

【課題】 高調波成分の負荷を、基本波の調整に影響されることなく短絡から開放までの範囲で最適な負荷となるよう独立して設定することができ、高い電力変換効率を得ることができる電力増幅器を提供する。

【解決手段】 トランジスタ3の出力に、高調波に対する負荷を設定して反射する高調波反射回路4と、設定された高調波に対する後段の負荷の影響を分離する負荷分離回路5と、基本波についてトランジスタ3と出力負荷との整合を取る基本波整合調整回路6を備え、高調波反射回路4に設けられた先端開放スタブ23の長さが調整されることで、高調波の負荷を調整する電力増幅器としており、高調波成分及び基本波について独立して最適な負荷調整を行うことができ、電力変換効率を向上させることができるものである。

(もっと読む)

インピーダンス変換器、集積回路装置、増幅器および通信機モジュール

【課題】小型で伝送損失の少ないインピーダンス変換器、集積回路装置を実現する。

【解決手段】集積回路装置は、インピーダンス変換器15と、集積回路11A,11Bとを有し、インピーダンス変換器15は、第1の誘電率を有する第1の基板21の上方に設けられ、第1のインピーダンスを有する第1の伝送線路22A,22Bと、第1の誘電率より高い誘電率を有する第2の基板31の上方に設けられ、第1の伝送線路22A,22Bと電気的に接続され、第1のインピーダンスよりも低い特性インピーダンスを有する第2の伝送線路32AA,32ABおよび第3の伝送線路32BA,32BBと、第2の伝送線路32AA,32ABと第3の伝送線路32BA,32BBとの間に接続される抵抗35A,35Bとを有し、集積回路11A,11Bは、第2の伝送線路32AA,32ABおよび第3の伝送線路32BA,32BBと電気的に接続される。

(もっと読む)

バイアス回路

【課題】 不要波の出力を抑制することのできる小型なバイアス回路を得ることを目的とする。

【解決手段】 半導体素子3に電力を供給するバイアス回路において、インダクタ5及びキャパシタ6が直列に接続された直列回路と、直列回路に並列に接続されて並列回路を構成するインダクタ7と、接地されたキャパシタ8とインダクタ7との間に接続され、外部から電力が供給されるバイアス端子9を備えて、直列回路および並列回路の共振により、半導体素子3の不要波を除去し所望の周波数のみを伝達する。

(もっと読む)

電子回路

【課題】広帯域および小型化を可能とすること。

【解決手段】第1端子が接地された第1トランジスタT1と、制御端子G2に第1トランジスタの第2端子D1が入力し、第1端子が第1キャパシタを介し接地され、第2端子に直流電源が接続される第2トランジスタT2と、第2端子D1と制御端子G2との間の第1ノードN1に一端が接続され、他端が第2キャパシタを介し接地された第1分布定数線路L1と、一端が第2端子D1に接続され、他端が第1ノードに接続された第2分布定数線路L2と、一端が制御端子G2に接続され、他端が第1ノードに接続された第3分布定数線路L3と、第1分布定数線路と第2キャパシタとの間の第2ノードN2と、第2トランジスタの第1端子と第1キャパシタとの間の第3ノードN3と、の間に接続された抵抗R1と、第3ノードと第2端子D1との間を第1分布定数線路と抵抗とを介して直流的に接続する経路と、を具備する電子回路。

(もっと読む)

41 - 60 / 334

[ Back to top ]