Fターム[5J079BA22]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 起動 (147) | 高速起動 (59)

Fターム[5J079BA22]に分類される特許

41 - 59 / 59

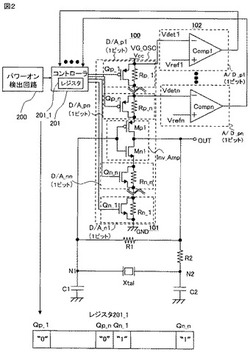

半導体集積回路

【課題】電源電圧の低下、温度上昇等の発振器の動作条件の変動によって、発振後の発振動作の停止、発振安定時間の延長、起動時の発振の失敗等の不具合を解消すること。

【解決手段】入出力端子間に振動子が接続可能な反転増幅器Inv_Ampは、PMOSMp1とNMOSMn1を含む。ディジタル入力信号に応答して出力インピーダンスが変化するよう抵抗とMOSスイッチとを含む複数のD/A変換器D/Ap_1…D/Ap_n、D/An_1…D/An_nを、Mp1のソースと電源電圧VccまたはMn1のソースと接地GNDの間に接続する。可変利得発振器VG_OSCの動作条件の変化をA/D変換ユニット102が検出して、複数のD/A変換器の合計の出力インピーダンスを徐々に変化させる。

(もっと読む)

圧電発振回路

【課題】 圧電素子を用いた発振回路で起動時間の早い圧電発振回路が求められていた。

【解決手段】 本発明は、圧電素子と、発振回路からなる圧電発振回路において、発振開始時に使用する起動発振用回路と定常時に使用する定常発振用回路とを持ち、発振開始時に使用する起動発振用回路と定常時に使用する定常発振用回路とを切り替える切り替え回路を備え、起動時と定常時とを判断する判断回路を備えた圧電発振回路により、より早い起動特性を得ている。

(もっと読む)

発振回路、物理量トランスデューサ及び振動ジャイロセンサ

【課題】 簡素な構成で、発振ループ内の振幅制御を高精度で実現し発振起動時間を短縮する発振回路、物理量トランスデューサ及び振動ジャイロセンサを提供する。

【解決手段】 発振回路10は、制御電圧Vcの変化に対するそのゲインの変化を示す所与の感度特性を有し、発振ループ内の発振振幅を制御するためのゲインコントロールアンプ20と、発振振幅に応じてゲインコントロールアンプ20のゲインを調整するための制御電圧Vcを出力するゲイン制御回路30とを含む。ゲイン制御回路30は、発振振幅を監視して発振ループ内の発振が定常状態か起動過程かを判別する。ゲインコントロールアンプ20は、発振が起動過程と判別されたとき、制御電圧Vcに基づいて第1の感度特性に従ってそのゲインを変化させ、発振が定常状態と判別されたとき、制御電圧Vcに基づいて第1の感度特性より感度の低い第2の感度特性に従ってそのゲインを変化させる。

(もっと読む)

移動通信基地局装置の恒温槽付水晶発振器のウォームアップ方法及び移動通信基地局装置

【課題】充放電回路を利用したウォームアップ方法は、電源断時間によっては、ウォームアップ時間を最適な時間に短縮することができない。また、温度上昇速度の恒温槽付水晶発振器の個体差分のウォームアップ時間を短縮することができない。

【解決手段】CPU102は、上位装置150からの現在時刻を一定時間毎に更新してFーROM103に更新記憶している。装置電源の瞬断が発生した場合、CPU102は、電源復旧時にF−ROM103に更新記憶されていた時刻を電源断時刻とし、また、電源が復旧したときに上位装置150から取得した現在時刻とから電源断時間を算出し、その電源断時間と、FーROM103から読み出した、予め恒温槽付水晶発振器104の出力クロックから算出された電源断時間対ウォームアップ時間の傾き値とを用いて、恒温槽付水晶発振器104の個体差の影響のない、最短のウォームアップ時間を算出する。

(もっと読む)

高速始動付き低雑音基準発振器

速い始動時間及び定常状態での低い雑音を有する周波数源が提供される。周波数源は、発振器(102)と、発振器始動でのアナログAGCループと定常状態の動作でのデジタルAGCループとの間を切り替えるハイブリッド自動利得制御(AGC)ループとを含む。アナログAGCループは、発振器(102)に接続されたピーク検出器(104)と、ピーク検出器(104)出力と基準電圧との差を積分する誤差積分器(106)とを含む。デジタルAGCループは、ピーク検出器出力と高/低基準電圧とを比較する比較器(110)と、タイマ信号を与える発振器(102)カウンタと、デジタル・ワードを供給されるデジタル/アナログ変換器(DAC)(114)と、DAC(114)と発振器(102)との間のロー・パス・フィルタ(116)とを含む。タイマ信号は、マルチプレクサ(108)にアナログAGCループ又はデジタルAGCループのいずれかを選択させる。  (もっと読む)

(もっと読む)

始動制御装置を含む発振器

発振装置(1)には、発振器コア(2)と、制御可能な静電容量値を有する、発振器コア(2)に接続された容量性ローディングユニット(3、3a、3b)と、第1および第2のメモリユニット(5a、5b)を含む、容量性ローディングユニットに接続されたメモリ装置(4)と、が含まれる。第1のメモリユニット(5a)は、始動期間中に、静電容量値を制御するために容量性ローディングユニット(3、3a、3b)に供給される第1の値を格納するように構成される。第2のメモリユニット(5b)は、動作期間中に、静電容量値を制御するために容量性ローディングユニット(3、3a、3b)に供給される第2の値を格納するように構成される。発振装置(1)の始動方法によれば、発振信号の振幅が測定される。さらに、動作期間の開始時点が、発振信号が所定の閾値を超える時点として選択される。  (もっと読む)

(もっと読む)

発振回路

【課題】補償信号を発生する補償回路と、補償回路からの補償信号に応じて発振周波数を制御可能とされた発振部とを有する発振回路に関し、高速に所望の周波数に安定されることができる発振回路を提供することを目的とする。

【解決手段】本発明は、補償信号を発生する補償回路(122)と、補償回路(122)からの補償信号に応じて発振周波数を制御可能とされた発振部(121)とを有する発振回路において、抵抗(R1)及びキャパシタ(C2)を含み、補償信号の積分波形を発振部(121)に供給する積分回路(R1、C2)と、積分回路(R1、C2)に含まれるキャパシタ(C2)を充電する充電回路(123)と、積分回路(R1、C2)に含まれる抵抗(R1)の両端を短絡させるスイッチ回路(124)と、キャパシタ(C2)の充電が終了した後、スイッチ回路(124)により積分回路(R1、C2)に含まれる抵抗(R1)を短絡させる制御回路(125)とを有することを特徴とする。

(もっと読む)

圧電発振器

【課題】 解決しようとする課題は、あらゆる圧電発振器に対して起動時間の短縮化を実現すること。

【解決手段】圧電振動子を有する圧電発振回路と、該圧電発振回路の発振ループ回路と電源電圧ラインとを接続する為のスイッチ回路と、該スイッチ回路のON/OFF動作を制御する為の制御回路とを備えた圧電発振器であり、前記電源電圧印加した後、前記圧電振動子の励振信号の振幅レベルが極大値±0.1λの範囲内である時に前記スイッチ回路がON動作するものであることを特徴とする圧電発振器。

(もっと読む)

水晶発振器の整定時間を短縮する方法

水晶発振器を制御する水晶の発振を、当該水晶に開始パルスを印加することによって開始する方法及びシステム。開始パルスは、上記水晶の周期の2分の1未満のパルス幅を有する。 (もっと読む)

水晶発振回路

【課題】分周回路を内蔵した水晶発振器において、発振起動時に異常発振したり、起動性が悪いという課題があった。

【解決手段】本発明の水晶発振回路は、発振回路と分周回路と出力バッファ部の電源をそれぞれ別の駆動電圧で動作させる。複数の電源を用いて駆動電圧を生成し、駆動するのである。このような構成とすることによって、電源投入直後、発振回路の発振出力振幅が微小な状態において、分周回路および出力バッファ部の動作を停止することができ、主に出力バッファ部が動作することによって発生する電源ノイズを抑制することができる。これによって、異常発振や発振起動性の悪化を防ぐことができる。

(もっと読む)

低消費電力回路

【課題】 起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】 カレントミラー回路M1と、カレントミラー回路M1の出力端に一端を接続した第1分割抵抗R1、この第1分割抵抗R1に一端を接続した第2分割抵抗R2との直列回路からなるバイアス分割回路R12と、第1分割抵抗R1の一端に制御端子(ゲート端子)を、第2分割抵抗R2の他端に第2主電流端子を、GNDに第1主電流端子を接続した第1トランジスタN1と、第2分割抵抗R2の他端に制御端子(ゲート端子)を、カレントミラー回路M1の入力端に第2主電流端子を、第2主電源GNDに第1主電流端子を接続した、第1トランジスタN1と同一チャネル導電型の第2トランジスタN2とを含み、起動時に第1分割抵抗R1と第2分割抵抗R2との接続ノードに起動電流ISTを印加する。

(もっと読む)

電圧制御発振回路用の印加電圧制御回路

【課題】LSIから制御可能な汎用ポートの“H”レベルのレベルが、トランスミッションゲートの“H”レベルを認識する最小許容値を満足しない可能性が発生し、水晶振動子の発振安定に時間かかる。

【解決手段】電源起動時はNPNトランジスタQN1を遮断状態にして、第1のトランスミッションゲートG1を導通状態に、第2のトランスミッションゲートG2を遮断状態にし、電源電圧VDDを第1のトランスミッションゲートG1を介して電圧制御発振回路100の制御入力端子n3に印加する。水晶振動子Xの発振安定後は汎用端子12への制御信号によりNPNトランジスタQN1を導通状態に切り替えることを通じて第1のトランスミッションゲートを遮断状態に、第2のトランスミッションゲートを導通状態に切り替え、電圧制御端子11の電圧を第2のトランスミッションゲートG2を介して電圧制御発振回路の制御入力端子に印加する。

(もっと読む)

水晶発振回路

【課題】バランスの良い状態を、使用者が発振特性を選択することのできるようにし、最終的に使用者において発振特性を合わせ込める水晶発振回路を実現する。

【解決手段】ICに内蔵され、かつインバータ1の入力と出力の間に、水晶振動子2と帰還抵抗3が並列に接続されてなる水晶発振回路において、該インバータ1のレイアウト上のサイズを可変な構造とし、プログラム制御により、外部からある値が設定されると、設定された値に更新する設定手段6と、変更用のプログラムが起動されると、該変更用プログラムにより該インバータ1のレイアウト上のサイズを上記値に対応したサイズに変更する切換え変更手段とを具備する。設定手段6としては、値を設定するレジスタを設けるか、IC端子の状態を変更するか、あるいは、値を指定するROMを設ける方法がある。

(もっと読む)

圧電発振器

【課題】 高速起動回路を備えた水晶発振回路をIC化する際の小型化する手段を得る。

【解決手段】 圧電振動子と、増幅回路と、高速起動回路とを備えた圧電発振器であって、高速起動回路は第1のPNP型Tr(トランジスタ)と、第2のNPN型Trと、第3のPNP型Trとを備え、第1のTrのエミッタと電源との間に第1の抵抗を接続すると共にコレクタを接地し、第2のTrのコレクタを電源に接続すると共にベースとエミッタとを接続し、エミッタ−接地間に容量を接続し、第2のTrのエミッタと第1のTrのベースを接続し、第2のTrのエミッタと第3のTrのベースとを接続し、第3のTrのコレクタを圧電振動子の一端子に接続して構成される。

(もっと読む)

発振装置及び発振方法

【課題】 従来の発振装置では、CR発振回路は、水晶発振回路の発振の起動の支援を充分に適切に行うことができなかった。

【解決手段】 本発明に係る発振装置は、水晶発振子により規定される周波数を有する第1の信号を発振する水晶発振回路と、前記水晶発振回路が前記第1の信号を定常的に発振するまでの過渡期において、前記周波数と実質的に同一な第2の周波数を有する第2の信号を生成し、当該第2の信号を前記水晶発振回路に供給するCR発振回路とを含む。

(もっと読む)

水晶発振回路

本発明の課題は、低位相雑音で安定した動作を得ることである。また他の課題は、起動時間の遅延を生じさせない発振出力を得ることである。 本発明によれば、帰還回路(5)によって、水晶振動子(10)の発振出力を帰還した信号を、負荷容量選択部(3)の負荷容量を選択する制御信号に重畳させて、制御信号がもつ電圧雑音により受けるMOSトランジスタ(50)への影響を受けにくくして、位相雑音の低減化を図り、また、起動時においてある一定時間、負荷容量選択部(3)に入力される制御信号を制限して、短時間で起動することができる水晶発振回路を実現できる。  (もっと読む)

(もっと読む)

発振器起動制御回路

【課題】起動時間を短縮するとともに、起動時間を安定して制御し、さらに発振回路の起動後、発振周波数を安定化することができる発振器起動制御回路を提供する。

【解決手段】発振回路(1)は、インバータ(14)の入力と出力を水晶振動子(15)の両端および抵抗(16)の両端に接続し、入力をMOS可変容量(10)のドレインに、出力をMOS可変容量(11)のドレインに接続し、MOS可変容量(10)のソースを固定容量(12)に接続し、MOS可変容量(11)のソースを固定容量(13)に接続し、固定容量(12、13)の他端をGNDに接続している水晶発振回路である。更にMOS可変容量(10)のゲートに抵抗(18)とスイッチ(7)を接続し、MOS可変容量(11)のゲートに抵抗(19)とスイッチ(8)を接続し、抵抗(18、19)の他端を互いに接続し、更に電圧制御回路(3)に接続している。

(もっと読む)

発振器及び半導体装置

【課題】 低消費電流化の貢献だけではなく、発振安定待ち時間を短縮し、カメラや車載電装部品などで要求されるシステムの起動を早めることを課題とする。

【解決手段】 入力信号を反転増幅して出力する反転増幅器(105)と、反転増幅器の入出力端子間に接続される振動子(103)と、振動子に並列に接続される帰還抵抗(104)と、振動子に接続され、振動子、反転増幅器及び帰還抵抗により発振する負荷時並列共振周波数又は並列共振周波数の信号に基づく第1のクロック信号を機能ブロックに出力する出力回路(106〜108)とを有する発振器が提供される。

(もっと読む)

VCXOの起動時間を短縮するための方法と装置

無線端末(10)の所望の基準周波数を生成するための、低減された起動時間を有するVCXO(Voltage Controlled Crystal Oscillator)(100)のような電圧制御発振器(100)が本願明細書において記載されている。本発明によれば、VCXO(100)は、電圧コントローラ(110)によって発振器(120)に印加された可変電圧に基づいて、所望の基準周波数を生成する発振器(120)を含む。加えて、VCXO(100)は、発振器(120)に伴うキャパシタンスを低減するためバイアス電圧を発振器の入力ノードに印加し、VCXO(100)のDC電流消費または同調レンジに悪影響を与えること無く起動時間を低減する起動コントローラ(130)を含む。  (もっと読む)

(もっと読む)

41 - 59 / 59

[ Back to top ]