Fターム[5J079BA23]の内容

電気機械共振器を用いた発振回路 (23,106) | 目的、効果 (4,554) | 起動 (147) | 不要モード発振防止 (21)

Fターム[5J079BA23]に分類される特許

1 - 20 / 21

発振回路、発振器、電子機器及び発振回路の起動方法

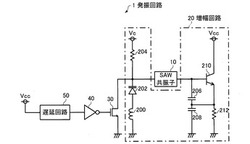

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

圧電振動子、圧電ユニット、圧電発振器と電子機器及びそれらの製造方法

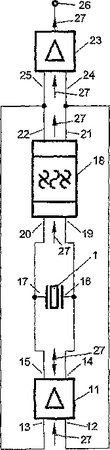

【課題】逆相の屈曲モードで振動する超小型の音叉型圧電振動子を提供する。

【解決手段】基部部分に接続された少なくとも第1及び第2音叉腕とを備えて構成され、音叉腕の各々の一端部が基部部分に接続され、他端部が自由であり、各々の上面と下面の少なくとも一面に溝が形成され、基本波モード振動の品質係数Qm1、共振周波数fm1、等価直列抵抗Rm1、等価容量Cm1と2次高調波モード振動の品質係数Qm2、共振周波数fm2、等価直列抵抗Rm2、等価容量Cm2を備え、振幅係数ka21がka21=(fm1Rm1Cm11/2)/(fm2Rm2Cm21/2)で定義され、かつ、安定係数As12がAs12=(Cm2Q22)/(Cm1Qm12)で定義される時、安定係数As12が0.0529<As12<0.333の範囲内、かつ、振幅係数ka21が0.23<ka21<0.577の範囲内にある。

(もっと読む)

圧電発振器、圧電発振器の製造方法、圧電発振器の温度補償方法

【課題】圧電発振器、圧電発振器の製造方法、圧電発振器の温度補償方法を提供する。

【解決手段】周波数温度特性にアクティヴィティディップ56を有する圧電振動子12と、前記圧電振動子12を発振させ発振信号50を出力する発振回路14と、記憶回路18と、を有し、前記記憶回路18には、前記周波数温度特性の情報54を近似する近似式の情報から抽出された特性情報58と、前記周波数温度特性の情報54と前記近似式の情報に基づいて算出されアクティヴィティディップ56を示すディップ情報62と、が記憶されたことを特徴とする。

(もっと読む)

発振器、発振装置

【課題】発振出力開始時のノイズに起因する異常発振や、電源立上時の過渡応答に起因する不要なパルスの出力を防止する為、ローパスフィルタの構成を変えて対応を可能とする発振器の提供。

【解決手段】発振手段からの発振信号の、発振開始からのパルス数が所定の閾値に達したことを発振パルスカウント回路3が検出すると、発振手段からの発振信号を選択して出力する。

(もっと読む)

SAWデバイス

【課題】圧電基板上に異なる共振周波数のSAW素子を2個備え、SAW素子の入力端または出力端の少なくとも一方が共通端子により接続されて共通化されたSAWデバイスにおいて、寄生容量および寄生インダクタンスが大きく異なることによる発生する、周波数特性の歪み、スプリアス周波数などの異常発振を抑制することを目的とする。

【解決手段】高周波側のSAW素子6を第1幅員の第1電極指と、第1電極指から第1間隙をおいて配置された第2幅員の第2電極指と、第2電極指から第2間隙をおいて配置された第3幅員の第3電極指と、第1電極指と第3電極指との隣にそれぞれ配置された第3間隙の半分のスペースとを備えた単位区間を複数区間繰返して構成され、第1電極指と第3電極指とを同相とし、第2電極指と第1電極指および第3電極指とを逆相とし、第1幅員と第3幅員とを同値とし、第1間隙と第2間隙とを同値とすることを特徴とする。

(もっと読む)

表面実装用の水晶発振器

【課題】電源投入時の周波数変動を防止する表面実装発振器を提供することを目的とする。

【解決手段】底壁1aの両主面に枠壁1(bc)を積層して両主面に凹部を有する容器本体1と、前記容器本体1の一方の凹部内底面に設けられた一対の水晶保持端子5(ab)に引出電極10(ab)の延出した一端部両側が固着された水晶片2と、前記一方の凹部の開口端面に接合して前記水晶片2を密閉封入する金属カバー4と、前記容器本体1の他方の凹部内底面に設けられた回路端子7にIC端子が電気的・機械的に接続したICチップ3とを備えた表面実装用の水晶発振器において、前記水晶保持端子5(ab)は前記容器本体1の内底面に延出した放熱用電極14を有する構成とする。

(もっと読む)

圧電発振回路、および圧電発振回路の起動方法

【課題】異常発振を防止する圧電発振器、および圧電発振器の起動方法を提供する。

【解決手段】発振信号を出力する圧電発振回路10であって、圧電振動子12と、負荷容量を備え、前記負荷容量を可変させる可変容量回路16と、伸長コイル24と、増幅回路14と、を有し、前記圧電発振回路10は、前記負荷容量を可変させることにより前記負荷容量の可変容量範囲に対応する発振周波数変動範囲内で前記発振信号の発振周波数を可変可能であり、前記圧電発振回路の発振開始期間において前記可変容量回路16の前記負荷容量の値を発振開始期間用容量値に固定する容量制御を行う容量制御回路18を備えてなる。

(もっと読む)

水晶発振器

【課題】 電源立ち上がり直後にCMOSインバータICの自励発振によって発生する不要波を出力しないようにして、安定した発振器出力を得ることができる水晶発振器を提供する。

【解決手段】 発振部10のCMOSインバータICの後段にNANDゲートIC11を備え、発振部10の出力をNANDゲートIC11の入力端子Aに入力すると共に、入力端子Bに電源電圧を入力し、電源電圧端子と入力端子Bとの間に抵抗R4を直列接続し、抵抗R4と入力端子Bとの間に、一端が接続され他端が接地されたコンデンサC4を設け、電源投入後、CMOSインバータICからの自励発振に由来する不要波が出力されている間は、NANDゲートICに入力される電源電圧がハイレベルとならないよう、抵抗R4及びコンデンサC4による時定数が設定されている水晶発振器としている。

(もっと読む)

圧電振動装置、発振回路及び電子装置

【課題】Qが高く、耐電力性に優れているだけでなく、印加電圧によるインピーダンス特性曲線の乱れが生じ難い、圧電振動装置を得る。

【解決手段】圧電薄膜4の下面に下部電極5が、上面に上部電極6が形成されている圧電振動部3が基板2から浮かされた状態で支持部9,10により支持されており、矩形の圧電振動部3の輪郭振動を利用しており、該輪郭振動と、圧電振動部3において生じる屈曲振動とが結合しないように、上記輪郭振動の共振周波数と屈曲振動の共振周波数とが隔てられている、圧電振動装置1。

(もっと読む)

水晶発振回路

【課題】 ディレイ回路を設けたり、バイアス決定回路のバイアス点と波形整形回路のスレッショルドとを異ならせたりすることなく、消費電流を低減し、自励発振や異常発振を防ぐことができる水晶発振回路を提供する。

【解決手段】 水晶振動子21および水晶振動子21の出力を増幅し、電源電圧より低い定電圧源LDO1により駆動される発振増幅器22を有する水晶発振部2の出力に、電源電圧レベルにレベルシフトする結合コンデンサ3が接続され、その結合コンデンサ3の出力に、ソースがVddに、ゲートがVssに接続されたPチャネルMOSトランジスタ41およびソースがVssに、ゲートがVddに接続されたNチャネルMOSトランジスタ42のそれぞれのドレインが接続されたバイアス決定回路4が接続され、そのバイアス決定回路4の出力に振幅検知回路5、および波形整形回路6が接続されている。

(もっと読む)

発振回路、発振器

【課題】発振に必要な負性抵抗を小さくすると同時に回路の低消費電力を図ることのできる発振回路及び発振器を提供する。

【解決手段】発振回路10は、トランジスタM1とトランジスタM2とが差動接続されるクロスカップル型回路からなり、振動子SAWの共振点帯域で発振する。トランジスタM1は第1ソース負荷回路としての抵抗器RL1に接続され、トランジスタM2は第2ソース負荷回路としての抵抗器RL2に接続されている。また、トランジスタM1は第1ドレイン負荷回路としての抵抗器Rs1に接続され、トランジスタM2は第2ドレイン負荷回路としての抵抗器Rs2に接続されている。第1ソース負荷回路のインピーダンスの大きさが第1ドレイン負荷回路のインピーダンスの大きさ以上であり、且つ、第2ソース負荷回路のインピーダンスの大きさが第2ドレイン負荷回路のインピーダンスの大きさ以上とする。

(もっと読む)

発振回路

【課題】自励発振が起こらず、出力対称性を確保できるようにした発振回路を提供する。

【解決手段】コルピッツ型の水晶発振回路において、CMOSインバータINV1の出力側(ノードN1)と電源VDDとの間に、CMOSインバータINV1の帰還バイアス電圧を高くするためのトランジスタMP1と発振出力が無いときONするトランジスタMP2とを直列接続して、電源投入初期時にそのノードN1をVDD/2より高い電圧にプルアップし、正常発振が開始してノードN3の電圧が所定値に達すると、トランジスタMP2をOFFしてノードN1のプルアップを解除する。また、CMOSインバータINV1の出力を反転するCMOSインバータINV2を接続し、その出力側のノードN2にアンド回路AND1を接続し、正常発振が開始してノードN3の電圧が所定値に達したとき、それから遅延回路DL1の遅延の後に、アンド回路AND1のゲートを開いて、ノードN2の発振信号を出力端子OUTに出力する。

(もっと読む)

圧電振動子及び圧電発振器

【課題】圧電振動素子のマウント位置のバラツキによる浮遊容量のバラツキを低減するこ

とができる圧電振動子を提供する。

【解決手段】圧電基板11と、圧電基板11の表裏両面に夫々形成された励振電極12、

13と、励振電極12、13から夫々圧電基板11の端面に引き出されたリード端子12

a、13aとを備えた圧電振動素子10と、上面に圧電振動素子10のリード端子12a

、13aが導電性接合部材6を介して夫々接合される素子搭載用パッド7a、7bを備え

た凹所3と、外部底面に設けられた複数の実装電極5a〜5dと、素子搭載用パッド7a

、7bと実装電極5a、5bとを接続する内部配線とを有するパッケージ2とを備えた圧

電振動子1であって、実装電極5aと素子搭載用パッド7aとを接続する内部配線8aが

励振電極12、13と対面すると共に、内部配線8aと励振電極12、13間の距離が一

定となるように配置した。

(もっと読む)

発振回路

【課題】所望の周波数以外の周波数で発振するおそれがあり、また、出力される発振周波

数の波形が正弦波に近似しないことがあった。

【解決手段】第1の電位及び第2の電位間に接続されたCMOSインバータと、一端がC

MOSインバータの入力端に接続された第1の素子部と、一端がCMOSインバータの入

力端に接続され、他端がCMOSインバータの出力端に接続された第2の素子部と、一端

がCMOSインバータの出力端に接続された第3の素子部と、一端が第1の素子部の他端

及び第3の素子部の他端に接続され、他端が第1の電位及び第2の電位のうちの一方に接

続された第4の素子部とを含み、第1、第2、第3、及び第4の素子部は、水晶振動子、

抵抗器、インダクタ及びキャパシタのいずれかであり、第1、第2、及び第3の素子部に

より規定される周波数で発振する。

(もっと読む)

逓倍発振回路及びECL出力圧電発振回路

【課題】小型化で異常発振の発生を抑制できる逓倍発振回路を提供する。

【解決手段】水晶振動子Y1を有し所定の周波数で発振する水晶発振回路11と、水晶発

振回路11の発振出力に含まれる所定の高調波出力に同調する同調回路13と、増幅用ト

ランジスタQ2とこの増幅用トランジスタQ2コレクタ−ベース間に接続され自己バイア

ス機能とデカップリング機能を有する抵抗R4と、増幅用トランジスタQ2コレクタに接

続され、増幅用トランジスタQ2から出力される所定の高調波出力に同調する同調回路1

5と、同調回路13と同調回路15との間を結合する結合コンデンサC6とを備えるよう

にした。

(もっと読む)

発振回路

【課題】発振部の後段に接続する波形整形部の内部容量が発振部の発振周波数に与える影響を排除し、発振回路の異常発振を防止すること。

【解決手段】この発振回路は、所望の周波数で発振して発振信号を出力する発振部10と、前記発振部10の出力端に接続され前記発振信号を波形整形する波形整形部20と、前記発振部10と前記波形整形部20との間に介挿された抵抗30とを具備し、抵抗30と波形整形部20の内部容量22とでローパスフィルタを形成する。

(もっと読む)

コルピッツ型発振器

【課題】主振動(Cモード)での安定発振を得ながら、不要振動(Bモード)を確実に抑圧した発振を得る。

【解決手段】圧電振動子X1とトランジスタQ1および分割容量成分C1,C2を含むコルピッツ型発振器において、容量成分C1と容量成分C2との接続中点とトランジスタのエミッタとの間に容量成分C3とインダクタL1の直列接続から成る帰還回路を挿入し、容量成分C2と並列にインダクタL2を挿入し、容量成分C2とインダクタL2の並列共振周波数を当該発振器の発振周波数近傍に設定することにより、圧電振動子から見た回路側の負性抵抗となる周波数帯域を、所望する周波数のみを含む狭帯域に設定して当該発振器の不要振動を抑圧する。

(もっと読む)

水晶発振回路

【課題】Bモード の共振を確実に抑圧でき、それによってCモード の共振を確実に励振することができる水晶発振器を提供する。

【解決手段】水晶発振回路は、SCカットやITカットなどの水晶振動子を用いているため、Cモード(主モード)周波数にBモード(不要モード)周波数が近接しているため、水晶発振回路の帰還ループ中に、Cモード周波数を通過させるCモード共振回路(主モード共振回路)と、不要モード周波数での発振を抑圧するトラップ回路を具備する構成とする。

(もっと読む)

高周波電磁発振を発生させる発振器回路

高周波電磁発振を発生させる発振器回路が、少なくとも1つの入力と少なくとも1つの出力とを有する増幅器構成と、増幅器構成の少なくとも1つの出力に接続される水晶振動子と、少なくとも1つの入力が、水晶振動子と、水晶振動子に接続された少なくとも1つの、増幅器構成の出力とに接続され、少なくとも1つの出力が、増幅器構成の入力または少なくとも1つの入力に反結合されたバンドパス・フィルタ構成とを含む。バンドパス・フィルタ構成の振幅−周波数特性および/または位相−周波数特性を、増幅器構成および水晶振動子の振幅−周波数特性および位相−周波数特性の関数として設計することにより、水晶振動子の選択された高調波に対してのみ発振条件が満たされ、この選択された、水晶振動子の高調波によって形成される高周波電磁発振をバンドパス・フィルタ構成の出力において利用することができる。この発振器回路は、シンプルに構成され、干渉の影響を少なくともほぼ受けない動作が可能である。  (もっと読む)

(もっと読む)

発振回路、圧電発振器および発振回路の制御方法

【課題】 インバータの閾値電圧が可変可能であり、発振段回路内に生じたノイズに影響されることなく圧電振動子を発振させる発振回路、圧電発振器および発振回路の制御方法を提供する。

【解決手段】 圧電発振器10は、圧電振動子12と、PチャネルMOSトランジスタ16およびNチャネルMOSトランジスタ18からなるCMOS回路を多段に接続してなり、前記圧電振動子12に接続したインバータ14と、前記NチャネルMOSトランジスタ18のソース側に接続したスイッチ28と、前記インバータ30の出力側に接続し、前記インバータ14から出力されたパルス信号のカウンタ26と、前記カウンタ26の後段に接続し、前記スイッチ28を制御する制御器22と、を有する構成とした。

(もっと読む)

1 - 20 / 21

[ Back to top ]