Fターム[5J081FF08]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路構成 (543) | 比較器 (56)

Fターム[5J081FF08]に分類される特許

1 - 20 / 56

半導体装置

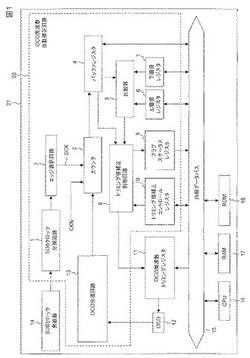

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路

【課題】自励発振回路周辺の状態変化による発振周波数の変化を抑えることができる周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路を提供する。

【解決手段】周波数自動調整機能付自励発振回路は、基準信号を生成する基準信号生成回路101bと、基準信号の周波数を調整する発振周波数調整回路101aとを有する自励発振回路101と、互いに特性の異なる1組の抵抗素子を含み、1組の抵抗素子の抵抗値の変化の違いにより自励発振回路101の周辺状態を検出し、検出された周辺状態を示す信号を出力する特性変動検出回路102_1と、特性変動検出回路102_1の出力信号に基づいて発振周波数調整回路101aによる周波数調整を制御する制御部103とを備える。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

発振周波数補正装置

【課題】同期信号の検出が困難なときにも正確な発振周波数のクロック信号を生成できるようにした発振周波数補正装置を提供する。

【解決手段】電源投入時の劣化検出タイミングにおいて、定電流源23から抵抗器22に通電して得られたA/D変換器6のAD変換値(抵抗器22の端子電圧VR)に基づいて、CPU2が逓倍数設定値FMULRを補正する。この場合、定電流源20を用いることなく定電流源23が作動して抵抗器22に通電する。CPU2は、抵抗器22の端子電圧を測定することでCR発振器14内の抵抗器R1の抵抗値の経年変化を反映し、この変化に基づいてCR発振回路8のクロック信号CLKの逓倍数設定値FMULRを補正する。

(もっと読む)

発振器

【課題】発振器の発振周波数、又は負荷の大小によるバッファー回路の出力レベル変動を抑制して、バッファー回路の消費電力を低減する発振器を提供する。

【解決手段】この発振器100は、発振回路18と、発振回路18の発振信号を増幅するプリバッファー回路19と、最終段のバッファー回路11と、バッファー回路11の出力電圧レベルを検出するレベル検出回路8と、レベル設定2に応じてレベル検出回路8のレベルを増幅する増幅回路1と、増幅回路1から出力したレベル検出回路8の検出レベルに基づいて出力信号(OUT)の電圧、又は電流を制御してバッファー回路11の出力レベルを調整するレベル調整回路5と、を備えて構成されている。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

発振周波数補正信号発生回路

【課題】発振周波数とは別の周波数を生成するための回路を別途設けることなく、発振周波数を補正することができるようにする発振周波数補正信号発生回路を提供する。

【解決手段】発振信号を互いに異なる遅延時間にて遅延させて複数の遅延信号を生成し、当該遅延信号の各々に基づくタイミングにて当該発振信号を1周期単位でサンプリングして周期毎のサンプル値群を生成し、互いに異なる時点の2つの測定対象周期における当該サンプル値群の一連のサンプル値を比較してその比較結果に応じて前記補正信号を生成する。

(もっと読む)

半導体装置

【課題】CMOSトランジスタによって構成されたVCOを備えた半導体装置において、発振信号の発振振幅のばらつきの抑制および低消費電力化を実現する。

【解決手段】VCO30は、CMOSトランジスタによって構成されたLCタンクVCOと、VCOの発振周波数帯域から一の発振周波数を選択するための周波数選択信号を生成する自動周波数選択回路42と、VCOの制御電圧を生成するPLL32と、周波数選択信号に基づいて差動型のMOSトランジスタのゲートに供給するバイアス電圧を調整するバイアス回路50とを備える。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

電圧制御発振回路及びPLL回路

【課題】制御電圧に対する周波数の変化量を自由に調整できる電圧制御発振回路及びPLL回路を提供する。

【解決手段】制御電圧に応じて容量成分が制御される可変容量素子Cv1、Cv2と、可変容量素子に直列に接続された直列容量素子Cs1、Cs2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子Cp1,Cp2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子Lとを有する電圧制御発振回路100において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されている。

(もっと読む)

温度特性調整データ生成方法

【課題】n(nは1以上の整数)次の関数で表現される温度特性を持った信号のn−1次の温度係数を調整する際に、n次の温度係数の影響を軽減し、且つコストの増大を抑えることができる、温度特性の調整データを生成する方法を提供する。

【解決手段】温度特性調整データ生成方法は、n(nは1以上の整数)次の関数で表現される温度特性を持った信号を生成する回路を有する半導体装置の温度特性を調整するデータ(803)を、プログラム処理装置(6、10)を用いて生成する方法であって、n+1よりも少ない数の温度における前記信号の値を、前記信号に関する目標値に所定の補正値を加えた値(601)に近づけるように温度特性を調整するデータを生成するデータ生成処理を含む。

(もっと読む)

低位相ノイズ電圧制御発振器

本発明の形態は、消費電力を低減し位相ノイズ性能を向上させるために、電流再使用技術を用いた低位相ノイズ発振器回路を含み、発振器回路は、第2のVCOに結合されている第1のVCOを備え、第1及び第2のVCOの出力は、コンデンサ等の受動素子に結合されている。第1及び第2のVCO両方の全体の消費電力は、単一のVCOの消費電力と略同じである。また、位相ノイズは、約3dBほど低減される。このため、発振器回路の消費電力を増加させることなしに、位相ノイズ性能が向上される。 (もっと読む)

MOSFETのソースバルク電圧を用いた信号処理ASIC用の温度補償RC発振器

温度補償CMOS RC発振回路は、抵抗と温度相関バイアス電流とを用いてソースバルク電圧を変化させて、温度に対するMOSFETの閾値電圧の変動を安定させる。この温度層間バイアス電流はまた、抵抗を流れる。温度が上昇すると、バイアス電流も増え、MOSFETのソースバルク電圧を上昇させる。上昇したソースバルク電圧は、高い温度にてMOSFETの閾値電圧を安定させるのを補助する。この発振器には省電力ロジックも組み込まれており、低い電力消費で高い周波数が得られる。本発明では、得られる発振器が低出力設計となってしまう高利得オペアンプや高速比較器はなく、他のシステムとともにシングルチップに組み込むことができる。 (もっと読む)

温度安定化された電圧制御発振器

【課題】温度安定化された電圧制御発振器を提供する。

【解決手段】セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a、310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370、380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b、320a、320bを含んでいる。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

発振器及び位相同期回路

【課題】十分に高い周波数帯域において、広帯域にわたって柔軟に発振周波数を調整すること。

【解決手段】信号線131は、電源から直流電圧Vdcが印加されると、電源に接続された始端を節とし、終端を腹とする4分の3波長の定在波を発生させる。ストリップ132−1〜132−nは、それぞれスイッチ133−1〜133−nを介してグランド層に接続されている。スイッチ133−1〜133−nは、切替制御部140による制御に従って、それぞれストリップ132−1〜132−nとグランド層との接続及び非接続を切り替える。スイッチ133−1〜133−nの接続及び非接続を切り替えることにより、擬似的に信号線131とグランド層の間の距離が調節され、伝送線路部130における実効誘電率が変化して、定在波の周波数を調整することができる。

(もっと読む)

デジタルPLL回路及び半導体集積回路

【課題】粗調整用と微調整用のコンデンサを切り替えて発振回路の発振周波数を調整する際に、粗調整区間に生じるサイクルスリップに起因して発振周波数可変範囲が狭くなるのを回避可能なデジタルPLL回路及び半導体集積回路を提供することである。

【解決手段】インダクタンス素子に並列接続される容量素子の数を変えて発振周波数が制御される発振回路4と、基準クロック及びその遅延クロックと発振回路出力とをデジタル位相比較し、その比較結果に基づいて容量素子の並列接続数を制御し、発振回路出力の位相を基準クロック位相に近づける制御をする位相比較部6とを具備し、容量素子は、インダクタンス素子に並列接続可能な所定容量の粗調整用コンデンサ43と、これに並列接続可能で粗調整用コンデンサの1/n容量を有し、粗調整時に所定数の微調整用コンデンサが1つの粗調整用として制御される複数の微調整用コンデンサ44を備える。

(もっと読む)

電圧制御発振器のための補償回路

【課題】電圧制御発振器のための補償回路を提供する。

【解決手段】電圧制御発振器(VCO)の電圧を制御するために使用され得る回路は、第1の比較器、第2の比較器、アキュムレータ、及び出力装置を備え得る。第1の比較器は、制御電圧が高電位側しきい値電圧より高い場合に第1のパルス信号を出力する。第2の比較器は、制御電圧が低電位側しきい値電圧より低い場合に第2のパルス信号を出力する。アキュムレータは、もし第1のパルス信号が受信されるならばスイッチ制御信号の値を増加させ、もし第2のパルス信号が受信されるならばスイッチ制御信号の値を減少させる。出力装置は、スイッチ制御信号の値に応じてVCOの制御電圧を補償する補償電圧を生成する。

(もっと読む)

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

1 - 20 / 56

[ Back to top ]