Fターム[5J081FF13]の内容

LC分布定数、CR発振器 (9,854) | 構成要素(発振用能動素子、周波数決定素子以外) (1,204) | 回路構成 (543) | デジタル回路 (86) | メモリ (34)

Fターム[5J081FF13]に分類される特許

1 - 20 / 34

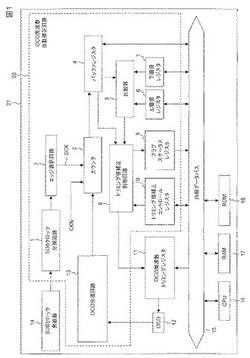

半導体装置

【課題】発振周波数変動の許容範囲を任意に設定可能にする。

【解決手段】半導体装置(21)は、トリミングレジスタ(11)に保持されたトリミング値によって発振周波数が変更される発振器(12)と、発振周波数を補正可能な補正回路(20)とを含む。上記補正回路は、上限値を設定可能な上限値レジスタ(6)と、下限値を設定可能な下限値レジスタ(7)と、発振周波数を分周するための分周回路(13)と、分周回路の出力をカウントするカウンタ(3)とを含む。さらに上記補正回路は、カウンタの出力を保持可能なバッファレジスタ(4)と、バッファレジスタの保持値が、上限値と下限値との間に入っているか否かを判別する比較器(5)と、その判別結果に基づいてトリミング値を補正するトリミング値補正制御回路(8)とを含む。ユーザは、上限値と下限値とによって、発振周波数変動の許容範囲を任意に設定することができる。

(もっと読む)

発振回路を有するマイクロコントローラ

【課題】複雑なバイアス回路を使用せず,抵抗の温度依存性を補償可能なMCU搭載に適したCR発振回路またはLC発振回路を提供する。

【解決手段】マイクロコントローラは,CPUと,CPUに供給するクロックを生成しクロックの周波数が周波数調整信号に応じて可変制御される発振回路と,温度を検知する温度センサと,温度センサにより検知される温度が所定温度変動したことに応答してCPUにより実行される周波数調整プログラムと,周波数調整信号と発振回路の発振周波数との関係を示す調整信号対周波数関係データと,温度と前記発振回路の発振周波数との関係を示す温度対周波数関係データとを格納するメモリとを有する。そして,周波数調整プログラムがCPUにより実行されることで,CPUが,温度対周波数関係データと調整信号対周波数関係データとに基づいて,温度センサにより検知される現在温度に応じて,発振回路の発振周波数を目標の周波数に制御する周波数調整信号を演算し,演算した周波数調整信号が発振回路に設定される。

(もっと読む)

発振器、半導体部品及び電子機器

【課題】複数の端子のうち一部の端子が使用されない場合においても好適に動作可能な発振器を提供する。

【解決手段】発振器1は、振動素子14と、振動素子14に電圧を印加して発振信号Outを生成する発振回路27と、発振回路27の出力部27aに接続されることにより発振信号Outを出力可能な端子5(Out1)及び端子5(Out2)と、出力部27aと外部機器(回路基板53を含む)との端子5(Out2)を介した導通状態の変化に応じた発振回路27の周波数の変化を補償する接続補償回路37とを有する。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路

【課題】自励発振回路周辺の状態変化による発振周波数の変化を抑えることができる周波数自動調整機能付自励発振回路およびそれを用いた半導体集積回路を提供する。

【解決手段】周波数自動調整機能付自励発振回路は、基準信号を生成する基準信号生成回路101bと、基準信号の周波数を調整する発振周波数調整回路101aとを有する自励発振回路101と、互いに特性の異なる1組の抵抗素子を含み、1組の抵抗素子の抵抗値の変化の違いにより自励発振回路101の周辺状態を検出し、検出された周辺状態を示す信号を出力する特性変動検出回路102_1と、特性変動検出回路102_1の出力信号に基づいて発振周波数調整回路101aによる周波数調整を制御する制御部103とを備える。

(もっと読む)

回路装置及び電子機器

【課題】無駄な電力消費やノイズの悪影響等を抑制できる回路装置及び電子機器等の提供。

【解決手段】回路装置は発振回路10とバッファー回路20を含む。バッファー回路20は、プリバッファーPBFと第1、第2の出力バッファーQBF1、QBF2を含む。第1のモードでは、第1の出力バッファーQBF1が動作イネーブル状態に設定され、第2の出力バッファーQBF2が動作ディスエーブル状態に設定される。第2のモードでは、第1の出力バッファーQBF1及び第2の出力バッファーQBF2が動作イネーブル状態に設定される。第1のモードでは、プリバッファーPBFの駆動能力が、第2のモードに比べて低い駆動能力に設定される。

(もっと読む)

補償機能付き電圧制御発振器およびこれを用いた電子鍵盤楽器

【課題】簡素な構成でVCOそのものを利用して個々のVCOの温度補償を含む直線性補償を行うこと。

【解決手段】制御部20は、2種類の電圧「V1、V2」をVCO10に供給し、その2種類の電圧「V1、V2」に対するVCO10の出力信号の2種類の周波数「f1、f2」を検出して、横軸を電圧(V)とし縦軸を周波数(f)とした場合の直線である「f=a・V+b(aは傾き、bは切片)」の係数(a、b)を求める。次いで、制御部20は、VCO10からの出力信号の周波数が「Fo」となる電圧「Vo」を「Vo=(Fo−b)/a」なる演算式によって求め、求めた電圧「Vo」をVCO10に供給する。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

車両制御システムおよび車載器

【課題】携帯機と車載器との間で無線通信を行うに際し、車載器に使用される振動子の発振周波数の温度ばらつきを軽減する。

【解決手段】受信IC22には車載器20の温度を測定する第2温度センサ27が内蔵されている。そして、補正部23は、携帯機10の第1振動子11および車載器20の第2振動子21の周波数温度特性のデータマップがそれぞれ記憶されており、受信IC22から携帯機10の温度を示す送信側温度情報を入力すると共に第2温度センサ27から車載器20の温度を示す受信側温度情報を入力し、送信側温度情報、受信側温度情報、およびデータマップに基づいて取得したオフセット値を第2振動子21に付加することで、第2振動子21の第2周波数を第1振動子11の第1周波数に近づける補正を行う。

(もっと読む)

発振回路及び電子機器

【課題】発振周波数が安定するまでに要する時間の短い発振回路及び電子機器を提供する。

【解決手段】周波数補正回路を有する共振回路と、前記共振回路の両端の間に接続された増幅回路とを備えた発振回路が提供される。前記周波数補正回路は、第1のコンデンサと、両端の電位が変動可能に前記第1のコンデンサと直列的に接続された第1のトランジスタと、を有することを特徴とする。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

半導体装置

【課題】周囲温度や外部電源電圧の変化による高速OCOに与える参照電圧および参照電流の変動を防止し、電源モジュールの回路面積が小さい半導体装置を提供する。

【解決手段】高速OCO10は、参照電流および参照電圧で定まる大きさの高速クロックを出力する。温度センサ5は、高速OCO10の周囲温度を検出し、電圧センサ4は、高速OCO10の動作電圧を検出する。電源モジュール12は、BGRを含み、BGRが出力する基準電圧に基づいて、参照電圧、参照電流、高速OCOの動作電圧を生成する。フラッシュメモリ8は、高速OCO10の周囲温度および動作電圧に対応する、参照電圧および参照電流のトリミングコードを定めたテーブルを記憶する。ロジック部13は、検出された周囲温度および動作電圧に対応する参照電圧および参照電流のトリミングコードに基づいて、参照電流および参照電圧の値を調整する。

(もっと読む)

半導体集積回路装置および発振周波数較正方法

【課題】発振器の発振周波数の較正作業を短縮することができる半導体集積回路装置および発振周波数較正方法を提供する。

【解決手段】DCO50と、温度に対して単調な特性を持って変化する電圧源20から得られる電位に応じたDCO50に設定すべき発振周波数の温度係数および発振周波数の絶対値を記憶する記憶部42と、を備えたことを特徴とする半導体集積回路装置。

(もっと読む)

高電圧振幅状態の下での電圧制御発振器(VCO)バッファに対するデバイス信頼性の向上

電圧制御発振器(VCO)バッファのための回路が説明される。回路は、VCOコアと接続されるVCOバッファの入力と接続された第1のキャパシタを含む。回路は、また、VCOバッファの入力と、p型金属酸化膜半導体電界効果(PMOS)トランジスタのゲートとに接続された第2のキャパシタを含む。回路は、さらに、第1のキャパシタと、PMOSトランジスタのゲートとに接続された第1のスイッチを含む。回路は、また、VCOバッファの入力と接続された第3のキャパシタを含む。回路は、さらに、VCOバッファの入力と、n型金属酸化膜半導体電界効果(NMOS)トランジスタのゲートとに接続された第4のキャパシタを含む。回路は、また、第3のキャパシタとNMOSトランジスタのゲートとに接続された第2のスイッチを含む。 (もっと読む)

スプリット遅延ライン発振器における装置、システム及び方法

【課題】安全なデータ伝送を行うスプリット遅延ライン発振器における装置、システム及び方法を提供すること。

【解決手段】安全なデータ伝送を行うスプリット遅延ライン発振器における本装置は、第1装置における第1の変調/復調ブロックを有し、その第1の変調/復調ブロックは、第1の可変遅延を設定し、第1の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第2装置における第2の変調/復調ブロックは、第2の可変遅延を設定し、第2の変調/復調ブロックを通過する共有キャリア信号の周波数を変調し、第1及び第2装置は、周波数変調された共有キャリア信号にデータを与えることで、共有する秘密情報を作成する。

(もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

発振器

【課題】内蔵するICチップの内容を外部から設定し、書き換えることで回路定数や回路方式あるいは分周数を実装機器の仕様に合せて切り換え可能とした融通性の高い発振器を提供する。

【解決手段】内蔵するICチップ3に発振回路と共に複数の回路定数や回路方式の回路、あるいは複数の分周数の分周回路を備えると共に、該ICチップに不揮発メモリの領域、あるいは分周回路領域を設け、発振器の回路定数や回路方式を当該不揮発メモリに外部から書き込んだデータで切り換える構成とした。

(もっと読む)

発振回路、及びこれを用いた無線受信回路、スイッチ装置

【課題】消費電力の増大と発振周波数調整に要する時間の増大とを低減しつつ、従来よりも発振周波数の調整精度を向上させることが容易な発振回路、及びこれを用いた無線受信回路、スイッチ装置を提供する。

【解決手段】パルス信号PWM1を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG1と、パルス信号PWM1を平滑して得られた直流電圧Vdc1を出力するローパスフィルタLPF1と、Vdc1を接続点P1に印加する配線25と、パルス信号PWM2を出力すると共にパルス幅の設定を受け付けるパルス生成部PWMG2と、PWM2を平滑して得られた電圧VLP2を出力するローパスフィルタLPF2と、VLP2を所定の比率に変換して直流電圧Vdc2として接続点P2に印加する電圧変換部CNV2と、接続点P1,P2間の電圧に応じた周波数の発振信号を生成する並列共振回路23を備えた。

(もっと読む)

VCOのキャパシタバンクのトリミングとキャリブレーション

技法は、電圧制御発振器(VCO)で使用されるキャパシタバンクに関連するキャパシタンスをトリミングするために開示される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。実施例では、キャパシタンスはそれぞれ複数の構成要素のキャパシタンスへサブ分割される。構成要素のキャパシタンスは、キャパシタバンクのステップのサイズをトリミングするために選択的にイネーブルされ、またはディスイネーブルされ得る。さらなる技法は、キャパシタバンクについてステップのサイズの誤差を最小化するためにトリミング可能なキャパシタンスをキャリブレートするために開示される。  (もっと読む)

(もっと読む)

1 - 20 / 34

[ Back to top ]