Fターム[5J081KK04]の内容

LC分布定数、CR発振器 (9,854) | 制御手段及び要因 (1,418) | 制御対象 (468) | 起動・停止 (24)

Fターム[5J081KK04]に分類される特許

1 - 20 / 24

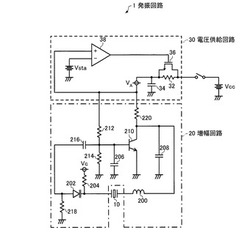

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】起動時の異常発振を抑えるとともに負荷の大きさによらず電源電圧の低電圧化が可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(水晶振動子10)と、共振子の一端から他端への帰還経路を有する増幅回路20と、電圧供給回路30と、を含む。電圧供給回路30は、電源電圧Vccが入力される時定数回路(抵抗32とコンデンサー34によるRC積分回路)を有し、電源電圧Vccが入力されてから時定数回路の時定数に応じて立ち上がるとともに増幅回路20の負荷によらず一定電圧となる駆動電圧VAを発生させ、駆動電圧VAを増幅回路20に供給する。

(もっと読む)

発振回路、発振器、電子機器及び発振回路の起動方法

【課題】インダクタンス素子に起因して発生する起動時の異常発振を効率的に抑えることが可能な発振回路、発振器、電子機器及び発振回路の起動方法を提供すること。

【解決手段】発振回路1は、共振子(SAW共振子10)と、増幅回路20と、スイッチング素子(NMOSスイッチ30)と、を含む。増幅回路20は、共振子の一端から他端への帰還経路、当該帰還経路に設けられている第1のインダクタンス素子(伸長コイル200)、当該帰還経路に設けられ、第1のインダクタンス素子と直列に設けられている可変容量素子(可変容量ダイオード202)、を有している。スイッチング素子は、第1のインダクタンス素子と可変容量素子とを含む回路部に対して並列に設けられている。

(もっと読む)

発振回路

【課題】コンパレータの消費電力を抑えつつ、高周波の発振出力の振幅を検出できる、発振回路を提供すること。

【解決手段】水晶振動子1を共振器として使用して発振出力Vxを生成する発振出力生成回路11と、発振出力Vxの振幅を検出する振幅検出回路15と、振幅検出回路15の出力Vsに応じて発振出力Vxをブーストするブースト回路16とを有する発振回路であって、振幅検出回路15は、発振出力Vxが入力される絶対値回路12と、絶対値回路12の出力を入力とするローパスフィルタ13と、ローパスフィルタ13の出力を入力とするコンパレータ14とを備えることを特徴とする、発振回路。

(もっと読む)

帰還型発振装置

【課題】発振開始時の立ち上がりを迅速に行うとともに、増幅素子に流れるバイアス電流を適正化すること。

【解決手段】準ミリ波帯域またはミリ波帯域を発振周波数帯域とする帰還型発振装置1において、入力端子から入力された信号を出力端子から出力する増幅素子(HEMT10)と、増幅素子の出力端子から入力端子に信号を帰還するための帰還回路(帰還回路40)と、増幅素子の出力端子と電源の間に挿入され、持続発振時に増幅素子に流れるバイアス電流を制限する抵抗素子(抵抗素子35)と、を有する。

(もっと読む)

圧電発振器

【課題】安定駆動に達するまでの時間を短縮した圧電発振器を提供する。

【解決手段】本発明の水晶発振器(圧電発振器)50は、水晶振動子(圧電振動子)1と、水晶振動子1に接続されて発振ループを形成して発振信号を出力する水晶発振部(圧電発振部)24、及び水晶発振部24の起動時に自励発振する自励発振部25により構成された発振回路と、を備え、自励発振部25の周波数が水晶発振部24の周波数よりも高く設定されている。尚、自励発振部25は、複数のコンデンサー(容量素子)C、インバーター5及び抵抗素子4により構成され、複数のコンデンサーCの合成容量の値を調整するために、調整手段6を備えている。

(もっと読む)

発振器、および発振を開始する方法

【課題】休止期間は消費電力を削減すると共に起動特性のよい発振器を提供する。

【解決手段】発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路412と、前記発振回路に第1の電流を供給する第1の制御可能電流源404と、発振回路に第2の電流を供給する第2の制御可能電流源408と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。

(もっと読む)

発振装置および角速度検出装置

【課題】振動子の起動を確実にし、安定して振動を維持する装置を提供する。

【解決手段】振動子12と、振動状態を検出する検出アンプ13と、振動情報を2値化してコンパレータ出力信号を出力する振幅比較器14と、制御発振器入力信号に応じて周波数が変化する電圧制御発振器151と、コンパレータ出力信号と比較信号との位相差信号を出力する位相比較器153と、位相差信号の低域成分を出力するループフィルタ154と、比較信号に対して予め定める位相差を有する位相シフト信号を出力する位相シフト器22と、位相シフト信号を入力する駆動アンプ11と、操作信号を出力する操作信号発生器21と、制御発振器入力信号として操作信号を選択し、制御発振器出力信号の周波数がキャプチャレンジの範囲となったときに、制御発振器入力信号として位相差情報信号を選択する操作切換器20と、を備える。

(もっと読む)

発振装置

【課題】発振周波数を決定する容量値の変化に伴う発振周波数の変動を抑え、且つ、位相雑音を低減することのできる発振装置を提供する。

【解決手段】発振装置は、ドレイン接地回路からなる第1増幅回路10と、第1増幅回路10の出力を増幅する、ゲート接地回路からなる第2増幅回路20と、第2増幅回路20の出力を第1増幅回路の入力に帰還させるコンデンサC1と、第1増幅回路10の入力側に設けられた共振器2と、共振器2及び第1増幅回路10内のトランジスタQ1に動作用のバイアス電圧を印加するバイアス回路12と、第2増幅回路20内のトランジスタQ2に動作用のバイアス電圧を印加するバイアス回路22とから構成される。この結果、位相雑音の発生を、単一のトランジスタからなるコルピッツ発振回路と同程度に抑えつつ、容量変化によって発振を起動できなくなったり、発振周波数が変動するのを防止できる。

(もっと読む)

二重正帰還電圧制御発振器

【課題】低供給電圧の性能でのマイクロ波帯域における電圧制御発振器の効率を向上させるための二重正帰還電圧制御発振器を提供する。

【解決手段】2つのコルピッツ回路20、21は第1正帰還ループを提供し、第1負抵抗と等価である。NMOS交差結合ペア回路30は、第2正帰還ループを提供し第2負抵抗と等価である。2つのコルピッツ回路20、21及びNMOS交差結合ペア回路30によって生成される2つの各負抵抗は、LCタンクの寄生抵抗に対して並列に接続されている。この為2つの各負抵抗は、LCタンクの寄生抵抗をオフセットする。2つの各負抵抗が生成されるので、低電圧の稼動時において、及び、直流電流の共有において、高い負抵抗が二重正帰還電圧制御発振器10によって生成される。この為、二重正帰還電圧制御発振器10は、より低い電力下で発振可能である。

(もっと読む)

クロックシステム

【課題】第2の発振回路の起動を待つことなく第1の発振回路の出力により高精度なクロック信号を得る。

【解決手段】クロックシステム1は、CR発振回路11、水晶発振回路12、及びトリミング回路15を含む。CR発振回路11は、内部回路17に供給されるクロックCLK1を生成する。水晶発振回路12は、CR発振回路11の発振周波数の調整に使用される。トリミング回路15は、CR発振回路11と水晶発振回路12の間の発振周波数差の検出結果に基づいて、CR発振回路11の発振周波数を調整する。

(もっと読む)

発振器

【課題】負荷容量に応じて最適な波形を出力可能な発振器を提供する。

【解決手段】発振回路12からの出力を、出力バッファ(前段出力バッファ14、出力バッファ22)を介して負荷回路に出力する発振器10であって、発振器10は、出力バッファ22の駆動能力を出力バッファから流れる電流に応じて調整可能なバッファ制御回路48を有する。ここで出力バッファ22は、発振回路12の後段に複数並列に接続されるとともに、バッファ制御回路48は、出力バッファから流れる電流に応じて出力バッファ22の稼動数を調整する信号を出力バッファ22に出力することにより出力バッファ22の駆動能力を調整している。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

静磁波発振装置

【課題】

発振周波数の可変幅が大きく、信号固定迄の引込み時間が早い静磁波発振装置を提供する。

【解決手段】

磁束密度により共振周波数が変化する共振器5と、該共振器と対向する位置にある永久磁石6と、該永久磁石を囲むコイル9,11とを具備し、前記共振器と前記永久磁石の間には空間7が形成され、該空間に強磁性体の金属板16が設けられ、該金属板は前記永久磁石と当接される。

(もっと読む)

発振器、および発振を開始する方法

発振信号がコールドスタートからの規定の定常状態条件に達する時を早める回路を含んでいる発振信号を生成するための装置。装置は、発振信号を生成するための発振回路と、発振回路に第1の電流を供給する第1の回路と、発振回路に第2の電流を供給する第2の回路と、を含み、第1および第2の電流は、発振信号が規定の定常状態条件に達するための時間分を縮小するのに適している。装置は、1以上の通信チャネルを確立するために低い負荷サイクルパルス変調を用いる通信システムに有益であるかもしれず、それによって装置はパルスのほぼ始めで発振信号を生成し始め、パルスのほぼ終わりに発振信号を終了する。  (もっと読む)

(もっと読む)

発振回路及び半導体装置

【課題】本発明は、発振回路及び半導体装置に関し、電源投入後、リセット後、スタンバイ状態からの復帰後のMCUの処理の高速化と低消費電力化を両立することを目的とする。

【解決手段】第1の発振回路と、第1の発振回路より長い発振安定時間を有する第2の発振回路と、第2の発振回路の発振安定時間の経過を示す安定信号を出力する信号生成回路と、選択信号に基づいて第1及び第2の発振回路の出力の一方を選択出力するスイッチ回路と、抑止信号に基づいて第2の発振回路の起動を抑止する抑止回路とを備え、第1及び第2の発振回路が同時に起動されてスイッチ回路により第1の発振回路の出力が選択出力された後に第2の発振回路の出力に切り替えられるモードと、第1の発振回路が起動されて抑止回路により第2の発振回路が起動されずスイッチ回路により第1の発振回路の出力のみが選択出力されるモードを有するように構成する。

(もっと読む)

発振器

【課題】発振周波数毎の出力信号の電力及びC/N比の変動を抑制する発振器を提供すること。

【解決手段】

本発明は、それぞれ異なる発振周波数の発振信号を出力する複数の発振部11〜1nと、複数の発振部11〜1nのそれぞれの出力が結合し、出力端子Toutの出力インピーダンスに対応する特性インピーダンスを有する伝送線路15と、伝送線路15と出力端子Toutとの間に接続されているローパスフィルタ18と、を具備する発振器である。

(もっと読む)

発振器

【課題】発振周波数変更機能を備えた発振器において、不揮発性メモリからデータを読み出す際に発振周波数が変更されることなく安定的に読み出すことができる。

【解決手段】LSIの外部に設けられた不揮発性メモリ15に、発振回路13から発振されるクロック信号の周波数を変更するための周波数設定値が記憶されており、その周波数設定値が、発振回路13から発振される初期設定された周波数のクロック信号によって読み出されると、ダミーレジスタ11に格納される。不揮発性メモリ15からデータが全て読み出されてロード動作完了信号が出力されると、ダミーレジスタ11から記憶レジスタ12へ周波数設定値が格納され、発振回路13の発振周波数が周波数設定値とされる。

(もっと読む)

差動発振装置及び変調器

【課題】差動発振装置において発振開始時から二つの出力端子から出力される出力信号の位相が反転するまでの時間を短縮すること。

【解決手段】一方のトランジスタ105の端子に外部入力端子を有しスイッチ回路104を有する差動発振部103と、前記差動発振部103の発振開始と発振停止を制御する第一の制御信号を生成する第一の制御信号発生回路101と、前記差動発振部103の一方のトランジスタ105の端子に入力する第二の制御信号を生成する第二の制御信号発生回路102とを有する差動発振装置において、第二の制御信号によって二つのトランジスタ105,106に流れるコレクタ電流の位相関係を決めることで、発振開始時から二つの出力端子から出力される出力信号の位相は逆相となる。

(もっと読む)

電圧制御発振器

【課題】 高速起動性、低位相雑音性および低消費電力特性のすべてを充足できる電圧制御発振器を提供する。

【解決手段】 バイアス部は、電流源と、電流源に直列形態に接続される第1トランジスタと、第1トランジスタにカレントミラー接続され、制御電圧に応じて所望の周波数の発振信号を生成する本体部にバイアス電流を供給する第2トランジスタと、第1および第2トランジスタの制御端子間に接続され、抵抗素子として機能するスイッチ回路と、第2トランジスタの制御端子に接続される容量素子とを備えて構成される。電流源は、電圧制御発振器の起動状態時に第1トランジスタに対する電流供給動作を実施し、電圧制御発振器の定常状態時に第1トランジスタに対する電流供給動作を停止する。スイッチ回路は、電圧制御発振器の起動状態時にオンし、電圧制御発振器の定常状態時にオフする。

(もっと読む)

間欠動作回路及び変調装置

【課題】小回路規模、低消費電力で、立ち上がりと立ち下がりの速い出力波形を得ることができる間欠動作回路を提供すること。

【解決手段】能動回路106と、能動回路106の動作開始と動作停止を制御する第1の制御信号S1を生成する第1の制御信号生成回路101と、能動回路106にリンギング振動を起こさせ、かつ、そのリンギング振動の周波数と振幅値を制御することができる第2の制御信号S2を生成する第2の制御信号生成回路102と、能動回路106からリンギング振動と安定振動が継続して出力されるように、第1及び第2の制御信号S1、S2の能動回路106への入力タイミングを調整するタイミング調整回路103とを設けるようにする。

(もっと読む)

1 - 20 / 24

[ Back to top ]