Fターム[5J106CC02]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | アナログ発振回路 (130)

Fターム[5J106CC02]に分類される特許

1 - 20 / 130

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。更に前記温度検出値に基づいて、OCXOの設定周波数を補正し、雰囲気温度が基準温度からずれたことによる周波数の変動分を補償するようにする。

(もっと読む)

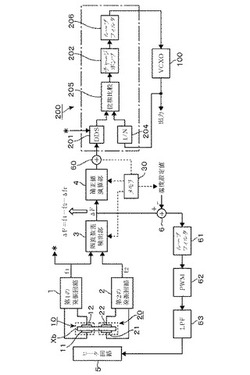

レベル調整装置

【課題】 基準発振器、VCO、位相比較器の純度が低くても位相雑音特性を良好にする。

【解決手段】 基準発振器28aが発振する基準周波数frefをBS放送波のチャンネル間隔とされる38.36MHzに設定する。そして、中間周波数を282.28(=7×38.36+13.76)MHzとした場合は、1049.48MHzのチャンネル周波数とされるBS−1チャンネルがアサインされるBS−IFレベル調整ユニット10では、局部発振器28の出力周波数foutが767.2MHzになり、分周器28eの分周数Nを20とすればよい。基準周波数frefを38.36MHzと高くすることができるため、局部発振器28の位相雑音特性が良好になる。

(もっと読む)

CR発振回路およびその周波数補正方法

【課題】基準周波数信号を用いることなく、温度変動、電源電圧変動および回路定数のばらつきにかかわらず高精度な発振周波数を得る。

【解決手段】出荷検査時において、発振動作の環境温度と電源電圧を変化させながら発振周波数が目標周波数に一致するのに必要な抵抗5の抵抗値を順次求め、環境温度と電源電圧に対して当該抵抗値を対応付けたデータテーブルをメモリ18に記憶する。CR発振回路の実際の使用状態では、制御回路17は、所定の制御周期ごとに温度検出回路15と電源電圧検出回路16から電圧Va、Vbを入力しA/D変換する。メモリ18に予め記憶されたデータテーブルから電圧Va、Vbに対応した抵抗5の抵抗値を読み出し、抵抗5の抵抗値Rが当該読み出した指定値に等しくなるようにスイッチ7a〜7cを切り替える。

(もっと読む)

位相同期回路およびその制御方法

【課題】ばらつき条件(温度、電源電圧、経年変化等)下の安定動作を補償しかつ低ゲインの電圧−周波数特性を実現できる位相同期回路を提供する。

【解決手段】バラクタアレイを有するVCO101と、VCO101の特性をモニターするモニター回路102と、モニター結果に応じてバラクタアレイに供給するオフセット量を切り替えるオフセット発生回路103とを備える。ばらつき条件下のVCOの特性をモニターした結果からバラクタアレイのオフセット量を調整することで、位相同期回路の動作不良を防ぐ。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

発振器及び半導体集積回路装置

【課題】発振器の出力端子間に直接寄生する容量Cparaの大きさが無視できない場合でも温度特性を補償する発振器及び発振器を内蔵する半導体集積回路装置を提供する。

【解決手段】インダクタンス素子Lと、容量素子Cと、増幅器30と、をそれぞれ第1の端子と第2の端子との間に並列に接続し、インダクタンス素子と容量素子とによって生じる共振を増幅器によって増幅し、第1の端子と第2の端子とから出力する発振器であって、第1の端子と第2の端子との間にインダクタンス素子の寄生抵抗RLより抵抗値の大きな第1の抵抗素子Rcが第1の端子と第2の端子との間に容量素子と直列に接続されている。

(もっと読む)

位相比較器

【課題】位相比較器において、2つのフリップ・フロップの出力信号がリセットされるまでの遅延時間によって両出力信号に現れる余分な成分を取り除き、それによって生じる種々の問題を解決すること。

【解決手段】本発明の位相比較器は、比較対象の2つの入力信号が入力されて第1と第2の出力信号を出力する第1と第2のフリップ・フロップと、第1と第2の出力信号を論理積処理してリセット信号を出力する論理積処理回路と、論理積処理回路と同じ遅延時間を持ち第1遅延信号と第2遅延信号を出力する第1と第2の遅延手段と、第1遅延信号と第2遅延信号がそれぞれ入力されるとともにリセット信号によってリセットされて第3と第4の出力信号を出力する第3と第4のフリップ・フロップとを備え、位相が進んだ方の入力信号を遅延させた第1もしくは第2遅延信号が入力される第3もしくは第4のフリップ・フロップの出力信号に位相比較出力信号が出力さるように構成されている。

(もっと読む)

電子機器およびクロック補正方法

【課題】 RC発振器によりクロック信号を生成するシステムにおいて、クロック信号の周波数を大きく変動させずに補正して規定の範囲に保つことのできる電子機器およびクロック補正方法を提供することにある。

【解決手段】 RC発振器の抵抗または容量の設定を切り替えてクロック信号の周波数を複数段階に変更可能な周波数変更手段と、この複数段階の変更量を表わしたトリミングテーブルを記憶する記憶手段と、周波数変更手段の設定を切り替えてクロック信号の周波数を補正するクロック補正制御手段とを備えた電子機器およびそのクロック補正方法である。そして、クロック補正制御手段は、トリミングテーブルのデータに基づき、クロック信号の周波数を補正前の周波数から規定の周波数へ次第に近づいていくように周波数変更手段の設定を切り替えて(S7,S8)、クロック信号の周波数を補正する。

(もっと読む)

位相同期回路および無線受信装置

【課題】サブサンプリングPLLの利点を保持したまま、フラクショナル分周を実現する。

【解決手段】電圧制御発振器は、制御電圧に応じて周波数が制御される第1信号、および前記第1信号と逆相の第2信号を生成する。サブサンプリング位相比較器は、基準信号の周期毎に、前記第1信号および第2信号の電圧を標本化して、第1標本化電圧および第2標本化電圧を生成する。電流生成回路は、供給電圧に応じて第1電流信号を生成する第1のチャージポンプと、供給電圧に応じて前記第1電流信号と反対符号の第2電流信号を生成する第2のチャージポンプとを有する。セレクト制御手段は、前記第1および第2標本化電圧を前記第2および第1チャージポンプにまたはこれと反対に供給する第1、第2供給モードを選択的に実行する。ループフィルタは、前記第1、第2の電流信号の合成電流信号を平滑化して、前記電圧制御発振器に与える前記制御電圧を生成する。

(もっと読む)

MEMSデバイス、電子機器

【課題】実装面積やコストを抑え、起動時間を短縮し、周波数精度の高いクロックも出力できるMEMSデバイス等を提供する。

【解決手段】 第1のクロック信号400と第2のクロック信号402の少なくとも一方を出力するMEMSデバイス100であって、同一の基板上に設けられた第1のMEMS共振子302を有する第1のMEMS発振器300と第2のMEMS共振子322を有する第2のMEMS発振器320とを含み、第1のMEMS発振器の共振周波数である第1の共振周波数と、第2のMEMS発振器の共振周波数である第2の共振周波数とは略一致し、第1のMEMS共振子のQ値と第2のMEMS共振子のQ値とは異なり、第1のMEMS発振器は、第1の共振周波数を周波数とする第1のクロック信号を出力し、第2のMEMS発振器は、第2の共振周波数を周波数とする第2のクロック信号を出力する。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

電圧制御発振回路及びPLL回路

【課題】制御電圧に対する周波数の変化量を自由に調整できる電圧制御発振回路及びPLL回路を提供する。

【解決手段】制御電圧に応じて容量成分が制御される可変容量素子Cv1、Cv2と、可変容量素子に直列に接続された直列容量素子Cs1、Cs2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続された並列容量素子Cp1,Cp2と、可変容量素子と直列容量素子とから構成される直列回路に並列に接続され、誘導成分を構成する誘導素子Lとを有する電圧制御発振回路100において、直列容量素子及び並列容量素子は、各々その容量成分を切り換え可能な構成されており、直列容量素子の容量成分及び並列容量素子の容量成分を切り換えることにより、制御電圧に対する発振周波数の変化量が調整されている。

(もっと読む)

スペクトラムアナライザおよびスペクトラム分析方法

【課題】フラクショナルスプリアスに起因するスペクトル波形の表示を阻止しつつ、迅速な測定を可能にする。

【解決手段】指定されたスパン(分析対象周波数範囲)の幅値が境界値より大きい場合、基準信号周波数を所定の基準値に設定し、RBW(分解能帯域幅)より狭いループフィルタ帯域を選択することによってフラクショナルスプリアスをRBWの内側にしてスペクトラム波形として表示されないようにする。また、指定されたスパンの幅値が境界値より小さい場合、基準信号周波数を基準値から所定値シフトさせ、そのシフト量と分周比の整数部との積に等しい分だけVCO出力信号の主信号成分とフラクショナルスプリアスとの周波数差を拡大させ、その拡大した周波数差より狭い範囲でループフィルタの帯域をRBWが含まれる領域に応じて設定してフラクショナルスプリアスのレベルを抑圧する。

(もっと読む)

電圧制御発振器及びそれを備えた無線通信装置

【課題】バイアス抵抗の抵抗値を大きい値に維持して省電力化及び発振効率の向上を図りつつ、広帯域の変調信号に対応することができる電圧制御発振器及びそれを備えた無線通信装置を提供すること。

【解決手段】

印加される電圧に応じて静電容量値が変化するバラクタM1,M2を有し、当該バラクタM1,M2に制御端子T2を介して印加される制御信号に応じて共振周波数が変化する共振回路30と、共振回路30と並列に接続された負性抵抗回路40とを備え、制御信号の逆相信号が制御端子T3を介して印加されるキャパシタC3、C4をバラクタM1,M2に接続した。

(もっと読む)

原子発振器

【課題】設計の自由度を向上させることにより比較的簡易な構成の原子発振器を提供すること。

【解決手段】原子発振器1は、光源10、光検出手段30、制御手段40を含む。光源10は、中心周波数をf1として周波数がΔfずつ異なる複数の周波数成分を有する第1の光と、中心周波数をf2として周波数がΔfずつ異なる複数の周波数成分を有する第2の光と、を発生させる。光検出手段30は、アルカリ金属原子を透過した第1の光及び第2の光を含む光の強度を検出する。制御手段40は、光検出手段30の検出結果に基づいて、第1の光の所定の周波数成分と第2の光の所定の周波数成分の周波数差がアルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数に等しくなるように制御する。第1の光の中心周波数f1と第2の光の中心周波数f2の周波数差は、アルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数と異なる。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

発振回路

【課題】 起動直後から安定した振動波形を有する出力信号を得ることができる発振回路を提供する。

【解決手段】 発振回路1Aは、入力電圧に基づいて振動波形を有する振動出力電圧を出力する主発振回路2Aと、主発振回路2Aの振動出力電圧に応じた出力信号と予め定められた周波数を有するクロック同期信号SYNCとが入力され、出力信号及びクロック同期信号SYNCの位相差に応じた電圧を出力する位相比較器3と、位相比較器3の出力電圧を平滑化する第1ローパスフィルタ4と、第1ローパスフィルタ4の出力電圧が基準電圧Vref1以上の場合、第1ローパスフィルタ4の出力電圧を主発振回路2Aに入力し、第1ローパスフィルタ4の出力電圧が基準電圧Vref1より低い場合、基準電圧Vref1を主発振回路2Aに入力する切替回路5Aとを備えている。

(もっと読む)

通信ネットワークにおける使用のための発振器、周波数シンセサイザ及びネットワークノード

本開示は、周波数シンセサイザ内での周波数の生成における使用のための発振器であって、少なくとも1つの巻きを伴って金属線ループを形成する第1の誘導素子と、前記第1の誘導素子との間で第1の共振回路を形成するように構成され、少なくとも1つの第1の接続端子を通じて前記第1の誘導素子と接続される第1の容量回路と、を備え、前記第1の容量回路は、少なくとも1つの容量素子、並びに、発振を確立し及び維持するように構成される電子コンポーネント配置を含む、発振器に関する。当該発振器は、少なくとも1つの容量素子と電子コンポーネントの配置とを含む第2の容量回路が、前記第1の誘導素子との間で第2の共振回路を形成するように構成され、前記第1の容量回路の前記第1の接続端子に対して前記第1の誘導素子の反対側に位置する少なくとも1つの第2の接続端子を通じて前記第1の誘導素子と接続されることと、前記第1及び第2の共振回路が実質的に同等の周波数にチューニングされることと、を特徴とする。本発明は、周波数シンセサイザ及び通信ネットワーク内での使用のためのネットワークノードにも関する。 (もっと読む)

1 - 20 / 130

[ Back to top ]