Fターム[5J106CC19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 複数の発振回路・VCO (166)

Fターム[5J106CC19]の下位に属するFターム

複数のループVCO (43)

Fターム[5J106CC19]に分類される特許

101 - 120 / 123

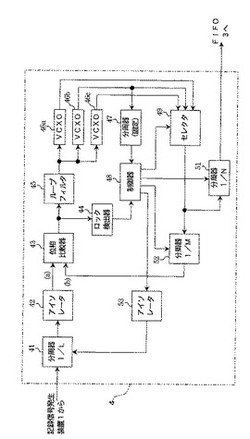

PLL回路

【課題】 複数種類の異なった記録モードで記録するための記録信号が入力され、入力信号に含まれる雑音成分を取り除いた純度の高い信号を出力するPLL回路を実現する。

【解決手段】 入力信号を1/Lにして第1分周器41から第1周波数信号を出力し、入力信号に対応するマスタクロック信号を発振器46aで発振し、マスタクロック信号の周波数を1/Mにして第2周波数信号を第2分周器52から出力し、第1周波数信号と第2周波数信号との位相差信号を位相比較器43から出力し、第1周波数信号と第2周波数信号とが一致しているか否かをロック検出器44で検出し、一致しない場合には第1分周器のL及び第2分周器のMを可変させ、一致した場合にはL及びMを固定させる制御信号を制御回路48から出力し、マスタクロック信号を1/Nにして真の信号成分を第3分周器から出力するようにしたPLL回路を構成した。

(もっと読む)

ディジタル情報記録再生装置およびディジタルフェーズロックドループ回路

【課題】ユーザ領域で用いるトラッキング用位相比較器では、PLLの引込み範囲が狭く、所定長のRUN−IN領域だけでは、PLLの引込みが完了できない課題があった。

【解決手段】ゼロクロス検出手段と、ゼロクロス検出手段の通過タイミングに合わせて動作を開始しカウント値を出力する周期カウンタと、前記ゼロクロス検出手段から出力された通過方向情報と前記カウント値から、再生信号がゼロクロスするタイミングを予測し、初期位相誤差を出力するアクイジション用位相誤差検出器を備える。ゼロクロス検出手段は、プリアンブル領域に含まれる特定パターンの立上り又は立下りエッジのゼロクロス点を検出し、検出されたゼロクロス点から所定周期の周期カウンタを動作させ、プリアンブル領域の特定パターンから予測されるゼロクロス点を予測し、アクイジション用位相誤差を出力する。

(もっと読む)

クロック信号の生成及び分配装置

【課題】 数ギガヘルツ以上の高周波域においても、高精度のクロック信号を生成し分配可能なクロック生成分配装置を提供すること、及び20GHzに達するような高周波域においても、各電圧制御発振器が同一位相で発振し、希望する周波数のクロック信号が生成でき、高周波クロック信号を、より安定にチップ内の各部に分配する分散VCO型クロック生成分配装置を提供すること。

【解決手段】 各電圧制御発振器としてLC共振型電圧制御発振器を採用し、さらにその発振ノード間の接続配線のインダクタ成分を相対的に小さくして、あるいは、LC共振発振器を注入同期により同期して発振させることにより、各LC共振型電圧制御発振器が安定して同一位相で発振するようにする。

(もっと読む)

多重周波数源システムのためのオフセット信号位相調整

オフセット信号位相調整を用いる同調可能な多重周波数源システムが、第1の周波数源と、位相遅延素子と、第1の周波数源と同時に動作するように構成された第2の周波数源とを含む。第1の周波数源は、基準入力信号を受け取るように結合された入力と、第1の周波数源信号を提供する出力とを含む。位相遅延は、入力基準信号を受け取るように結合された入力と、出力とを含み、位相遅延素子は、入力基準信号に既定の位相遅延を適用して位相遅延入力信号を生み出すように動作する。第2の周波数源は、位相遅延入力信号を受け取るように結合された入力と、第2の周波数源信号を提供する出力とを含む。 (もっと読む)

送受信機の周波数合成の方法および装置

【課題】受信機参照周波数信号から受信機周波数信号を合成するように構成されるプライマリ周波数シンセサイザを提供し、フラクショナル−N分周を使用することにより受信機周波数信号から送信機周波数信号を合成するように構成されるオフセット周波数シンセサイザを提供することに基づく、送受信機の周波数合成に関する方法および装置である。かかる構成が、要求される受信および送信周波数間の非整数のデュプレックス距離を可能とする。プライマリ周波数シンセサイザは、フラクショナル−N周波数シンセサイザとして作動されることもできる。これは受信機周波数信号が受信機参照周波数信号との非整数の関係を有することもできることを意味する。フラクショナル−N周波数合成と共に作動するようにプライマリおよびオフセット周波数シンセサイザを構成することが、プライマリおよびセカンダリ周波数シンセサイザの独立した周波数の調整/最適化を許容する。 (もっと読む)

クロック生成回路及びそれを備えた半導体装置

【課題】供給される信号と帰還信号が一定の位相になるよう負帰還により調整を行う回路において、供給される信号がない場合、外部からのノイズにより、クロックの周波数が変動し通信に不具合が生じる問題を課題とする。

【解決手段】PLL回路と、発振回路とを有し、PLL回路からの信号と、発振回路からの信号との出力を切り替えるためのスイッチが設け、受信信号が無い場合にPLL回路との接続を発振回路との接続に切り替える。

(もっと読む)

PLL回路

【課題】小規模な制御回路により、出力クロックの位相変動を抑圧するPLL回路を得る。

【解決手段】出力クロックの位相変動を抑圧するPLL回路において、入力信号とVCOの出力クロックとの位相差を検出する位相比較手段2と、前記位相比較手段の出力を入力とし低周波数成分のみを通過させるLPF3と、前記LPFの出力を入力としPLL回路の定常位相誤差を検出する定常位相誤差検出手段5と、前記定常位相誤差検出手段の出力を入力としVCO発振周波数オフセット制御電圧を生成するVCO発振周波数オフセット制御手段6と、前記LPFの出力を入力とするVCO発振周波数制御端子および前記VCO発振周波数オフセット制御手段の出力を入力とするVCO発振周波数オフセット制御端子を有するVCO4とを備える。

(もっと読む)

通信用半導体集積回路および無線通信装置

【課題】 送信信号の変調および受信信号の復調やアップコンバート、ダウンコンバートの機能を有する通信用半導体集積回路(高周波IC)およびベースバンド回路を備えた無線通信装置におけるトータルの消費電力を低減する。

【解決手段】 送信信号の変調送信信号の変調および受信信号の復調および受信信号の復調処理に用いられる基準クロック信号を生成するクロック生成回路(260)を内蔵した通信用半導体集積回路(高周波IC)において、前記クロック生成回路には、振動子が接続されることにより該振動子の固有振動数と印加される制御電圧とに応じた周波数で発振する電圧制御型発振回路(VCXO262)を設け、該電圧制御型発振回路は、ベースバンドICから供給されるディジタル周波数制御情報を内部のDA変換回路(270)で変換した結果を前記制御電圧としてその電圧に応じた周波数で発振するように構成した。

(もっと読む)

周波数差補償器

【課題】 二つの電圧制御型発振器のそれぞれの発振波形を位相は同期せずに周波数のみを等しくするような周波数差補償器を提供する。

【解決手段】 入力制御端子から得る制御電圧Vcntに応じた周波数fで発振する発振器01と、発振周波数fに依存した直流電圧値Vfを出力する周波数変換器02と、一定周波数frで発振する発振器03と、周波数frに依存した直流電圧値Vfrを出力する周波数変換器04と、周波数変換器02及び周波数変換器04の各出力値の差分に基づき出力値Vcmpを出力する比較器05と、出力値Vcmpに基づいて発振周波数Vfが発振周波数Vfrと等しくなるように入力制御端子へ制御電圧Vcntを出力する制御器06から構成される周波数差補償器とした。

(もっと読む)

2重系クロック位相同期装置および通信装置

【課題】 歪みのないクロックを出力できる2重化クロック位相同期装置、およびこれを用いた通信装置を提供することである。

【解決手段】 無線基地局10は、外部から受信した信号から抽出されたクロックに位相同期した基準クロックを生成するクロック位相同期部12a,12bを備えた通信装置である。クロック位相同期部12a,12bは、位相ロックループ回路を2重化したものであり、待機系は運用系よりも速い応答速度で動作する。こうした構成によって、運用系と待機系との間の位相差が少なくなり、系の切替が起こったとしても、出力クロックに歪みが生じることがなくなる。

(もっと読む)

VCO装置

テレビジョン放送受信機等の無線装置に用いられるVCO(電圧制御発振回路)装置に関する。発振周波数が広帯域にわたり、かつ低消費電力化が実現できるVCO装置を提供する。VCO回路群(4)は、周波数制御電圧端子(8)に印加される制御電圧(Vt)に応じた周波数の信号を発振する。LO信号選択手段(3)はVCO回路群(4)の中から所望の出力信号を選択する。PLL(6)は、LO信号選択手段(3)で選択された局部信号(fvco)を分周して基準信号との位相を比較し位相差から変換した信号を出力する。ループフィルタ(7)は、PLL(6)の出力信号を平滑して周波数制御電圧である制御電圧(Vt)を出力し、LO信号選択手段(3)で選択された局部信号を高周波信号処理手段(1)へ出力する。  (もっと読む)

(もっと読む)

2パイ・スリップ検出を用いて位相同期ループ(PLL)シンセサイザを粗調整するためのシステムおよび方法

VCOの周波数と基準周波数との間の位相差を決定し、VCOの周波数と基準周波数との位相差が2πラジアン以上の場合に誤差信号を出力する位相周波数検出器(PFD)を有する位相同期ループ(PLL)シンセサイザ(200)において、少なくとも1つの電圧制御発振器(VCO)(211)を粗調整するためのシステムに関する。続いて、PFDに生成された誤差信号の数を追従するために、監視装置(215)が用いられる。監視装置の回路が所定のレベルに到達する場合、VCOの自走周波数が粗調整され得る。本発明によって、回路の動作に影響を与える動作因子にかかわらずPLLのVCOが動作レンジに留まることが可能なようにPLLを粗調整することを可能とする、大きな利点が示される。  (もっと読む)

(もっと読む)

PLLシンセサイザ及びこれを用いたマルチバンド無線機

【課題】使用周波数帯に応じて発振器を、また使用通信システムに応じて後段の変復調回路を切り換えて、発振器個数を減らし後段の変復調回路を共通化する。

【解決手段】複数の周波数帯,通信システムのモードで使用するため第1の発振器100と第2の発振器101の出力に第1のスイッチ回路102を設けて、第1,第2,第3の分周器103,104,105の分周信号を選択する。第1,第2の増幅器107,108の前段に第2,第3のスイッチ回路122,123を設け、信号を通信システムのモードに応じて選択し、第1,第2の増幅器107,108に入力して増幅する。この出力を第1,第2のミキサ109,111で通信システムのベースバンド信号と合成する。合成信号を第3,第4の増幅器110,112で増幅して出力する。各スイッチによって、所定モードの周波数帯,通信システムに応じた回路を選択することにより共通化する。

(もっと読む)

無線通信システム

【課題】 従来のPLL回路においては、分周比の切替え後可変分周器の出力(帰還側パルス)の最初の立上がりが基準側分周器の出力(基準側パルス)の立上がりよりも早くなるか遅くなるかは、一義的に決まっておらず、分周比の切替えタイミングに依存してしまい、周波数引込み時間が変動するという問題点があった。

【解決手段】 発振系回路から供給される局部発振信号の周波数は、フィルタからの出力電圧に従って変更され、アンテナから受信される信号と上記局部発振信号とを合成する受信系回路と、第2の制御信号に応答して、上記フィルタに所定の電圧をセットする設定手段と、上記第1の制御信号を生成し、上記発振系回路から供給され上記第1の周波数から上記第2の周波数へ変更される局部発振信号の変化に応じて上記第2の制御信号を生成する制御手段とを含むことようにした。

(もっと読む)

PLL回路

【課題】位相比較器で検出の位相誤差をループフィルタに入力/遮断する信号断接手段を備え、CVラインが暴れる範囲では遮断するように信号断接手段を制御し、CVラインの暴れをカットしてループフィルタの入出力電圧の応答遅延を改善したPLLを提供する。

【解決手段】PLL回路100は、基準周波数信号Fを発生の基準周波数信号発生器1と、分周器9で分周された信号と基準周波数信号Fの位相を比較の位相比較器2と、位相比較器2で検出の位相誤差εをループフィルタ4に入力/遮断する信号断接手段3と、位相比較器2で比較の位相誤差εを積分するループフィルタ4と、制御電圧vに基づいて発振周波数fが制御されるVCO(電圧制御発振器)−A5と、VCO(電圧制御発振器)−B6と、分周器9への分周比の設定及び信号断接手段3を制御のCPU(制御手段)8と、VCOA5、B6で発振の発振信号周波数fを所定の分周比で分周の分周器9とで構成。

(もっと読む)

位相同期発振器

【課題】周波数比較機能を有さない位相比較器を用いた場合において、確実に周波数引き込みが可能であって、確実にロックはずれを検知できる位相同期発振器を提供する。

【解決手段】周波数比較機能を有さない位相比較器と電圧制御発振器とを有するメインPLL回路と、電圧制御発振器からの周波数を精度良くモニターするクオリファイPLL回路と、モニターした周波数が所定範囲からはずれると、固有周波数を有する振動子を用いた固定周波数の発振器に電圧制御発振器を同期させるスターターPLL回路とを備える。

(もっと読む)

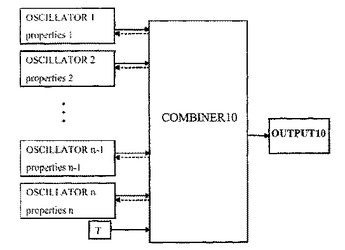

周波数合成器及びその動作方法

【課題】 シグマデルタ変調器を共有して、チップで占める面積を減少させることができる受信及び送信用の分数分周位相固定ループを利用した周波数合成器及び周波数合成方法を提供する。

【解決手段】 CDMA技術等を利用した無線移動通信で、送信チャンネル周波数と受信チャンネル周波数とは一定の間隔を維持する。これを利用して、基準周波数を出力するカウンタの値を調節して、周波数合成器を構成する送信用と受信用の分数分周位相固定ループの小数分周比を同一に維持させると、シグマデルタ変調器と基準周波数を決定するカウンタの数を一つに減少させることができる。従って、周波数合成器のチップ面積を大幅に減少させ、消耗電流量も減少させることができる。

(もっと読む)

PLL回路

【課題】 複数の発振帯域を有するVCO、又は異なる発信帯域を有する複数のVCOを備えたPLL回路において、設定した発振周波数に最適なVCOを選択完了するまでに要する時間を短縮すること。

【解決手段】 PLL回路の各出力周波数に対応する最適なVCOを予め記憶回路11に記憶しておき、このデータを利用してPLL回路の出力周波数が変化した時に最初に選択するVCOを決定する。また、各出力周波数に対応する最適なVCOは、当該出力周波数の選択完了後に書き換えることができるようにする。また、当該出力周波数に対応するVCOデータの代替として、前後の出力周波数のデータを利用する。また、コンパレータの出力を利用してVCOの制御電圧の動きを観測することにより、選択しているVCOの可否を判断するまでの時間を短縮する。

(もっと読む)

基準周波数発生装置

【課題】 障害時に現用系原子発振器から予備系原子発振器に切り替える際の不整合を簡易な構成で防止する基準周波数発生装置を提供する。

【解決手段】 原子の共鳴周波数に応じた周波数の発振出力を行う現用系原子発振器と、原子の共鳴周波数に応じた周波数を制御信号に基づいて制御して発振出力を行う予備系原子発振器と、前記現用系原子発振器の発振出力と該予備系原子発振器の発振出力との差を検出し、この差に応じた前記制御信号を予備系原子発振器に入力することで、前記予備系原子発振器の発振周波数を前記現用系原子発振器の発振周波数と同期させる制御信号入力部と、前記現用系原子発振器の正常時には該現用系原子発振器の出力を基準周波数信号として外部へ出力し、前記現用系原子発振器の障害時には前記予備系原子発振器の出力を基準周波数信号として外部へ出力する切替器とを備えた。

(もっと読む)

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

101 - 120 / 123

[ Back to top ]