Fターム[5J106CC19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 複数の発振回路・VCO (166)

Fターム[5J106CC19]の下位に属するFターム

複数のループVCO (43)

Fターム[5J106CC19]に分類される特許

41 - 60 / 123

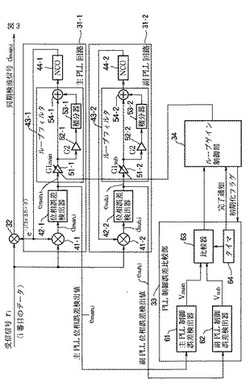

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

周波数シンセサイザ

【課題】バラツキ耐性を強くし、温度変動のときに、VCOの周波数変動を補償する周波数シンセサイザの提供。

【解決手段】VCO5と、VCOの発振出力を可変分周回路4で分周した信号22と基準発振回路1の基準信号21を位相比較する位相比較器2と、位相比較結果に基づきVCOへの制御電圧23を生成するループフィルタ3とがPLLを構成し、VCOは、複数の重み付けされた容量素子56〜58と制御信号に基づきオン・オフされる複数のスイッチを備えた容量バンクと、バラクタ54を備える。温度補償ブロック7は、バラクタの補正電位発生回路73と、容量バンクの寄生容量の補正電位発生回路71と、該補正電位発生回路の出力電位を制御信号に基づき重み付け処理するゲイン可変アンプと、バラクタの補正電位発生回路の出力電圧とゲイン可変アンプの出力電圧を加算する加算回路79とを備え、加算回路の出力25によりVCOのバラクタが制御される。

(もっと読む)

温特補正機能付き発振回路およびその製造方法

【課題】 発振周波数を補正するためのメモリなどが不要な温特補正機能付き発振回路およびその製造方法を実現する。

【解決手段】 温特補正機能付き発振回路10は、第1の発振回路21と、第2の発振回路22と、第1の発振回路21が発生する発振周波数を理想の発振周波数に近い発振周波数に補正するための補正回路50とを備える。補正回路50は、第1の発振回路21の発振周波数f1と、第2の発振回路22の発振周波数f2との差分(f1−f2)を検出し、その検出した差分に補正係数αを乗じ(α・(f1−f2))、その補正された差分を第1の発振回路21の発振周波数に加算し(f1+α・(f1−f2))、それを出力する動作を行う。

(もっと読む)

位相同期発振器アレイ

【課題】小型でIC化が可能な位相同期発振器を実現すること。

【解決手段】 位相同期した複数の発振信号を得る位相同期発振器アレイにおいて、位相が180度異なる2つの信号を入力する第1入力端子と第2入力端子とを有したn個の第1差動増幅器から第n差動増幅器と、1≦k<nの全ての自然数kに対して、第k差動増幅器の第2入力端子と第k+1差動増幅器の第1入力端子との間の全て、及び、第n差動増幅器の第2入力端子と第1差動増幅器の第1入力端子との間を、それぞれ、逆相で結合するn個のフィルタFと、を設けたことを特徴とする位相同期発振器アレイ。フィルタFは、一方の差動増幅器1の第2入力端子B12と接地間に配設された第2インダクタL12と、他方の差動増幅器2の第1入力端子B21と接地間に配設された第1インダクタとL21、一方の差動増幅器1の第2入力端子と他方の差動増幅器2の第1入力端子との間を接続する第3容量C15と第3インダクタL23との直列接続回路とを有する。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、ジッタを低減する。

【解決手段】第1の発振回路および第2の発振回路はそれぞれ2つの周波数制御端子を備え、それぞれの一方の周波数制御端子に周波数制御信号Aを入力する構成であり、第2の発振回路の他方の周波数制御端子に固定の周波数制御信号Bを与え、第1の発振回路および第2の発振回路の各発振周波数を比較し、その周波数誤差に応じた周波数制御信号Cを第1の発振回路の他方の周波数制御端子に与えるばらつき補償回路を備える。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

基準周波数発生装置及び基準周波数発生システム

【課題】冗長化された基準周波数発生システムにおいて、現用側と予備側での出力切替時に出力信号のタイミングが急激に変動するのを防止する。

【解決手段】現用側の基準周波数発生装置51においては、自機のGPS受信機21aが生成する1PPS信号がPLL回路22aに供給される。予備側の基準周波数発生装置52においては、現用側の基準周波数発生装置51のPLL回路22aから出力された1Hzの信号が、第1伝送経路を経由してPLL回路22bに供給される。予備側に入力された1Hzの信号は、前記第1伝送経路と遅延量が等しい第2伝送経路を経由して現用側に戻される。現用側の基準周波数発生装置51は、自機のPLL回路22aからの1Hzの信号と、予備側に出力して戻された1Hzの信号と、の時間差に基づき補正用信号を出力する。予備側の基準周波数発生装置52は、補正用信号に基づいて、PLL回路22bの出力信号の位相を調整する。

(もっと読む)

ルビジウム原子発振器

【課題】スイープ時間を短時間にする。

【解決手段】マイクロ波MWに基づき共鳴信号RSを発生する原子共鳴器1と、原子共鳴器1が発生する共鳴信号RSを増幅する増幅器2と、位相変調信号LWを出力する低周波発振器10と、共鳴信号RSと位相変調信号LWとに基づき制御電圧VCを出力する周波数制御部4と、制御電圧VCによって発振信号OUTの周波数が制御される電圧制御発振器8と、発振信号OUTを位相変調信号LWに基づき逓倍及び位相変調してマイクロ波MWを出力する逓倍位相変調部9と、記憶部27と、共鳴信号RSの周波数がロックされたロック状態の時に制御電圧VCを所定の時間間隔TSで記憶部27に同期電圧SVとして記憶させ、共鳴信号RSの周波数がロックされていない非ロック状態の時に制御電圧VCと同期電圧SVとに基づき周波数制御部4に制御信号S2を出力する制御部26と、を含むルビジウム原子発振器100。

(もっと読む)

複数の同調ループを有する周波数シンセサイザ

【解決手段】複数の同調ループ、例えば微同調ループと粗同調ループ、を有する周波数シンセサイザが述べられる。微同調ループは、制限された同調レンジにわたって動作し、細かい周波数分解能を有し得る。粗同調ループは、広い同調レンジにわたって動作し、粗な周波数分解能を有し得る。微同調ループは、参照周波数の参照信号を受信し、細かいステップで調整可能な第1周波数の微同調信号を生成し得る。粗同調ループは、参照信号を受信し、出力信号と微同調信号とに基づいて第2周波数の微同調信号を生成し得る。第2周波数は、粗なステップ、例えば参照周波数の整数倍で調整可能であり得る。出力周波数は、第1周波数及び第2周波数に基づいて決定され得る。 (もっと読む)

ジッタ発生装置

【課題】ジッタ信号に対応したジッタ付加信号を出力できるジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、ジッタ信号を増幅する増幅回路と、基準信号が入力され、増幅回路の出力によりジッタを付加する第1のPLL回路と、基準信号が入力される第2のPLL回路と、第1、第2のPLL回路の出力を位相比較する位相比較回路と、ジッタ信号を平滑する第1の平滑回路と、位相比較回路の比較結果を入力し、平滑する第2の平滑回路と、第1、第2の平滑回路の出力を比較し、増幅回路の増幅を制御する電圧差比較回路とを備えたことを特徴とするものである。

(もっと読む)

周波数シンセサイザ及び無線送信装置

【課題】VCOの出力帯域を選択設定可能な周波数シンセサイザにおける消費電力を低減すること。

【解決手段】互いに並列に接続されたミキサ111と分周器112とを有する周波数変換回路110を設け、VCO101の周波数帯域選択時に分周器112を用いることにより、VCO101の周波数帯域選択時の位相比較器102の最高動作周波数を低くすることができ、消費電力を低減できる。また、送信時にはミキサ111を用いることにより、送信時のループゲインを下げずに済む。

(もっと読む)

PLL回路および通信用半導体集積回路装置

【課題】スプリアス特性の向上が実現可能なPLL回路およびそれを搭載した通信用半導体集積回路装置を提供する。

【解決手段】例えば、PLL回路を含む高周波ICチップRF_CP3において、PLL回路内に複数の電圧制御発振回路ブロックVCO_BK1〜VCO_BK3を設ける。そして、ループフィルタの一部となる2次のループフィルタFLT_Aを位相検出等を行うシンセサイザブロックSYNに配置し、他の一部となる1次のループフィルタFLT_BをVCO_BK1〜VCO_BK3のそれぞれに配置する。さらに、VCO_BK1〜VCO_BK3のそれぞれにおいては、インダクタL1,L2をRF_CP3の内側でなく外側(外周の一辺)に近くなるような向きにレイアウトする。

(もっと読む)

位相同期発振器アレイ及びアレイアンテナ装置

【課題】分配器を用いることなく、位相同期した多数の発振信号を供給すること。

【解決手段】発振信号の位相差が90度である4位相の同一周波数の発振信号を出力する位相同期発振器アレイである。複数の閉線路21〜23から成る複数のリング共振器と、閉線路の全長を1/4分割した位置に設けられた4つのポート21a〜21dのうち隣接する2つのポート21b、21cと、この閉線路21に隣接する閉線路22の隣接する2つのポート22a、22d間を、それぞれ、負性抵抗として、接続する差動発振器31a、31bと、少なくとも何れか1方の端部に配置される閉線路21において、その閉線路の4つのポートのうち、差動発振器が接続されていない2つのポート21a、21dに対して、90度の位相差を有した信号を励振する励振装置30とを有する。

(もっと読む)

周波数シンセサイザおよびその制御方法

【課題】周波数シンセサイザがロック状態にあり、かつ、電圧制御発振器の電圧制御信号が一定の電圧範囲からはずれたときに、ロック状態を保ったまま、電圧制御信号を一定の電圧範囲に戻す。

【解決手段】ローパスフィルタ3が生成する制御電圧信号11によって直流バイアス電圧が制御された可変容量ダイオード52の他に補償用可変容量ダイオード53、54を電圧制御発振器5に設け、制御電圧信号11をモニタし、制御電圧信号11の電圧が可変容量ダイオード52の容量を容易に変えられる範囲外の電圧となったときに制御信号16、17のレベルを変化させるモニタ回路8と、その制御信号16、17のレベルの変化をロック状態が解除されないゆっくりとした電圧変化に鈍らせて補償用可変容量ダイオードに直流バイアス電圧を与える時定数回路72とを備える。

(もっと読む)

パルス発生回路及びパルス発生回路を備えた電子機器

【課題】PVTに依存せずに安定した周波数を出力する。

【解決手段】出力する第1の出力信号Vf1の周波数を第1の制御電圧VC1で制御する第1の電圧制御発振器11と、第1の出力信号Vf1及び基準信号CLKに基づき第1の出力信号Vf1の周波数を一定に維持する第1の制御電圧VC1を生成する制御電圧生成部13と、を含む位相同期回路10と、出力する第2の出力信号Vf2の周波数を第2の制御電圧VC2で制御する第2の電圧制御発振器20と、第1の制御電圧VC1に基づき第2の出力信号Vf2の周波数を一定に維持する第2の制御電圧VC2を生成する制御電圧変換部30と、を含むパルス発生回路1。

(もっと読む)

CDR回路

【課題】再生クロックのジッタを低減する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスにより発振位相が制御されるクロックを生成するゲーテッドVCO3と、フィードバック入力端子にゲーテッドVCO3の出力クロックが入力され、ゲーテッドVCO3の出力クロックと同じ周波数の再生クロックを生成するVCO4と、入力データを遅延させる遅延回路5と、遅延回路5を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。

(もっと読む)

PLL回路

【課題】発振周波数帯域がそれぞれ互いに異なる複数のVCOを備えつつ、発振信号の周波数のアンロック状態を短時間にすることが可能なPLL回路を提供することを目的とする。

【解決手段】VCO22−1〜22−8と、VCO出力回路16と、プログラマブル分周器14と、位相比較器17と、チャージポンプ20と、ループフィルタ21と、VCO22−1〜22−8からそれぞれ出力される発振信号が順次選択されるようにVCO選択信号を出力するとともに、VtuneがVCO選択判定用の所定範囲に入ると、VCO選択信号を固定するVCO選択回路15とを備えてPLL回路11を構成し、VtuneがVCO切り替え判定用の所定範囲に入らなくなると、VtuneがVCO選択判定用の所定範囲に入るように、VCO選択信号を切り替える。

(もっと読む)

発振装置

【課題】通信機などが必要とする発振装置の発振周波数範囲の広帯域化が、簡単な構成で精度よく行えるようにする。

【解決手段】8GHzから12GHzなどの第1の周波数帯域幅の可変範囲を持つ低位相雑音な発振手段と、発振手段の発振出力を分周する周波数分周器とを備える。発振手段が出力する発振信号の周波数と、周波数分周器で分周する分周比を制御して、周波数分周器の出力周波数を、発振手段の発振周波数以下の周波数で、第1の周波数帯域幅と同じかそれ以上の周波数帯域幅で可変設定される所望の周波数とする制御を行う。

(もっと読む)

局部発振信号発生装置の検査方法

【課題】発振周波数可変域の異なる複数の電圧制御発振器を有する局部発振信号発生装置を検査するための検査方法であって、安価な半導体検査装置を用いて実現可能であり且つ検査効率のよい検査方法を提供する。

【解決手段】発振周波数可変域の異なる複数の電圧制御発振器1_1〜1_nを有する局部発振信号発生装置を検査するための検査方法であって、前記複数の電圧制御発振器1_1〜1_nの各発振周波数可変域の上端周波数及び下端周波数のうち一部のみ(例えばfA,fB)を探索し、その探索結果を用いた演算によって得られた周波数ポイント(例えばfD)の正常発振の有無を判定することにより、発振周波数可変域が隣接する電圧制御発振器同士において発振周波数可変域が規定以上重複していることを検査する検査方法。

(もっと読む)

PLL回路

【課題】複数のVCOを切り替えて使用するPLL回路において、VCOの位相雑音を最適化することである。

【解決手段】PLL回路11の複数のVCO12−1〜12−nの内の1つの選択は、VCO選択データにより行われ、キャパシタの選択はVSBデータにより行われる。バイアス電流設定回路25は、VCO選択データとVSBデータと制御電圧のデジタル変換値VTDをデコードして、予め定めたバイアス設定値を可変電流源I1に出力する。

(もっと読む)

41 - 60 / 123

[ Back to top ]