Fターム[5J106CC19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 複数の発振回路・VCO (166)

Fターム[5J106CC19]の下位に属するFターム

複数のループVCO (43)

Fターム[5J106CC19]に分類される特許

81 - 100 / 123

ルビジウム原子発振器

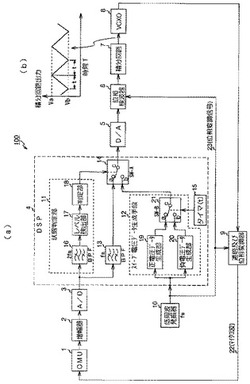

【課題】スイープ電圧発生のための回路規模を小型化し、且つ非ロック時における周波数引き込み動作を自動的に行なうことが可能なルビジウム原子発振器を提供する。

【解決手段】このルビジウム原子発振器100は、OMU1と、増幅器2と、出力信号をデジタル信号に変換するA/D変換器3と、ロック状態又は非ロック状態を判定する状態判定部11と、位相変調信号fmの周波数成分を選択的に出力するBPF13と、スイープ電圧データを生成するスイープ電圧データ生成手段12と、タイマ15と、第1のBPF13の出力信号又はスイープ電圧データ生成手段12の出力信号を選択するSW−A14と、アナログ信号に変換するD/A変換器5と、位相検波して周波数制御信号を生成する位相検波器6と、周波数制御信号を積分処理する積分回路7と、周波数制御信号に従い出力周波数が制御されるVCXO8と、を備えて構成されている。

(もっと読む)

ジッタ発生装置

【課題】ジッタをデジタル的に発生させることにより、ジッタに関する調整が可能でありジッタ非注入時の信号劣化が生じることを防止したジッタ発生装置を提供する。

【解決手段】本実施の形態におけるジッタ発生装置では、第2カウンタ5が出力する−1〜1の範囲内のランダムな整数値のカウンタ値を第1カウンタ2が出力するカウンタ値に加算して、波形メモリ3にアドレスとして入力し振幅データから波形を得ることにより、ジッタをデジタル的に発生させ、波形20に対して波形21,22の波形の間をランダムにゆらいだ、ジッタが注入された波形を得ることが可能となる。

(もっと読む)

位相ロック・ループを制御する方法、利得制御装置及び位相ロック・ループ・システム

【課題】マルチ・ギガヘルツ範囲で動作し且つ低ジッタの、調整可能な利得を有する位相ロック・ループ(PLL)を提供する。

【解決手段】

1つの実施形態では、PLLのfVCO 信号の諸特性を取得する。これらの特性は、fVCO 信号及びPLLの位相ロック状態に関する異なるタイプのジッタの出現回数を含む。利得制御モジュールは、前記取得した諸特性の分析に基づき、少なくともPLLの一部を制御する。例えば、PLLが位相ロックされているか、又はループ・フィルタの漏洩がある場合、PLL内にあるチャージ・ポンプの利得が減少される。前記取得した特性に基づいて、チャージ・ポンプのミスマッチが検出される場合、当該ミスマッチを修正するために、追加の制御信号がチャージ・ポンプに供給される。

(もっと読む)

電圧生成回路及び発振装置

【課題】位相雑音特性が良好で、かつ低消費電力、小型化に適した発振装置を提供すること。

【解決手段】固定電圧Vrefが印加される第1の端子と、可変電圧Vcが印加される第2の端子と、前記第1の端子と前記第2の端子との間に直列接続された、抵抗値rのm個の抵抗器及び抵抗値RINの入力抵抗器と、前記m個の抵抗器のうちn個の抵抗器を選択するための複数のスイッチと、制御電圧を出力する第3の端子と、を有する抵抗切替部と、前記複数の抵抗器に流す定電流の電流値Ioffを設定し当該定電流を供給する電流供給部とから構成され、{Vref+n×r×[(VC−Vref)/(m×r+RIN)]}で与えられる第1の電圧と、{−(n×r×Ioff)}で与えられる第2の電圧との重ね合わせにより規定される第3の電圧を、前記第3の端子から制御電圧として出力する。

(もっと読む)

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

位相同期発振器及びその制御方法

【課題】VCO回路の特性バラツキや温度変動によらず、簡単な構成及び制御で常に高安定なVCO出力が得られることを課題とする。

【解決手段】位相比較器と、ローパスフィルタと、主制御を行う制御部と、該制御部出力の制御電圧で駆動されるVCO回路と、その出力を分周する可変分周器とからなるPLLループを備える位相同期発振器であって、制御部は、PLLループを複数周波数でロックさせて各ロック時の制御電圧を測定し、該測定した各制御電圧に基づき、VCO回路のリニアリティー校正された変調感度を求めると共に、該PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための制御電圧信号を生成する。

(もっと読む)

GPS機器用の非常に精密で温度に依存しない基準周波数を生成するためのシステム及び方法

【課題】 二連式水晶発振器を組み込んだ、水晶振動子を用いたクロック発振器において温度を補償するための機器及び方法である。

【解決手段】 二つの発振器の同期を担当するプロセッサの効率的な使用によって、最小限の電力消費が達成される。この発明は、特に、携帯式無線位置測定機器に精密な基準クロックを供給するのに適している。

(もっと読む)

インピーダンス回路およびこれを用いた信号生成回路

【課題】基準周波数を得る場合、安定した周波数、もしくは遅延要素を得る回路を提供する。

【解決手段】第1の温度変動率を持つ第1のインピーダンス回路1と第1の能動回路3で構成した第1の発振回路6と、第1の温度変動率とは逆の変動方向となる第2の温度変動率を持つ第2のインピーダンス回路2と第2の能動回路4で構成した第2の発振回路7との出力を時系列的に交互に切替器5で選択する。第1のインピーダンス回路1の温度係数の絶対値が第2のインピーダンス回路2の温度係数より大きいとき、第1の発振回路6の使用時間を短くし、温度係数の小さい第2の発振回路7の使用時間を長く動作させるように、温度係数の比と逆の比率で発振回路の使用時間の比率を設定する。温度変動方向が逆の2つの温度係数を有することから、平均値として温度変動がほぼなく軽減される。時間平均値として温度変動が極めて小さく温度変動率の改善された発振周波数を得る。

(もっと読む)

PLL回路

【課題】複数のVCOを有するPLL回路のチップ上の占有面積を削減でき、且つ、PLL回路に対するマイコンの負担を軽減できる。

【解決手段】本発明の例に関わるPLL回路は、位相差信号を出力する位相比較回路1と、位相差信号に基づくチューニング電圧を出力するチャージポンプ回路2と、チューニング電圧に基づく発振周波数を出力する複数のVCO51〜5nと、複数のVCOの中から1つのVCOを自動的に選択するオートセレクト回路を具備し、オートセレクト回路は、チャージポンプ回路2と接続される比較回路3と、比較回路3とVCO51〜5nと接続されるカウンタ4とを具備し、比較回路3は、チューニング電圧に基づき、カウンタ4をアップカウント、又は、ダウンカウントさせるアップ/ダウン信号を出力し、カウンタ4は、アップ/ダウン信号に基づき、複数のVCO51〜5nの中から1つのVCOを選択するセレクト信号を出力することを備える。

(もっと読む)

変調回路方式及びその電圧制御発振器

【課題】PLLループの電圧制御発振器にかかる回路負担を抑えることにより、電圧制御発振器の性能が低下することの無い変調回路方式及びその電圧制御発振器を提供することを目的とする。

【解決手段】電圧制御発振器12を具備するPLLループと、変調信号とPLLループ外調整電圧とを加算する加算手段17と、加算手段17の出力を電圧制御発振器12へ供給する周波数粗調整手段18とを有し、加算手段17において加算されて出力された、変調信号とPLLループ外調整電圧との加算信号を、周波数粗調整手段18を介して電圧制御発振器12へ供給し、PLLループにおける電圧制御発振器12の発振周波数信号に加算信号を重畳して変調信号を生成する。

(もっと読む)

CDR回路

【課題】入力データに含まれているジッタを削除した再生データを得る。

【解決手段】入力データのデータレート周波数と同じ周波数の参照クロックを入力データにより位相合わせして再生クロックを作成し、該再生クロックにより前記入力データをFIFO101に書き込む。該FIFO101からの読み出しには、前記再生クロックと同期関係にない前記参照クロック又は別のクロックを使用し、前記FIFO101から再生データを出力させる。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

局部発振装置及びこれを用いた無線送受信機

【課題】周波数安定性と位相雑音特性に優れた局部発振装置を提供すること。

【解決手段】所定の信号処理手段に入力される少なくとも2つの局部発振信号を出力する局部発振装置であって、固定周波数である第1の局部発振信号を発する第1の発振手段と、可変周波数である第2の局部発振信号を発する第2の発振手段と、を備え、第2の発振手段は、第1の局部発振信号を入力して当該第1の局部発振信号の変化を補正する第2の局部発振信号を出力する。

(もっと読む)

クロック生成回路

【課題】クロック源となる発振器の経年変化によって生じた周波数変動を定期的な保守時に周波数測定を行うことなく検出する。

【解決手段】制御電圧によって制御されるOCVCXO102の出力に応じたクロック信号を生成する現用系クロック生成回路100と、OCVCXO102の出力を用いて生成されたリファレンス信号REFnを用いて現用系クロック生成回路100と同期するように決定される制御電圧によって制御されるOCVCXOの出力に応じたクロック信号を生成する予備系クロック生成回路200とからなり、制御電圧の値を監視することにより、OCVCXO102における周波数変動を検出する。

(もっと読む)

発振器結合システム

【課題】ノイズ抑制の困難度を簡易な回路素子で簡単化するための発振器結合システムを提供する。

【解決手段】複数の発振素子と、複数の遅延素子とを備え、該遅延素子は、少なくとも2つの発振素子の間に接続され、それらの複数の遅延素子の間には特定の位相または時間遅延関係があり、該遅延素子により少なくとも該2つの発振素子の位相または周波数のノイズ抑制関連特性が結合されることで、回路システム動作中においてノイズの自己相関性が低下し、位相または周波数のノイズ抑制効果が増進し、スペースを取るような固体(solid state)サーキュレータ(circulator)またはアイソレーター(isolator)または共振器(resonator)の使用はなく、信号のひずみが低減され、システムの安定性が向上している。

(もっと読む)

広帯域高周波発振回路

【課題】地上デジタル放送の中継装置のローカル信号発生源として好適な広帯域高周波発振回路を提供する。

【解決手段】第1のPLLループ10のDDS回路16は、基準信号より高い周波数で発振する電圧制御水晶発振回路13の出力信号をシステムクロックとして基準信号と同一の周波数の信号Fc1を生成する。位相比較器11は、信号Fc1と基準信号とを位相比較して電圧制御水晶発振回路13を制御し参照信号Frefを生成する。第2のPLLループ20の電圧制御発振回路23a〜23cは、切換回路24により選択され、参照信号Frefによりローカル信号を生成する。DDS回路26は、ローカル信号を2分周し、システムクロックとして参照信号Frefと同一周波数の信号Fc2を生成する。位相比較器21は、信号Fc2と参照信号Frefを位相比較し、上記選択された電圧制御発振回路を周波数制御する。

(もっと読む)

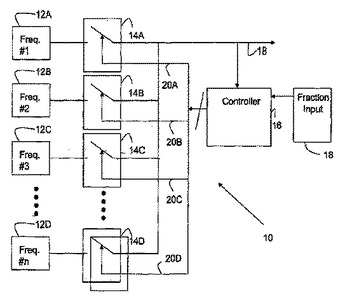

高速スイッチングのための周波数合成の新規方法

単一のソースの設計、マルチプレクサの設計、分数分周器の設計、または周波数逓倍器と周波数分周器の設計で実装可能なデジタル周波数シンセサイザである。実装は、制御器のディザリング回路またはデルタシグマ変調器を利用可能である。この周波数シンセサイザは、CMOS構成において実装可能であり、クリーンアップ位相ロックループ(PLL)を利用可能である。  (もっと読む)

(もっと読む)

クロック信号発生装置、クロック信号発生方法及びプログラム

【課題】位相の変化に迅速に追従しつつ、クロックスリップが起こり難い(安定した)クロック信号を再生するクロック信号発生装置等を提供することである。

【解決手段】位相比較器1Aは、データ信号と、デジタルVCO1Cの再生クロック信号を基準としたデータ信号の位相の遅れ及び進みを検出する。ランダムウォークフィルタ1Bは、この遅れ進みの回数差を計測して、回数差の絶対値が所定値に達すると、差を打ち消す方向に再生クロック信号の位相を変化させるようデジタルVCO1Cを制御し、計測結果をリセットして計測を再開する。再生位相比較器3は、デジタルVCO1C及び2Cの各再生クロック信号の位相差を検出してランダムウォークフィルタ1Bに通知する。ランダムウォークフィルタ1Bは、通知された位相差が所定量に達している間は、計測結果のリセットやデジタルVCO1Cの再生クロック信号の位相の変更を行わない。

(もっと読む)

安定クロック信号を供給する方法及び装置

本願に記載した実施例は、通信インタフェース(例えば、UARTポート(76))を駆動させるために使用する安定クロック信号を生成するための、低コストの信号調節又は信号校正の方法及び装置に関する。特に、マイクロコントローラ(60)内のプロセッサ(61)は、低周波水晶発振器(72)及びスケーリング・モジュール(78)を使用して、高周波RC発振器(64)によって生成される不安定クロック信号に含まれる周波数オフセット・エラーを除去する。特定のトリガ・イベントが生じた場合(マイクロコントローラの電源が投入された場合、マイクロコントローラが、スリープ・モード又は待機モードからウェイクアップされた場合、マイクロコントローラに通信エラーが生じた場合など)、プロセッサは周波数オフセット・エラーを検出し、除去する。  (もっと読む)

(もっと読む)

PLL周波数シンセサイザ

【課題】チャンネル周波数が整数と分数との和で表現される複雑な周波数に適合可能なPLL周波数シンセサイザを提供することを目的とする。

【解決手段】マルチループ構成を持つPLL周波数シンセサイザであって、出力周波数の整数部分の比較周波数を設定するメインループ10と、出力周波数の分数部分の比較周波数を設定するサブループ15とを備え、メインループ10で設定された出力周波数の整数部分とサブループ15で設定された出力周波数の分数部分との和となる周波数を出力周波数として出力することにより上記課題を解決する。

(もっと読む)

81 - 100 / 123

[ Back to top ]