Fターム[5J106CC19]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 発振回路、VCO (2,067) | 複数の発振回路・VCO (166)

Fターム[5J106CC19]の下位に属するFターム

複数のループVCO (43)

Fターム[5J106CC19]に分類される特許

21 - 40 / 123

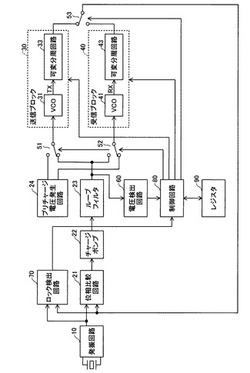

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

基準周波数発生装置

【課題】長時間にわたって基準周波数周波数の周波数安定度を維持可能で、かつ安価な基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置1は、ルビジウム発振器11と、ルビジウム発振器11より周波数安定度が低い水晶発振器21と、判定部42と、切替スイッチ51a〜51fと、を備える。判定部42は、ルビジウム発振器11が正常な出力信号を出力している正常状態か、正常な出力信号を出力していない故障状態か、を判定する。切替スイッチ51c,51dは、ルビジウム発振器11が正常状態であると判定部42が判定しているときは、第1PLL回路を構成するように設定を行い、ルビジウム発振器11が故障状態であると判定部42が判定しているときは、第2PLL回路を構成するように設定を行う。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

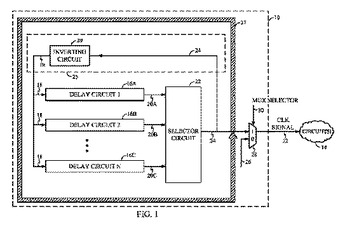

適応クロック発生器、システムおよび方法

機能回路のための、性能マージンを回避し、あるいは小さくするためのクロック信号を生成するために使用することができる適応クロック発生器、システムおよび関連する方法が開示される。特定の実施形態では、クロック発生器は、機能回路内の選択された遅延経路に関連する遅延回路に提供された遅延経路に従って、自律的に、かつ、適合的にクロック信号を生成する。クロック発生器には、入力信号を受け取るように適合され、かつ、出力信号を生成するために、受け取った入力信号を機能回路の遅延経路に関連する量だけ遅延させるように適合された遅延回路が含まれている。遅延回路には、上記出力信号に応答する帰還回路が結合されており、この帰還回路は、遅延回路に発振ループ構成で戻すための入力信号を生成するように適合されている。入力信号を使用して機能回路にクロック信号を提供することができる。  (もっと読む)

(もっと読む)

信号処理装置

【課題】 ジッタの少ないクロックを発生させる

【解決手段】 第1の発振器と、前記第1の発振器から出力される第1のクロックの周波数とは異なる周波数の第2のクロックを出力する第2の発振器と、前記第1の発振器からの第1のクロックと前記第2の発振器からの第2のクロックのうちの一方を選択する選択手段と、前記選択手段により選択された第1のクロックまたは第2のクロックの周波数を逓倍し、出力クロックを生成する生成手段と、前記第1の発振器からの第1のクロックを逓倍する逓倍回路と、前記逓倍回路からの出力信号と前記生成手段からの出力クロックとの位相差を検出し、前記位相差を示す信号を前記第2の発振器に出力することにより前記第2の発振器からの第2のクロックの周波数を変更する位相検出手段とを備える。

(もっと読む)

可変インダクタ、電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路

【課題】制御電圧入力端子の個数を減少させることができる新規な可変インダクタならびにその新規な可変インダクタを備える電圧制御発振器、複合型PLL回路、フィルタ回路および増幅回路を提供する。

【解決手段】本発明の可変インダクタ5においては、複数のインダクタンス素子61、62、63、64におけるそれぞれの接続点とグランド10との間にそれぞれ接続された複数のスイッチダイオード7A、7B、7Cのそれぞれの一端側に対して、複数の定電圧入力端子8A、8B、8Cを介して、互いに異なる定電圧がそれぞれ供給されている。また、本実施形態の可変インダクタ5においては、複数のスイッチダイオード7A、7B、7Cにおけるそれぞれの他端側に対して、1個の制御電圧入力端子9を介して、制御電圧が供給されている。

(もっと読む)

量子干渉装置、原子発振器及び磁気センサー

【課題】アルカリ金属原子に対するEIT現象の発現効率を高めることにより、レーザーパワーの利用効率を向上させることができる量子干渉装置、原子発振器及び磁気センサーを提供すること。

【解決手段】光源10は周波数がΔωずつ異なる複数の第1,第2の共鳴光を発生させ、光検出手段40は磁場発生手段30により磁場が与えられたアルカリ金属原子を透過した第1,第2の共鳴光を含む光の強度を検出する。制御手段50は、光検出手段の検出結果に基づき、所定の1対の第1,第2の共鳴光の周波数差がアルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数差に等しくなるように、かつ、アルカリ金属原子の2つの基底準位の各々に発生した、磁気量子数が互いに1だけ異なる2つのゼーマン分裂準位のエネルギー差に相当する周波数δに対して、2×δ×n=Δω及びΔω×n=2×δ(nは正の整数)の少なくとも一方を満足するように制御する。

(もっと読む)

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

周波数シンセサイザ

【課題】 電源投入直後から長期にわたる使用期間全体で良好な周波数安定度が得られる周波数シンセサイザを提供する。

【解決手段】 基準信号発生回路1に、OCXO20と、TCXO30と、それぞれの出力に対してウェイト調整を行うウェイト変換器21,31と、各ウェイト変換器からの出力を加算して基準信号として出力する加算器41を備え、CPU10が、電源投入時にはTCXO30のウェイトを100%、OCXO20のウェイトを0%とし、徐々にOCXO20のウェイトを上げて、予め設定された一定時間後にTCXO30のウェイトを0%、OCXO20のウェイトを100%とするようにウェイト変換器B,Cを制御する周波数シンセサイザとしており、電源投入後に急速に周波数を安定させることができるものである。

(もっと読む)

クロック信号分配装置

【課題】高品質のクロック信号を分配することができるクロック信号分配装置を提供することを課題とする。

【解決手段】第1のインダクタ及び第1の容量に応じた周波数で共振して信号を発振する複数のLC共振発振器(302,303)と、第2のインダクタ及び第2の容量に応じた周波数で共振し、入力クロック信号に同期した信号を発振する注入同期型LC共振発振器(301)と、前記複数のLC共振発振器及び前記注入同期型LC共振発振器の発振ノードを接続する伝送線路(311,312)とを有することを特徴とするクロック信号分配装置が提供される。

(もっと読む)

PLL装置及び不要周波数回避方法

【課題】PLL装置において、不要周波数の影響を、無線性能に影響を与えることなく回避できるようにする。

【解決手段】電圧制御発振器3、4と、基準信号に基づく第1信号及び電圧制御発振器の出力信号に基づく第2信号の両位相を比較し、位相差を示す位相差信号を出力する位相比較器1と、位相差信号に基づき、両位相を同期させる制御電圧を電圧制御発振器に印加するループフィルタ2とを備え、所定の目的周波数を得るPLL装置において、目的周波数を中心とする所定の周波数範囲内に不要周波数が存在する場合に、不要周波数を該周波数範囲外のものとするために基準信号の周波数を変更する基準周波数変更手段5と、基準信号の周波数の変更にも拘わらず目的周波数の出力が維持されるように、第1信号又は第2信号を生成する際の分周比を変更する分周比変更手段5とを設ける。

(もっと読む)

クロック供給システム

【課題】基準クロックが異常であるのか、電圧制御発振器が異常であるのか故障原因を特定することが可能なクロック供給システムを提供する。

【解決手段】現用系のシステム200のVCXO203の制御値Xがα<X<βにあるかを監視し、その範囲から外れた時に異常を検出する。この異常検出時にVCXO203の制御値を予め決められた制御値γに設定し、現用系のシステムで運用する。また、この運用状態で予備系のシステム210のVCXO213の制御値X’がα’<X’<β’にあるかを判定し、その範囲内にある場合には基準クロック2aの異常と判定し、現用系のまま運用する。一方、その範囲内から外れている場合には現用系のVCXO203が異常と判定し、予備系のシステムに切り替えを行う。

(もっと読む)

クロックデータ再生回路

【課題】複数のVCO間の発振周波数のばらつきを補償し、低ジッタで大きな電源電圧・温度変動耐性を実現する。

【解決手段】第1の発振回路および第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第2の発振回路および第1の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Ca,Cbを入力する端子を備え、第1〜第2の発振回路はそれぞれ2つの制御端子を備え、それぞれの一方の制御端子に周波数制御信号Aを入力し、第1の発振回路の他方の制御端子に回路間ばらつき調整信号Caを入力し、第2の発振回路の他方の制御端子に回路間ばらつき調整信号Cbを入力する構成。

(もっと読む)

PLL回路および電圧制御発振器

【課題】PLL回路のデッドロック状態になることを防止する

【解決手段】閾値判定部13aは、制御電圧の高低を示す制御信号を生成する。制御部13bは、制御信号に応じた制御値を出力し、制御値が発振周波数の上限および下限について最も高い対応関係を示す場合において制御信号が高を示すとき、および制御値が発振周波数の上限および下限について最も低い対応関係を示す場合において制御信号が低を示すときのいずれか一方を満たす際、所定の制御値を出力する。発振器13cは、制御電圧と発振周波数との対応関係が発振周波数の上限および下限が異なるように複数定められていると共に対応関係が複数の制御値と対応付けられており、制御値が示す対応関係における制御電圧に応じた発振周波数を有する出力信号を出力する。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

クロックデータ再生回路

【課題】プロセスばらつきによる発信周波数ずれを調整する。

【解決手段】入力データと周波数および位相が同期した再生クロックを出力する発振回路と、発振回路が出力する再生クロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、発振回路のプロセスばらつきによる発振周波数のずれを調整するプロセスばらつき調整信号Bを入力する端子を備え、発振回路は2つの制御端子を備え、その一方の制御端子に周波数制御信号Aを入力し、他方の制御端子にプロセスばらつき調整信号Bを入力する構成である。

(もっと読む)

周波数シンセサイザ

【課題】バラツキ耐性を強くし、温度変動のときに、VCOの周波数変動を補償する周波数シンセサイザの提供。

【解決手段】VCO5と、VCOの発振出力を可変分周回路4で分周した信号22と基準発振回路1の基準信号21を位相比較する位相比較器2と、位相比較結果に基づきVCOへの制御電圧23を生成するループフィルタ3とがPLLを構成し、VCOは、複数の重み付けされた容量素子56〜58と制御信号に基づきオン・オフされる複数のスイッチを備えた容量バンクと、バラクタ54を備える。温度補償ブロック7は、バラクタの補正電位発生回路73と、容量バンクの寄生容量の補正電位発生回路71と、該補正電位発生回路の出力電位を制御信号に基づき重み付け処理するゲイン可変アンプと、バラクタの補正電位発生回路の出力電圧とゲイン可変アンプの出力電圧を加算する加算回路79とを備え、加算回路の出力25によりVCOのバラクタが制御される。

(もっと読む)

21 - 40 / 123

[ Back to top ]