Fターム[5J106CC25]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | サンプリング型 (61)

Fターム[5J106CC25]に分類される特許

41 - 60 / 61

位相同期回路

【課題】タイミングジッタをより低く抑えて安定したクロックパルスを得る。

【解決手段】水平・垂直同期分離回路10から分離出力された水平及び垂直同期信号に基づき、Vブランキング期間中の水平位相変動の比較的大きな期間である連続した5Hの水平同期期間においては、各水平同期期間に対応して発生させるサンプリングパルス信号をマスク処理し、このマスク処理されたサンプリングパルス信号に基づいてVCO発振回路50の発振周波数を電圧制御するようにした。

(もっと読む)

デジタル位相検知器及びデジタル位相検知信号の発生方法

【課題】フェーズロックループで使用可能なデジタル位相検知器において、サンプリングクロック信号を基準として高い位相分解能で入力クロック信号の位相を検知する。

【解決手段】サンプリングクロック信号はサンプリング14に対して、前もってデジタル的に調節可能な位相変位12へ露呈され、「補助サンプリングクロック信号」CK<1:8>が発生する。サンプリング14は位相検知信号PD OUTの第一のより上位のデジタルコンポーネントOUT1<9:0>を送給する。この第一のデジタルコンポーネントOUT1<9:0>の評価に基づいて、位相変位12が行われ且つ位相検知信号PD OUTの第二デジタルコンポーネントOUT2<12:0>が発生される。補助サンプリングクロック信号CK<1:8>は段階的に調節可能であり、それは各場合においてサンプリングクロック信号CKの1周期よりも小さい。

(もっと読む)

クロックデータ復元装置

【課題】より正確にクロック信号およびデータを復元することができるクロックデータ復元装置を提供する。

【解決手段】クロックデータ復元装置1は、入力したデジタル信号に基づいてクロック信号およびデータを復元する装置であって、イコライザ部10、サンプラ部20、クロック生成部30、イコライザ制御部40および位相モニタ部50を備える。イコライザ部10、サンプラ部20およびイコライザ制御部40によるループ処理により、イコライザ部10におけるデジタル信号のレベル調整量の制御が行われるが、一方で、クロック信号CKとデジタル信号との間の位相差が所定値より大きいときには当該制御が位相モニタ部50により停止される。これにより、より正確にクロック信号およびデータが復元され得る。

(もっと読む)

標準信号発生器及び標準信号発生システム

【課題】恒温設備を設けることなく位相ドリフトを低減させて、標準信号発生器のウォームアップ時間の短縮を図ること。

【解決手段】位相補正データ生成部4のA/D変換器41は、基準信号生成部1から出力された基準信号14aの周波数をサンプリング周波数として標準信号100aをA/D変換する。プログラマブル周波数ディバイダ42が分周した基準信号14aの周期で、データ間引き部43はA/D変換器41からのビート信号41aを間引き抽出する。補正量算出部40は、データ間引き部43からのビート信号43aの電圧値に基づいて、位相ドリフト量Δθdriftを算出する。その位相ドリフト量Δθdriftに基づいて標準信号100aの位相補正を行う。

(もっと読む)

複数個の出力信号を発生させるフェーズロックループ

【課題】入力クロック信号と同期した複数個の出力クロック信号を調節可能な相対的位相差でもって供給する。

【解決手段】制御可能なオシレータDCOがフェーズロックループの出力信号CKoutを発生し、且つ位相検知器PDがPLL12の入力クロック信号CKinとPLL出力信号CKoutとの間の位相差を決定し、且つオシレータDCOを使用されているクロック信号CKinと同期させる位相検知器出力信号を供給する。ここで、クロック信号CKinと同期されている調節可能な相対的な位相差を有する複数個のPLL出力信号を供給可能にするために、位相差の決定のためにPLLの出力信号CKoutの位相シフトをしたバージョンCK<1:8>を発生し且つ使用されているクロック信号CKinの位相と比較し、且つPLL出力信号CKoutの調節し位相シフトしたバージョンCK<1:8>を更なるPLL出力信号CK<1:8>として供給する。

(もっと読む)

スイッチ可能なフェーズロックループ及びスイッチ可能なフェーズロックループの動作方法

【課題】PLL及びPLLの動作方法に関し、制御可能なオシレータが出力信号を発生し且つPLLの入力クロック信号として使用するために第一クロック信号及び第二クロック信号の間でスイッチオーバーさせる。

【解決手段】現在使用されているクロック信号(CKin1又はCKin2)が出力信号を発生するために、このクロック信号と出力信号との間の位相差が決定され且つオシレータの制御のために使用され、一方現在使用されていないクロック信号(CKin2又はCKin1)が出力信号を発生するために、出力信号に関してのその周波数差が決定され且つ格納され且つ継続的にアップデートされ且つ、前に使用されていないこのクロック信号へのスイッチオーバーの後にオシレータの制御のために提供される。PLL出力信号はどのようなスイッチオーバーに関連する周波数変化よりも迅速に追従することが可能である。

(もっと読む)

ディジタル処理装置のノイズ低減方式

【課題】ディジタル信号処理回路によってPLLや周波数シンセサイザ等を構成するディジタル処理装置のノイズ低減を確実、容易にする。

【解決手段】PLLの位相比較演算を行うディジタル処理デバイス115をディジタル信号処理回路115A〜115Cで構成する周波数シンセサイザにおいて、ノイズ低減部115Dは、多数の論理回路要素がほぼ同時にオン/オフ動作するディジタルローパスフィルタ115Bと同等のオン/オフ動作になる回路構成にし、かつフィルタ115Bのオン/オフ動作と逆のオン/オフ動作させることでノイズを低減する。

(もっと読む)

周波数シンセサイザ

【課題】新規な原理により、広帯域に亘って細かく周波数を設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供すること。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを作成し、電圧制御発振部の出力周波数が設定値になったときのベクトルの周波数を予め計算しておいて、電圧制御発振部を駆動したときにベクトルの周波数と前記計算された周波数との差分に相当する電圧信号を電圧制御発振部にフィードバックして、その差分がゼロになるようにPLLを形成する。従ってPLLがロックされたときに電圧制御発振部の出力周波数が設定周波数に調整される。またPLLのロック後に両者の開きが大きくなった後は設定値を積分回路部により積分して制御電圧に加える。

(もっと読む)

PLL回路

【課題】ループフィルタの出力を上限値、下限値と比較して、PLL回路がロックしているかどうかを判定するロック判定回路の上限値、下限値が固定されているので、入力信号の周波数のずれや部品特性のばらつきによっては、キャプチャーレンジがこの上下限値から外れてロックしなくなるという課題を解決する。

【解決手段】ロックしたときのループフィルタの出力の上限値と下限値を上限値/下限値検出回路で検出して保持し、この保持した上下限値をリミット回路に入力し、このリミット回路でループフィルタの出力を前記上下限値の間の値に規制するようにした。ループフィルタの出力電圧が常にキャプチャーレンジ内に規制されるので、入力信号の周波数のずれや部品特性のばらつきに関わらず、確実にロックさせることができる。

(もっと読む)

PLL装置

【課題】外部からの基準周波数信号に電圧制御発振部からの周波数信号を同期させて出力するPLL装置において、外部からの基準信号に不具合が生じても周波数の変動が抑えられるようにすること。

【解決手段】外部からの基準周波数信号の信号レベルを監視し、その信号レベルが設定範囲内であるときには、位相差データ作成手段により作成された位相差に関するデータを用いてPLL制御を行うが、前記信号レベルが設定外れたときには、信号の供給が停止あるいは異常が起きたものと認識して記憶部に記憶されている位相差に関するデータ、例えば蓄積している最新のデータあるいは予め作成しておいたデータに切り替えてPLL制御を行う。

(もっと読む)

PLL装置

【課題】極めて高い周波数安定度が得られるPLL装置を提供すること

【解決手段】恒温槽付き水晶発振器(OCXO)から40MHzの矩形波である周波数信号によりA/D(アナログ/ディジタル)変換部により標準信号をサンプリングし、そのディジタル信号を直交変換部により直交変換処理し、標準信号とOCXOからの周波数信号との位相差に相当する位相のベクトルを複素表示したときの実数部分(I)及び虚数部分(Q)を取り出す。このベクトルの角速度を検出し、この角速度に対応する直流電圧をPWM制御部を介して生成し、OCXOに供給する。

(もっと読む)

位相比較器

【課題】フルレートとハーフレートの両方に対応した位相比較器を得る。

【解決手段】データ信号の立ち下がりタイミングでクロック信号の振幅値を検出する第一の検出手段1と、データ信号の立ち上がりタイミングでクロック信号の振幅値を検出する第二の検出手段2と、第一の検出手段1がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第一の識別結果を出力し、第二の検出手段2がクロック信号の立ち上がり状態又は立ち下がり状態の振幅値を検出しているのかを識別して第二の識別結果を出力するエッジ比較手段3と、第一の識別結果に応じて第一の検出手段1の出力の極性を反転する第一の極性反転手段4と、第二の識別結果に応じて第二の検出手段2の出力の極性を反転する第二の極性反転手段5と、データ信号の極性に応じて第一又は第二の極性反転手段4、5の出力値を選択して出力する信号選択手段6とを設けた。

(もっと読む)

ディジタル位相同期装置

【課題】入力された正弦波と周波数が等しく、かつ位相が同期した正弦波を、簡易で正確に、出力する装置を提供する。

【解決手段】位相差検出回路1は、外部から入力された第一の正弦波と正弦波生成回路5より出力する第二の正弦波との位相差を、ディジタル信号処理により算出する。その算出値に基づいて第二の正弦波の位相と周波数を調整するので、正弦波生成回路5は入力された第一の正弦波に周波数が等しく、かつ位相が同期した第二の正弦波を簡易に正確に出力することができる。

(もっと読む)

広い位相余裕を有するクロック及びデータリカバリ回路

【課題】動作速度が速くて位相誤差の小さいクロック及びデータリカバリ回路を提供する。

【解決手段】クロック及びデータリカバリ回路はサンプラ、位相比較器、ループフィルタ及び位相補間器を含む。サンプラは復元クロック信号に応答してシリアルデータをサンプリングしてシリアルサンプリングパルスを生成する。位相比較器はシリアルサンプリングパルスから変換されたパラレルデータを用いて相対的に低速の複数の位相信号を生成する。複数の位相信号はループフィルタを通過した後、相対的に高速である一つの位相制御信号として生成される。位相補間器は位相制御信号に応答して基準クロック信号の位相を進めるか遅らせるようにすることで復元クロック信号を生成する。複数個の低速位相信号を用いて高速の位相制御信号を生成するので、クロック信号と受信データ信号との間に周波数差異が大きい場合にもフィルタ回路動作周波数を低速で保持しながら位相余裕が大きいクロック及びデータリカバリ回路を実現することができる。

(もっと読む)

ビット検出装置及び情報再生装置

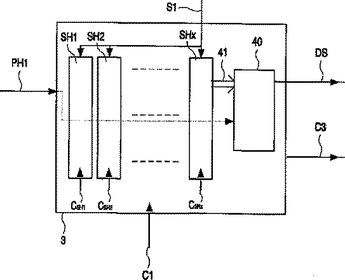

振幅を有するアナログ信号(AS)を、当該アナログ信号(AS)が導出されるビット列を表すデジタル信号(DS)に変換することができるビット検出装置が開示される。ビット検出装置は、量子化されたアナログ信号とクロック信号C2との間の位相差を検出する位相検出器を有する。位相差は、AD変換器によってサンプリングされる。前記位相差が低周波信号であるので、AD変換器は、比較的遅いレートでサンプリングすることができる。サンプリングされた位相差は、位相信号PH1を出力するデジタルPLLに供給される。位相信号及び量子化されたアナログ信号は、前記デジタル信号(DS)を再現するために用いられる。本発明は、前記ビット判断ユニットが更に、−クロック信号CSH2を用いて前記出力信号S1をサンプリングすることができる少なくとも1つの追加のサンプル及び保持ユニットSH2であって、前記クロック信号CSH2の周波数はクロック信号CSH1の周波数に等しく、前記クロック信号CSH2の位相は、前記クロック信号CSH1の位相とは大幅に異なる、サンプル及び保持ユニットSH2と、−前記のサンプル及び保持ユニットSH1又はSH2のサンプルを出力するための出力ユニットであって、前記位相信号PH1が前記位相差ΔP1は第1の領域にあることを示すときには前記サンプル及び保持ユニットSH1のサンプルが出力され、前記位相信号PH1が前記位相差ΔP1は第2の領域にあることを示すときには前記追加のサンプリング及び保持ユニットSH2のサンプルが出力される、出力ユニットとを有することにより特徴付けられる。これは、位相ジッタがある場合に発生するビットエラーの変更が低減されるという利点を有する。  (もっと読む)

(もっと読む)

ループ周波数関数としてのディレイもしくはフェーズロックドループをコントロールするための装置および方法

ディレイ ロックド ループ(Delay Locked Loop:DLL)もしくはフェーズ ロックド ループ(Phase Locked Loop:PLL)用の方法と回路が開示されている。かかる方法と回路は、処理、電圧、または温度の変化に関係なく、高周波数におけるループの安定性を改善し、また最大のトラッキング帯域幅を実現できる。技術の中心となるものは、クロック信号(1/tCK)である高い周波数においてではなくループ自身の固有の帯域幅(1/tLoop)に近い低い周波数においてループを効率的に動作させることである。そのようにするために、一実施例において、ループ遅延、すなわちtLoop,が、ループの動作前に計測されるか、あるいは予測される。続いて、位相検出器が、ループ周波数1/tLoopに近い周波数でイネーブルされる。簡単に言えば、位相検出器は、無用な遅延時間中は実働しないようにされており、その結果、ループが過剰反応したり、不安定になることを防ぐことができる。 (もっと読む)

信号発生装置

【課題】 ローカル信号の漏れ成分が位相周波数比較器に入力された場合であっても、スプリアスを発生させないようにする。

【解決手段】 サンプラ12に入力されるローカル信号Lを分周器21で分周して位相周波数比較器14に入力する構成とし、且つ、分周器21の分周比をN、低域通過フィルタ16の帯域の上限をfAとして、

fL/N>fA

fO=fL(K+1/N)またはfO=fL(K−1/N)

を満たす分周比Nと周波数fLとを求め、分周器21およびローカル信号発生器13にそれぞれ指定して、VCO11の出力信号の周波数を所望出力周波数fOにロックさせる。

(もっと読む)

位相同期装置及びデータ再生装置

【課題】

本発明は適切な初期位相誤差を算出することにより短時間で位相を同期できるようにする。

【解決手段】

本発明は、入力信号xkの位相を複数通りに変化させたシフトパターンiの位相変化信号θi(k)を生成するインターポレータ10と、各シフトパターンiにおける位相誤差Δτi′(k)をそれぞれ検出する位相誤差検出器70siと、各シフトパターンiにおける複数の位相誤差Δτi′(k)を基に平均値AViと標準偏差σiとをそれぞれ算出する平均算出器71si及び標準偏差算出器72siと、位相誤差Δτi′(k)の標準偏差σiが最小となるシフトパターンiにおける平均値AViを基に初期サンプリング位相μzprを算出する初期位相算出器75と、当該初期サンプリング位相μzprに応じて現位相を目標位相に近づけるインターポレータ10とを設けるようにした。

(もっと読む)

再生装置

【課題】 環境変化の影響を受けることなく、再生されたデジタルデータに位相同期したクロックを得る。

【解決手段】 記録媒体から情報信号を再生する再生手段と、前記再生手段から出力された再生信号をクロックに応じてサンプリングし、1サンプル複数ビットのデジタル信号に変換する変換手段と、前記変換手段から出力されたデジタル信号に対してパーシャルレスポンス(1、1)の処理を施し、その結果を2値判定して得られる連続した2サンプルのデータからなる2ビットのデータ中の特定のパターンを検出するパターン検出手段と、前記パターン検出手段の検出結果に応じて前記変換手段から出力されたデジタル信号を抽出し、前記再生信号と前記クロックとの位相差を示す信号として出力する抽出手段と、前記抽出手段の出力に応じて前記クロックを出力するクロック発生手段とを備える。

(もっと読む)

位相比較器、PLL回路、FLL回路、ビット同期回路、受信装置

【課題】 伝送信号のS/N比が低い場合であっても正確にビット判定を行うことができて、ビット誤りを低減可能な位相比較器、PLL回路、FLL回路、ビット同期回路、受信装置を提供する。

【解決手段】 位相比較器9は、積分器1〜3と、積分器1の出力と積分器2の出力との差を出力する加算器4と、積分器1の出力と積分器2の出力との和を出力する加算器5と、加算器4の出力の極性から各ビットを判定し、ビット判定結果を復調データSdとして出力するビット判定器6と、加算器5の出力の1/2(半値)と積分器3の出力との差を出力する加算器7と、加算器7の出力にビット判定器6の出力を乗じて位相誤差信号Spとして出力する乗算器8とから構成される。積分器1〜3は、前半積分区間信号Sa、後半積分区間信号Sb、中間積分区間信号ScがHレベルのときのみ積分動作を各々行う。

(もっと読む)

41 - 60 / 61

[ Back to top ]