Fターム[5J106CC25]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 位相比較(弁別)回路 (1,788) | サンプリング型 (61)

Fターム[5J106CC25]に分類される特許

21 - 40 / 61

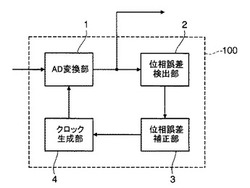

位相誤差検出装置、位相誤差検出方法、集積回路及び光ディスク装置

【課題】周波数誤差が生じているときでも±180度を越える位相誤差の検出を可能とし、PLLの安定性を向上させることができる位相誤差検出装置を提供する。

【解決手段】アナログ入力信号をサンプリングクロックに基づいてAD変換してデジタル再生信号を生成するAD変換部1の出力より位相誤差を検出する位相誤差検出装置は、AD変換部1の出力より前記位相誤差を生成する位相誤差生成部2と、位相誤差を補正する位相誤差補正部3とを含み、位相誤差補正部3は、過去の位相誤差により位相誤差検出範囲を決定し、位相誤差生成部2が生成した位相誤差が位相誤差検出範囲外であった場合に当該位相誤差を補正する。

(もっと読む)

デジタルクロック・データ復元機およびこれを適用したトランシーバー

本発明は、デジタルフィルタ回路(digital filter)とデジタル制御発振器(DCO;digitally controlled oscillator)を用いて回路全体をデジタル回路化したクロック・データ復元機に関するものであり、本発明に係るデジタル制御発振器は、複数個のインバータチェーンを備えており、それぞれのインバータに電源電流を供給する電源電圧とインバータの間に可変抵抗スイッチングマトリックスを構成して供給電源を変化させ、発振周波数をチューニングする。

ここで、可変抵抗スイッチングマトリックスは、PMOSトランジスタ配列を用いて具現化するものの、低いレベルでの周波数チューニングステップと高いレベルでの周波数チューニングステップを互いに均等化するために、スイッチングマトリックスの列と列の間に垂直抵抗を追加挿入している。また、ジッタ発生問題を解消するために、第1シグマデルタモジュレータを用いてディザリング回路を具現化しており、セグメントサーモメーター方式を適用して少ない個数のルーティングラインでデジタル制御発振器をチューニングしている。  (もっと読む)

(もっと読む)

高性能信号発生

【課題】高性能位相検出器は、プログラムで制御できる周波数および位相を有するデジタル基準信号を生成する局部デジタルオシレータを含む。

【解決手段】位相検出器は、デジタル基準信号とサンプリングされた入力信号の間の位相差を蓄積し、位相誤差の指標を作る。位相検出器は、周波数合成器において用いられ、低位相ノイズおよび正確な位相制御で信号を発生することができる利点がある。さらに、この種類のシンセサイザは、低ジッタのクロックおよび波形を生成するATEシステムおよび他の電子システムにおいて、ビルディングブロックのように用いられる。

(もっと読む)

位相同期回路、および通信装置

【課題】設定される動作モードに基づいて処理信号の処理クロック周波数を動作モードに基づいて切り替え、消費電力の低減を図ることが可能な位相同期回路、および通信装置を提供する。

【解決手段】デジタル値で表される発振制御信号に基づく発振周波数の発振信号を出力する発振回路と、搬送波周波数が基準周波数で除算された分周比と動作モードを規定する制御信号とが入力され、分周比を制御信号に基づいて設定された整数値で除算する第1ビットシフト部と、発振信号に基づく信号と制御信号とが入力され制御信号に基づいて設定された整数値により発振信号に基づく信号を分周する第1分周部と、基準周波数信号の各周期において第1累積加算値と第2累積加算値および累積位相の小数部とを比較し位相比較信号を出力する位相比較部と、位相比較信号を制御信号に基づく任意の収束値に収束させ発振制御信号を出力するデータ変換部とを備える位相同期回路が提供される。

(もっと読む)

制御装置、クロック同期方法

【課題】DPLL回路において、入力クロックの瞬間的な位相跳びによる出力クロックの位相跳びの発生を抑制する。

【解決手段】出力クロックを入力クロックに同期させる制御を行う制御装置は、前記入力クロックと前記出力クロックとの位相差をカウントするカウント部と、前記カウント部がカウントした位相差のうち、所定範囲内の位相差を示すカウント値を抽出する抽出部と、抽出された前記所定範囲内の位相差を示すカウント値に基づいて位相差情報を生成する位相差情報生成部と、前記位相差情報生成部により生成された前記位相差情報に基づいて、生成する前記出力クロックの周波数を制御可能なクロック生成部と、を備える。

(もっと読む)

位相比較器、PLL回路、及び位相比較器の制御方法

【課題】電圧制御発振器VCOの出力信号と参照信号との位相差をデジタル信号として高精度に検知できる位相比較器、PLL回路、及び位相比較器の制御方法を提供する。

【解決手段】各々複数段縦列接続され、基準信号および対象信号が入力される遅延回路と、各々の段の遅延時間の差により、基準信号と対象信号との位相差を出力する保持回路と、その出力結果を元に、遅延素子の時間差及び大小を変更する論理回路とを備えた。

(もっと読む)

信号再生回路向け位相比較回路及び信号再生回路向け位相比較回路を備える光通信装置

【課題】 1/Nレート構成に対応可能な高精度な位相比較回路を得る。

【解決手段】それぞれ、N相クロック信号CLKの各クロック信号を、受信データ信号DINの立ち上がりに同期してトラックホールドするN個のトラックホールド回路を備える。これらのN個のトラックホールド回路の出力から、受信データ信号DINの立ち上がりエッジが、クロック信号CLKの立ち上がりエッジに位置しているクロック信号をトラックホールドしているもののみをセレクタで選択して、位相差信号として出力する。

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

冗長構成システムにおける基準信号同期制御方法

【課題】運用系と待機系の位相差を正確に求めることが出来る冗長構成システムにおける基準信号同期制御方法を提供することである。

【解決手段】装置の基準信号を生成し、運用系と待機系の冗長構成を成すユニットにおいて、運用系のハードウェアと、待機系のハードウェアで、同じタイミングの基準信号を用いて装置を動作させるために、運用系から出力する基準信号は、各機能部の他、待機系にも送り、待機系は、運用系から入力される基準信号と自ら生成する基準信号との位相差を、運用系から待機系までの遅延を擬似的に実現させ、そこから求められた遅延量に従い、待機系が生成する基準信号に遅延分のオフセットをかけることで、運用系の基準信号と同期させる。

(もっと読む)

信号処理装置、信号処理方法、信号処理プログラム及びその記録媒体

【課題】

演算量を低減しつつ、入力信号に精度良く同期した信号を迅速に生成する。

【解決手段】

直交信号生成部110Aが、信号源910AからのサンプルレートfSM1でサンプリングされた信号SIAに含まれる角周波数ωCのパイロット信号の位相を反映し、互いの直交化が図られ、サンプルレートfSM2(<fSM1)でサンプリングされた信号PWA1,PWA2を生成する。これらの信号PWA1,PWA2に基づいて、位相算出部120Aが、パイロット信号の位相を算出する。こうして算出されたパイロット信号の位相をサンプルレートfSM1に戻した後、パイロット信号の位相に基づいて、基準信号発生部130Aが、パイロット信号と所定関係にある基準信号BSAを生成する。そして、基準信号BSAを利用して、信号加工部140が、信号SIAを加工する。

(もっと読む)

マルチチャネル・データ検出システム用に構成されたエラー組み合わせ論理およびエラー信号を生成するための方法

【課題】 各チャネル用のフェーズ・ロック・ループを有するマルチチャネル・データ検出システムの位相エラー組み合わせ論理を提供することにある。

【解決手段】 この位相エラー組み合わせ論理は、各チャネルに関する位相エラー情報を受信することと、受信位相エラー情報を結合し、結合された位相エラーを生成するように構成された組み合わせ論理と、結合された位相エラーを少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成された位相エラー出力とを含む。さらに、エラー信号組み合わせ論理は、各チャネルに関するフェーズ・ロック・ループに関連する信号のエラー情報を受信することと、受信エラー信号情報を結合し、結合されたエラー信号を生成し、たとえば、信頼性情報により、各チャネルからの受信エラー信号情報に重みを付けるように構成された組み合わせ論理とを含む。エラー補償出力は、結合され重みが付けられたエラー信号を少なくとも1つのチャネル・フェーズ・ロック・ループに適用するように構成される。

(もっと読む)

ジッタ検出回路及び半導体装置

【課題】サイクルトゥサイクルジッタの程度を検出する。

【解決手段】PLL回路(2)の発振クロック信号(vco)の遅延信信号を基準クロック信号(ref)の複数の遅延信号の変化に同期して複数のラッチ回路(23_1〜23_n)にラッチする。ラッチ回路毎にその出力又はその反転信号をセレクタ(24_1〜24_n)で選択する。セレクタ毎にその出力の変化回数をカウンタ(25_1〜25_n)で計数する。制御回路(28)は、発振クロック信号の2nサイクル毎に、前回のセレクタの選択が非反転出力であれば今回カウンタの計数値がn以上のときセレクタの選択状態を反転し、前回のセレクタの選択が反転出力であれば今回前記カウンタの計数値がn以上のときにセレクタの選択状態を反転する。前記第1カウンタの計数値が例えばジッタ検出情報として出力される。

(もっと読む)

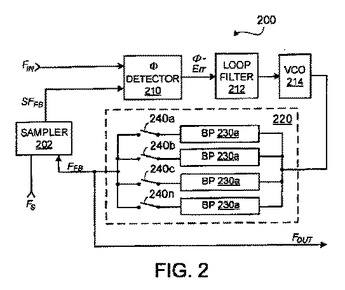

偽信号化された周波数上の位相ロック

位相ロックループ(200)は、サンプラー(202)、位相検出器(210)、ループフィルタ(212)、VCO(214)を含む。ループは、ループのフィードバックパス中に分割器を必要とすることなく周波数逓倍を達成する。VCO(214)は、サンプラーのナイキストレートより上で動作され、ループが偽信号化された信号上にロックすることを引き起こす。VCO出力周波数中のあらゆる変動(即ち、ジッターまたは位相ノイズ)は、周波数分割器に通常関連付けられる減衰無しで、1対1で位相検出器(210)にフィードバックされる。ループゲインは従って、高い閉ループ周波数逓倍を提供するループにおいてでも、高く保つことができる。一変形によると、高調波発生器(540)がVCOとサンプラーの間に置かれ、よってループがVCO周波数の高調波上にロックすることを引き起こす。開ループゲインと精度はよって更に向上される。  (もっと読む)

(もっと読む)

クロック生成回路、記録装置及びクロック生成方法

【課題】入力信号の欠落により発生する出力クロック信号のずれを適切に補正しつつ、入力信号に同期した出力クロック信号を生成することができるクロック生成回路を提供する。

【解決手段】所定の周波数を有する入力信号を所定の逓倍比で逓倍して出力クロック信号を生成するクロック生成回路10を提供する。このクロック生成回路10は、入力信号を逓倍して出力クロック信号を生成するPLL回路100と、PLL回路100の逓倍比を変更する補正回路200と、を備え、補正回路200は、入力信号に同期した入力同期信号と出力クロック信号に同期した出力同期信号との時間差が減少するにように、入力信号の1周期より長い補正周期毎の補正区間においてのみPLL回路100の逓倍比を所定の逓倍比から当該所定の逓倍比を増加又は減少した逓倍比に変更し、PLL回路100は、補正区間において、変更された逓倍比で入力信号を逓倍する。

(もっと読む)

電圧制御発振器を内蔵したPLL(PhaseLockedLoop)回路の位相差検出回路

【課題】低電圧動作時においても、VCO信号と基準信号との位相差を検知し、その位相差に対応したデジタル信号を生成する位相比較器を提供する。

【解決手段】基準信号と対象信号との位相差をデジタル信号として出力する位相比較器において、前記位相差に対応したパルス幅の信号により第1容量素子を充電することによって前記位相差を電荷として検出する第1検出手段と、前記基準信号の周期に対応したパルス幅の信号により第2容量素子を充電することによって基準となる時間差を基準電荷として検出する第2検出手段と、前記第1検出手段により検出された電荷と前記第2検出手段により検出された電荷とを比較する電荷比較手段と、前記電荷比較手段による比較結果により、前記第2容量素子に充電された電荷に対する前記第1容量素子に充電された電荷の比をデジタル信号として出力する出力手段と、を備える。

(もっと読む)

デジタルシンセサイザ

【課題】位相比較器および信号発振器をデジタル化することによって短時間に同期を確立し、同期状態を高精度でしかも高安定に保持することができるデジタルシンセサイザあるいはデジタル同期発振器を提供する。

【解決手段】少なくとも、デジタル位相比較器21と、デジタル制御発振器22と、分周器23から構成する。

【効果】通信システムにおいて同じ周波数であることが必須の2つの入力信号の間で短時間に同期を確立し、入力信号が停止した場合あるいは取去られた場合にも、同期状態を高精度でしかも高安定に保持する。

(もっと読む)

パルス無線受信装置および同期方法

【課題】NRZ符号化されたパルス信号に対しても同期可能であり、かつ従来のEarly/Late DLL方式に比べフィンガー数を削減したパルス無線受信装置および同期方法を提供する。

【解決手段】相対差算出手段1505は、最大値検出手段1551A、1551Bと最小値検出手段1552A、1552Bおよび加算手段1553A、1553B、1554を備える。最大値検出手段1551Aは、サンプル手段1504から入力される連続したn個のサンプル値1504Aから最大値を検出し最大値Amaxを出力する。同期制御手段1506は、相対差算出手段1505からの相対振幅差信号iVをもとに包絡線信号とク

ロック信号のタイミングが同期するように、クロック信号の位相を制御する遅延制御信号を生成し、遅延手段1503へ出力する。

(もっと読む)

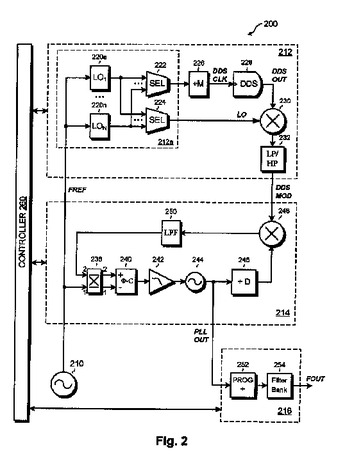

コスト的に有効な低ノイズの単一ループシンセサイザー

低コストで低位相ノイズのマイクロ波シンセサイザーは、DDS変調回路と位相ロックループを含む。DDS変調回路はDDSの出力を高周波数に変調する。位相ロックループはDDS出力をダウンコンバートし、ダウンコンバート信号を比較的低周波数の固定されたリファレンスにロックする。  (もっと読む)

(もっと読む)

位相比較回路

【課題】遅延時間が短く、しかも、メタステーブルが起こった場合において確実に後段回路の誤動作を防ぐことができる位相比較回路を提供する。

【解決手段】D-F/F21は外部クロック信号CLK1を制御クロック信号RCLKに基づいて読み込む。インバータINVA1、INVB1はスレショルドレベルが異なるインバータであり、インバータ22の出力を反転して出力する。インバータINVA2、INVB2はヒステリシス特性を有するインバータであり、インバータINVA2、INVB2の出力を反転して出力する。EX-NOR回路30、Dラッチ31、アンドゲート32は、インバータINVA2、INVB2の出力が一致している時、遅延回路33の出力をD-FF23および遅延回路34へ加え、一致していない時はオフとする。D-F/F23はアンドゲート32を介して供給される制御クロック信号RCLKの遅延信号に基づいてインバータ22の出力を読み込み出力する。

(もっと読む)

無線装置

【課題】パルスの形状が変動しても、正確な波形サンプルが可能な無線装置を提供する。

【解決手段】入力信号とクロック信号を同期させる同期装置は、入力信号を、所定の間隔の第1と第2のサンプルタイミングでサンプルするサンプル手段102,103と、同期引き込み時に、第1と第2のサンプルタイミングをともにずらし、同期追従時に、第1と第2のサンプルタイミングの間隔を狭める遅延制御手段112とを備える。同期状態判定部105は位相誤差算出部104から出力された位相誤差量から同期しているか否かを判定し、遅延量制御部106に同期状態を出力する。遅延量制御部106は位相誤差算出部104から出力される位相誤差量と同期状態判定部105から出力される同期状態から、可変遅延器107および108に現在設定している遅延量の増減を制御する。

(もっと読む)

21 - 40 / 61

[ Back to top ]