Fターム[5J106CC34]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−主要構成 (7,414) | 周波数比較(弁別)回路 (250) | 基準信号と比較 (33)

Fターム[5J106CC34]に分類される特許

1 - 20 / 33

自励発振型D級アンプおよび自励発振型D級アンプの自励発振周波数制御方法

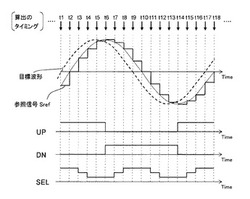

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。

(もっと読む)

水晶発振器

【課題】OCXOにおいて、水晶振動子及び発振回路の置かれている雰囲気温度を高い精度でコントロールし、出力周波数について高い安定度が得られること。

【解決手段】第1及び第2の水晶振動子10、20の発振出力をf1、f2とし、基準温度における前記発振出力の発振周波数を夫々f1r、f2rとすると、周波数差検出部3により、{(f2−f1)/f1}−{(f2r−f1r)/f1r}を演算する。この値を34ビットのディジタル値で表わすことにより温度に対応してディジタル値を得ることができる。従ってこの値を温度検出値として取り扱い、温度設定値との差分をループフィルタ61に供給し、ここからのディジタル値を直流電圧に変換し、ヒータ5を制御する。更に前記温度検出値に基づいて、OCXOの設定周波数を補正し、雰囲気温度が基準温度からずれたことによる周波数の変動分を補償するようにする。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

位相周波数比較回路及びPLL回路

【課題】入力クロックが停止しても出力クロックの周波数を保持するPLLを用いて、ロジック回路を駆動する方法を提供する。

【解決手段】位相周波数比較回路をPFD主要部と基準クロック停止検出部202Bの二つのモジュールから構成する。基準クロック停止検出部202BはPFD主要部のRS−FFのデータ端子に基準データ信号pfd_in_enを出力する。この基準データ信号pfd_in_enは、基準クロック停止検出部202B内のフリップフロップ202B−1に由来して生成される。このフリップフロップ202B−1は位相比較動作の終了を表すオーバラップ信号overlapをタイミングとし、基準クロックref_clkによってリセットされる。基準クロックref_clkが停止すると、基準データ信号pfd_in_enは「L」のままとなり、結果PFD主要部の動作が停止する。

(もっと読む)

発振回路

【課題】従来の発振回路では、出力信号のジッタを抑制できない問題があった。

【解決手段】本発明の発振回路は、発振周波数設定電流に基づき蓄積された電荷量に応じて発振周波数制御電圧Vcpを生成するフィルタコンデンサCpumpと、発振周波数制御電圧Vcpに応じて出力する発振信号Foutの周波数を変動させる発振器30と、発振信号Foutの周期に基づき論理レベルが切り替えられるタイミング制御信号を生成する制御回路40と、タイミング制御信号に基づき発振信号Foutの周期の長さに応じて連続的に電圧レベルが変化する周波数検出電圧Vcapを生成する周波数検出回路10と、周波数検出電圧Vcapと基準電圧Vresとの電圧差に応じて発振周波数設定電流を連続的に可変してフィルタコンデンサCpumpに出力する差動増幅器20と、を有する。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

基準周波数発生装置

【課題】ユーザ側装置で立上りタイミングが一致した2つの信号を容易に得られる基準周波数発生装置を提供する。

【解決手段】基準周波数発生装置は、ユーザ側装置へ10MHz及び1Hzの信号をそれぞれ出力する2つの出力端子と、ユーザ側装置から戻された上記信号をそれぞれ入力する2つの入力端子と、を備える。基準周波数発生装置を初めてユーザ側装置に接続したときは、2つの出力端子から出力される波形は何れも、その立上りタイミングがUTCの1秒に正確に同期している。この基準状態で、出力する1Hzの波形と、ユーザ側装置から戻された1Hzの波形との間で、立上りタイミングの差が測定される。また、ユーザ側装置から戻された1Hzの波形と、同様に戻された10MHzの波形との間で、立上りタイミングの差が測定される。CPUは、得られた時間差に基づき、10MHz及び1Hzの出力信号波形の位相を所定の関係に従って調整する。

(もっと読む)

PLL回路、PLL回路無線通信機、及びPLL回路のロック検出方法

【課題】デジタル回路で構成出来、ロック検出のエラーやロストの発生を抑制することが出来ると共に、検出時間を短縮することが出来るPLL回路、無線通信機、及びロック検出方法を提供する。

【解決手段】ウィンドウ幅の異なる複数のロック検出部6b−1〜6b−nによる検出結果を用いて検出を行う。ロック判定部7は、複数のロック検出部6b−1〜6b−nによる検出結果に基づいて、ロック状態の検出を行う。

(もっと読む)

ジッタ発生装置

【課題】本発明は、ジッタ抑制分を加味することなく、ジッタを付加することが出来るジッタ発生装置を実現することを目的にする。

【解決手段】本発明は、一方の入力に基準信号を入力し、他方の入力と位相比較を行い、位相差が閾値未満のとき、位相比較結果を出力しない位相比較器と、この位相比較器の出力を入力とするローパスフィルタと、このローパスフィルタの出力を入力とする電圧制御発振器と、この電圧制御発振器の出力を入力とし、位相比較器の他方の入力に出力する帰還回路と、ローパスフィルタの前後の少なくとも一方に設けられ、ジッタ信号を入力信号に加算し、出力する加算器とを備えたことを特徴とするものである。

(もっと読む)

フィルタ回路

【課題】本発明は、フィルタリング特性調整機能を有するアナログフィルタを有するフィルタ回路に関し、アナログフィルタのフィルタリング特性を簡易な補正回路によって補正する機能を備える。

【解決手段】アナログフィルタ50と、レプリカ回路としての発振器61と、周波数比較ロジック62を備え、周波数比較ロジック62で、その発振器61の発振周波数が基準周波数となるように、発振器61とアナログフィルタ50との双方を同時に調整する。

(もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

位相同期回路並びに記録再生装置および電子機器

【課題】位相同期回路において、ωn,ζを自由に変更可能でかつキャリブレーション可能にする。

【解決手段】ループフィルタ部106を抵抗素子162と容量素子164の直列回路で構成する。抵抗素子162は差動出力の第1ループフィルタ駆動部104_1(差動出力チャージポンプ回路DOCP)で駆動し、容量素子164はシングルエンド出力の第2ループフィルタ駆動部104_2(シングルエンドチャージポンプ回路SECP)で駆動する。発振部101は、ノードND101の電圧に基づき発振するようにする。発振部101の発振ゲインを補正するキャリブレーション部CALIB を設ける。抵抗回路や容量回路をスイッチングすることなく、ωn,ζを自由に変えられる。ループフィルタは、一方をシングルエンド、他方を差動で駆動すると、抵抗回路や容量回路の各両端に発生する電圧が独立になり、ωn,ζのキャリブレーションがし易くなる。

(もっと読む)

発振装置、受信装置および発振制御方法

【課題】発振周波数の制御の精度を向上させる。

【解決手段】検出部11は、基準信号の入力信号に対する周波数オフセットを検出する。コード生成部12aは、検出部11による周波数オフセットの検出状況に基づいて、所定ビット数のコードと周波数オフセットおよびDAC12bが電圧制御発振器13に印加する電圧との対応関係を設定する。また、コード生成部12aは、設定した対応関係に基づいて、周波数オフセットを補正する所定ビット数のコードを生成する。DAC12bは、コード生成部12aが生成したコードと上記の対応関係に基づいて、電圧制御発振器13に電圧を印加する。電圧制御発振器13は、DAC12bにより印加された電圧に応じた発振周波数の発振信号を出力する。

(もっと読む)

周波数補正回路及びそれを用いた無線通信装置

【課題】 発振器の出力周波数が増減した場合に自動補正を可能として常に出力周波数の精度を一定の範囲内に維持する周波数補正回路を得る。

【解決手段】 発振器2の発振周波数よりも高精度の基準周波数を、発振周波数を分周した分周周期毎に計数するカウンタ5と、発振周波数が正常な時のカウンタの計数値に相当する正常値に対して所定値Mを加算した値とカウンタの計数値とを比較して一致したときに発振周波数の減少を示す信号を生成する比較回路7と、正常値に対してMを減算した値とカウンタの計数値とを比較する比較回路8と、この比較回路8の一致結果に応答してこの一致結果を所定時間マスクするためのマスク信号を生成する単安定マルチバイブレータ11と、比較回路7の減少を示す信号に応じて発振周波数を減少方向に制御し、マスク信号の非生成時に発振周波数を増加方向に制御する制御回路12及びCPU1とを含む。

(もっと読む)

電子機器

【課題】発振子ごとに周波数偏差を0ppmに自動的に合わせ込むことにより、安定した発振周波数を得るとともに、温度偏差も考慮することでさらに安定した発振周波数を得る。

【解決手段】システムコントローラ10は、接続端子T4に周波数カウンタ101が接続されたタイミング、またはリモコン11からの指示信号に基づいて水晶発振子Zを発振させることにより当該水晶発振子Zの発振周波数を調整する調整モードに移行し、周波数カウンタ101によってカウントされた発振周波数が内部に設定されている基準発振周波数と一致するように制御端子T3の印加電圧を制御するとともに、一致したときの印加電圧値をフラッシュメモリ6に記憶して調整モードを終了。以後の機器の動作時には、フラッシュメモリ6に記憶されている印加電圧値を制御端子T3から印加して発振回路17からクロック信号を取得する。

(もっと読む)

デジタル周波数検出器及びこれを用いたデジタルPLL

【課題】デジタルPLLや周波数シンセサイザなどに使用されるデジタル周波数検出器及びこれを用いたデジタルPLLを提供する。

【解決手段】本デジタル周波数検出器は、第1周波数のハイレベル区間に動作する第1リングオシレータを利用して、第1周波数をデジタル形式の第1周波数情報として出力する第1変換部と、第2周波数のハイレベル区間に動作する第2リングオシレータを利用して、第2周波数をデジタル形式の第2周波数情報として出力する第2変換部と、第1周波数情報及び第2周波数情報の比を演算し、第1周波数に対するデジタル周波数を出力する演算部と、を含む。

(もっと読む)

周波数同期システム及び周波数同期方法

局部発振器からの局部信号と遠隔発振器からの基準クロック信号の間で周波数を同期させるデジタル周波数ロックループに関連するシステムおよび方法。基準カウンタは、基準クロック信号内のパルスごとにその計数を増分する。基準カウンタ内の値は、設定可能な基準値と比較される。基準カウンタ値と基準値の一致が発生するたびに、ヒット信号が生成され、基準カウンタ値が再初期化される。上記と同時に、局部信号からのパルスごとにフィードバックカウンタが増分される。ヒット信号が生成されると、フィードバックカウンタ内の値が設定可能なフィードバック値と比較(減算による)されて、差の値を生成する。次いで差の値が、局部発振器の周波数を増大または減少させるのに使用するための周波数調整信号に変換される。ヒット信号はまた、フィードバックカウンタを再初期化する。 (もっと読む)

1 - 20 / 33

[ Back to top ]