Fターム[5J106DD01]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 波形・レベル変換回路 (375)

Fターム[5J106DD01]の下位に属するFターム

Fターム[5J106DD01]に分類される特許

21 - 34 / 34

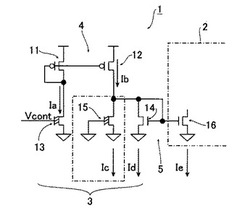

電圧制御発振回路

【課題】電圧電流変換部の制御電圧入力用MOSトランジスタにデプレッション型を使用した際に発生する発振周波数(バイアス電流)オフセットの製造プロセスばらつきが補正された電圧制御発振回路を提供する。

【解決手段】電圧制御発振回路1は、制御力電圧がゲートに入力される第1のデプレッション型MOSトランジスタ13と、その第1のデプレッション型MOSトランジスタ13のゲート・ソース間電圧が0Vのときのオフセットを補償する第2のデプレッション型MOSトランジスタ15を有し、制御電圧に応じたバイアス電流を発生する電圧電流変換回路3を備える。

(もっと読む)

PLL回路及び信号送受信システム

【課題】出力クロック信号のジッタ値に対するプロセスばらつきによる影響を抑える。

【解決手段】PLL回路として、基準クロック信号と出力クロック信号に基づくフィードバッククロック信号との間の位相差を検出する位相周波数比較回路と、前記位相差に応じて電流を出力するチャージポンプ回路と、前記チャージポンプ回路の出力を平滑化し、制御電圧として出力するローパスフィルタと、前記制御電圧、ゲイン制御信号、及びオフセット制御信号に応じた周波数の信号を生成し、前記出力クロック信号として出力する電圧制御発振回路と、前記制御電圧の変化に対する前記出力クロック信号の周波数の変化の比が目標値になるように、前記ゲイン制御信号を求めるゲイン調整回路と、前記制御電圧が所定の値である時における前記出力クロック信号の周波数が目標値になるように、前記オフセット制御信号を求めるオフセット調整回路とを備える。

(もっと読む)

発振装置および周波数検出装置

【課題】 中心周波数と周波数可変範囲を自在に設定できる高安定、高精度な電圧制御発振器を提供すること。

【解決手段】 第1の水晶発振器の第1の周波数成分と、第2の水晶発振器の第2の周波数成分とを加算器等で加算する等して、所望の中心周波数および所望の可変周波数範囲を作る。

(もっと読む)

リアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器

【課題】低消費電流および安定動作を実現することができるリアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器を提供すること。

【解決手段】水晶発振回路11と、該水晶発振回路11の出力を分周する計時回路(高速部)13と、計時回路(高速部)13の出力を分周する計時回路(低速部)14と、外部との間で信号のやり取りをするインターフェース回路15からなり、水晶発振回路11は第一の電圧VR1で駆動され、計時回路の少なくとも一部分(高速部)13は第二の電圧VR2で駆動され、計時回路の残りの部分およびインターフェース回路15は第三の電圧VDDで駆動され、第一の電圧VR1<第二の電圧VR2<第三の電圧VDDの大小関係を有する。第一の電圧VR1と第二の電圧VR2は第三の電圧VDDから生成される。

(もっと読む)

半導体装置

【課題】 PLL回路の出力の張り付きを防止する。

【解決手段】 半導体装置1には、入出力回路部2、アナログ回路部3、デジタル回路部4、入力端子PIN、制御端子PCTL、及び電源端子PVccが設けられている。アナログ回路部3には、第1の電源回路11、第2のレベルシフト回路16、位相周波数比較器17、チャージポンプ回路18、ループフィルタ19、及び電圧制御発振器20が設けられ、デジタル回路部4には、第2の電源回路12、第1のレベルシフト回路15、分周回路7、及び論理回路・メモリ部6が設けられている。アナログ系電源が供給され、デジタル系電源が供給されないとき、第1のレベルシフト回路15がONしないので、位相周波数比較器17はリセットされず動作を開始しない。

(もっと読む)

トリガ信号発生装置

【課題】入力信号に同期し、ジッタの少ないトリガ信号を生成するトリガ信号発生装置を実現することにある。

【解決手段】入力される入力信号よりも低い周波数のトリガ信号を出力するトリガ信号発生装置に改良を加えたものである。本装置は、入力信号を分周する分周回路と、この分周回路で分周された信号を入力信号に同期させる同期化手段を有する同期化回路とを設けたことを特徴とするものである。

(もっと読む)

DRAMの動作周波数を高める遅延固定ループ

【課題】入力クロックの周波数が高まっても、第2DLLクロックFCLK_DLLOEにより、ライジング/ポーリングアウトイネーブル信号R/FOUTENを生成することができる動作マージンを確保することにより、DRAMの動作周波数を高めることができる遅延固定ループを提供すること。

【解決手段】本発明の出力ドライバーは、遅延固定ループから出力されたクロックを受信し、読み出しデータの出力に用いられる第1DLLクロックを生成し、第1タイミング遅延によってドライビングする第1ドライビング部と、前記遅延固定ループから出力されたクロックを受信し、書き込み動作時の電流消費の低減のために用いられる第2DLLクロックを生成し、前記第1タイミング遅延より少ない第2タイミング遅延によってドライビングする第2ドライビング部とを備えることを特徴とする。

(もっと読む)

PLL回路

【課題】 電圧電流変換回路の抵抗値のばらつきを抑えることで、電圧制御発振器の発振周波数のばらつきを低減するPLL回路を提供する。

【解決手段】 電圧電流変換回路50は可変抵抗回路4と、リミット回路5と、カレント比調整回路6を備えて構成される。可変抵抗回路4を内蔵することで抵抗を内蔵した場合のプロセスばらつきを制御でき、かつ内蔵することで、外付抵抗端子の寄生容量の影響を受けずに済み、PLLループ帯域の影響を受けない高帯域で応答可能な電圧電流変換回路が実現できる。この可変抵抗回路4にCMOS可変抵抗を用いることで連続的な抵抗値調整を可能とする。

(もっと読む)

タイミング発生器、試験装置、及びタイミング発生方法

【課題】遅延量を精度よく測定し、遅延量が精度よく制御されたタイミング信号を発生するタイミング発生器、半導体試験装置、及びタイミング発生方法を提供する。

【解決手段】所定の周波数を発生する基準信号発生部と、基準信号を所定の時間遅延させたタイミング信号を出力する可変遅延回路部と、可変遅延回路部の遅延量を測定する遅延量測定部とを備え、遅延量測定部が測定した遅延量に基づいて可変遅延回路部の遅延量を制御するタイミング発生器において、基準信号の周波数を微小周波数範囲で連続的に変調させることにより、遅延量測定部が精度よく可変遅延回路部の遅延量を測定することができる。また、測定した遅延量に基づいて可変遅延回路部の遅延量を制御することにより、精度よく遅延されたタイミング信号を発生することが可能となる。

(もっと読む)

電流ミラー回路を有する電荷ポンプを用いた位相ロックループ回路

位相ロックループを行なうためのシステムおよび方法が開示される。このシステムは、位相周波数検出器回路と、第1の電流ミラー回路(305)および第2の電流ミラー回路(310)を有する電荷ポンプ回路(225)と、ループフィルタ回路と、電圧制御発振器回路とを含む。位相周波数検出器回路は、入力信号とフィードバック信号との位相差に基づいてアップ信号およびダウン信号を生成する。第1および第2の電流ミラー回路(305,310)は基準電流(340)を複製する。バイアス回路(315)は、第2の電流ミラー回路(310)への電圧バイアスに基づいた、第1の電流ミラー回路(310)のための電圧を、第1の電流ミラー回路のための電圧と回路の電圧とに基づいて生成するよう構成されており、基準電流(340)を低電力で正確に複製し、それにより、等しい大きさの電流パルスを低電流で供給する。  (もっと読む)

(もっと読む)

位相同期回路

【課題】 アナログ信号をデジタル信号に変換することなく、そのアナログ信号の位相を可変することができるとともに、そのアナログ信号が高周波の信号でも、そのアナログ信号の位相を可変することができるようにする。

【解決手段】 4相の信号の中から、基準信号との位相差が90度以内の2相の信号を選択するための位相検出回路5及びスイッチ部6と、その2相の信号のレベルをそれぞれ調整するレベル調整器7a,7bと、レベル調整後の2相の信号を合成する合成器8とを設け、その合成器8により合成された信号の位相が基準信号の位相と一致するように、そのレベル調整器7a,7bによるレベルの調整具合を制御する。

(もっと読む)

クロック変換器、変調器、及びデジタル放送用送信装置

【課題】変調器に入力されるクロックが10MHzの場合でも、現用/予備両系の変調器間で波形及び位相が一致した出力信号を得る。

【解決手段】 クロック変換器20は、10MHzのクロックを2/63MHzに分周する1/315分周器21と、512/63MHzのクロックを発振し、その発振周波数を電圧信号に応じて制御するVCO24と、VCO24からの512/63MHzのクロックを1/256に分周する1/256分周器25と、両分周器21、25の出力クロックを比較しその位相差に応じて前記電圧信号となるパルス信号を出力する位相比較器23と、デジタル放送用の多重フレームの周期を示すフレーム同期信号、及び10MHzのクロックを入力し、フレーム同期信号のパルス波形を10MHzのクロックに同期して整形し、整形された信号を前記リセット信号として出力する波形整形器22とを有する。

(もっと読む)

位相同期回路および情報再生装置

【課題】周波数比較精度の向上を図れ、安定かつ高速な周波数引き込みを実現することが可能なPLL回路および情報再生装置を提供する。

【解決手段】VCO23による3相クロックCLKA,CLKB,CLKCに同期してヒステリシスコンパレータ24によるヒステリシス信号HYCを取り込み、以降、たとえば第1相クロックCLKAに同期して、入力データ信号のヒステリシスのエッジがどの位相からどの位相に変化したか観察することにより周波数が高いか低いかを周波数誤差として検出する際に、ヒステリシスコンパレータ24にて取り除くことができなかった2Tパターンを、VCO23による3相クロックCLKA,CLKB,CLKCに同期してパルスの周期計測を行うことにより除去し、これにより検出結果に基づいたアップ信号UPまたはダウン信号DOWNをチャージポンプ回路26に出力する周波数比較器25を有する。

(もっと読む)

通信システム、通信装置、リファレンスクロック発生器、およびそのクロック発生方法

【課題】 基準クロックに障害が発生してもリファレンスクロックの出力が途切れないリファレンスクロック発生器を提供する。

【解決手段】 加算器3に入力される2つの基準クロック再生回路1a、1bの出力のうち、基準クロック再生回路1bの出力をレベル調整部2を介して振幅を調整し、異なる振幅のクロックをアナログ加算して逆相となる基準クロック再生回路1a、1bの出力が入力されても加算出力が零になることを防ぎ、その加算出力を波形整形器4を介してリファレンスクロックを生成、出力することにより入力する一方の基準クロックに障害が発生してもリファレンスクロックの出力が途切れないリファレンスクロック発生器が提供できる。

(もっと読む)

21 - 34 / 34

[ Back to top ]