Fターム[5J106DD05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 波形・レベル変換回路 (375) | 増幅回路 (201)

Fターム[5J106DD05]の下位に属するFターム

コンパレータ (96)

Fターム[5J106DD05]に分類される特許

1 - 20 / 105

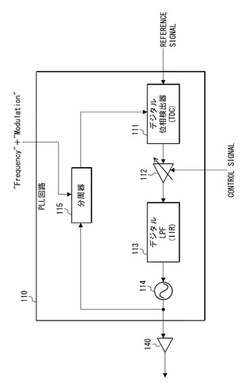

半導体装置及びこれを搭載する無線通信端末

【課題】回路規模の増大を抑止しつつ、ループ帯域の切替に際して生じるオフセットを補償する。

【解決手段】半導体装置(110)を構成する位相検出器(111)は、発振器(114)の出力信号を帰還した帰還信号と参照信号との間の位相差を検出し、位相差に応じた値を示す位相差値を生成する。増幅器(112)は、外部からの制御信号に応じて決定される増幅率で、位相差値を増幅する。フィルタ(113)は、増幅器(112)の出力値を平滑化する。発振器(114)は、フィルタ(113)の出力値に応じて、出力信号の周波数を制御する。

(もっと読む)

ディジタル制御発振装置および高周波信号処理装置

【課題】DNLの低減を実現可能なディジタル制御発振装置を提供する。

【解決手段】例えば、発振出力ノードOscP,OscM間に並列に結合されるアンプ回路ブロックAMPBK、コイル素子LP,LM、複数の単位容量ユニットCIU等を備え、各CIUは、容量素子CIp,CImと、当該CIp,CImを発振周波数の設定パラメータとして寄与させるか否かを選択するスイッチSWIを備える。ここで、SWIは、デコーダ回路DECからのオン・オフ制御線BIT_CIによって駆動され、当該BIT_CIは、シールド部GSによってOscP,OscMとの間でシールドされる。

(もっと読む)

CDR回路及びCDR方法

【課題】ロック状態であるか否かを検出し、その検出結果を出力するCDR回路及びCDR方法を提供する。

【解決手段】受信データ信号をサンプリングするデータサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドデータ信号を生成するデータサンプリング回路、データサンプリングクロック信号に対して位相がずれたエッジサンプリングクロック信号に同期して、受信データ信号をサンプリングしてサンプルドエッジ信号を生成するエッジサンプリング回路、データサンプリングクロック信号に同期して、受信データ信号の振幅と基準電圧との比較結果信号を出力する振幅比較回路を備え、比較結果信号、サンプルドデータ信号およびサンプルドエッジ信号に基づいて、データサンプリングクロック信号の位相を調整する位相シフタ回路、及び受信データ信号とデータサンプリングクロック信号との位相関係を検出するロック検出回路を備える。

(もっと読む)

位相ロック・ループにおけるVCOの動的バイアス印加

【課題】無線通信機器における局部発振器を提供する。

【解決手段】局部発振器が位相ロック・ループを含む。位相ロック・ループは電圧制御発振器23と新規のVCO制御回路27を含む。VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、VCO制御回路は、PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次にPLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程はPLLがロックされたままで行われる。

(もっと読む)

位相ロックループ回路

【課題】電圧制御発振回路の入力部でのリークに起因する定常位相誤差を防止できる位相ロックループ回路を提供する。

【解決手段】リファレンスクロック信号とフィードバッククロック信号の位相差を検出する位相比較回路と、検出された位相差に応じた電流を第1の容量に出力するチャージポンプ回路と、第1の容量に蓄積されている電荷に基づく制御電圧に応じた発振周波数の出力クロック信号を生成する電圧制御発振回路とを有する位相ロックループ回路にて、チャージポンプ回路による第1の容量への電流の出力完了後の第1の時刻に第1の電圧を保持し、保持された第1の電圧に基づき電圧制御発振回路の入力部に流れるリーク電流に応じた電流を生成し、生成された電流に応じた補正電流をカレントミラー回路を介して第1の容量に出力するようにして、リーク電流による制御電圧の変動を抑制する。

(もっと読む)

適応型受信システム、適応型送受信システム及び複数チャネル送受信システム

【課題】ロックポイント付近におけるサンプリングクロックの位相の調整と、イコライザ部の制御とを安定させ、ジッタトレランスを高める。

【解決手段】位相比較部は、サンプリングタイミングとサンプリングタイミングよりも第一の所定位相分前のタイミングとの間の第一区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LAG(n)を出力するとともに、サンプリングタイミングとサンプリングタイミングよりも第二の所定位相分後のタイミングとの間の第二区間に、等化信号EQDATAのエッジが存在するか否かを示す位相比較信号LEAD(n)を出力する。判定部は、検出データパターンの各ビットに対応する位相比較信号LAG(n),LEAD(n)の出力パターンを所定の比較対象パターンと比較し、合致するか否かに基づいて、等化信号EQDATAの1ビットがサンプリングクロックCKの1周期よりも長いか短いかを判定する。

(もっと読む)

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

PLL回路

【課題】 電源起動からロックまでの時間を短くすると共に、電源断時に電荷を速く放電できるPLL回路を提供する。

【解決手段】 位相の進み/遅れを検出器11で検出し、位相の進み/遅れに相当する信号を積分器12で積分し、起動パルス生成部13が、電源起動を検出し、ロックまでの時間に基づいたパルス幅のパルスをLPF5と積分器12に出力し、LPF5と積分器12が、起動パルス生成部13からのパルスによって内部のコンデンサを充電すると共に電源断で内部のコンデンサに蓄積された電荷を放電するPLL回路である。

(もっと読む)

無線通信装置

【課題】対象装置からの信号に基づいて当該対象装置と同期をとる構成において、非同期状態から同期状態へ早期に復帰することが可能な無線通信装置を提供する。

【解決手段】無線通信装置201は、対象装置から受信した受信データに基づいて生成された再生タイミング信号に基づいて第1の制御電圧を生成し、電圧制御発振器25に第1の制御電圧を供給することにより、再生タイミング信号の周波数成分のうち、所定の周波数以上の成分が減衰された周波数成分を有し、かつ再生タイミング信号に同期する基準タイミング信号を生成するためのジッタ抑圧部12と、タイミング信号生成部22によって生成される再生タイミング信号の異常を検知し、異常を検知した場合には、第1の制御電圧の代わりに、第1の所定範囲内の電圧である第2の制御電圧を電圧制御発振器25に供給するための発振器制御部13とを備える。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機の個体差や伝送チャネルの時間変動に応じて最適なループゲインを探索できるようにするとともに、伝送フレーム内で複数の変調方式が用いられる場合でも最適なループゲインを探索することができるようにする。

【解決手段】ループゲイン制御部34から初期化フラグを受け取ったPLL制御誤差比較部33は、制御誤差値を算出し、比較器63において、この制御誤差値の大小比較を開始する。制御誤差比較結果に基づいてループフィルタ43−1およびループフィルタ43−2に供給するループゲインを制御する。伝送モード別ゲイン選択部71は、複数の内部のレジスタのうち、伝送モード番号TMに対応するループゲインレジスタG1main[TM]に保持させる値をゲイン制御シーケンサ72から入力される値によって更新する。

(もっと読む)

通信装置及び周波数シンセサイザ

【課題】使用する周波数帯域で、温度変化による送受信の振幅値の偏差を抑えることができる通信装置を提供すること。

【解決手段】送信信号の信号路に介在して設けられると共に制御電圧の印加により容量が変化する可変容量素子とインダクタンスとを含む共振回路を有し、この共振回路の共振点に応じて高周波の入力信号の振幅を調整する振幅調整回路と、前記信号路が置かれている雰囲気の温度を検出する温度検出部と、一のチャンネルにおける周波数帯域において、送信信号の振幅値が予め設定した値になるようにまたは近づくように、前記振幅調整回路の制御電圧値と温度検出値との関係データを記憶する記憶部と、前記温度検出部の温度検出値と前記関係データとに基づいて振幅調整回路の制御電圧を出力する制御電圧出力部と、を備えるように装置を構成する。

(もっと読む)

原子発振器

【課題】従来よりも周波数精度を向上させることができる原子発振器を提供する。

【解決手段】磁場発生部40は、アルカリ金属原子20の第1基底準位と第2基底準位にゼーマン分裂を生じさせる磁場を発生させる。周波数制御部50は、光検出部30の検出信号32に基づいて、光源10が出射する第1の光と第2の光が、順に、複数の所定の磁気量子数の各々に対応する第1基底準位と第2基底準位の間で遷移を引き起こす共鳴光対となるように、所定の切り替えタイミングで第1の光及び第2の光の少なくとも一方の周波数を切り替える。磁場制御部60は、検出信号32に基づいて、第1の光と第2の光が、所定の磁気量子数の各々に対応する共鳴光対となるときの第1基底準位と第2基底準位のエネルギー差を特定可能なプロファイル情報を順に取得し、アルカリ金属原子20にかかる磁場の強度が一定になるように磁場発生部40が発生させる磁場の強度を制御する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの確実な同期と再生クロックの適切なジッタ低減とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aは、外部から入力される駆動力制御信号に応じて駆動力が調整される駆動力調整機能付きバッファ増幅器である。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも安定的な動作が可能でかつ出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、ゲーティング回路10の出力パルスのタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3と、ゲーティング回路10の出力端子とVCO11の入力端子との間に設けられたバッファ増幅器16と、VCO11の出力端子とVCO13の入力端子との間に設けられたバッファ増幅器17とを備える。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

位相同期発振装置

【課題】 小さいばらつきで電圧制御回路から供給される温度補償された電圧によって制御される電圧制御発振器を介して接続された増幅器の出力電力を、精度良く増減させ出力端子から出力する位相同期発振装置を得る。

【解決手段】 発振周波数を制御する周波数制御電圧入力端子と発振電力を制御する電圧入力端子とを有する電圧制御発振器と、この電圧制御発振器から出力される高周波信号を増幅して出力する温度特性を有する増幅器と、温度センサを有し、この温度センサの出力信号で基準電圧から変化する電圧を前記電圧制御発振器の電圧入力端子に入力し、前記電圧制御発振器を介して前記増幅器の電力非飽和領域の電力を増減する電圧制御回路とを備えている。

(もっと読む)

量子干渉装置、原子発振器及び磁気センサー

【課題】アルカリ金属原子に対するEIT現象の発現効率を高めることにより、レーザーパワーの利用効率を向上させることができる量子干渉装置、原子発振器及び磁気センサーを提供すること。

【解決手段】光源10は周波数がΔωずつ異なる複数の第1,第2の共鳴光を発生させ、光検出手段40は磁場発生手段30により磁場が与えられたアルカリ金属原子を透過した第1,第2の共鳴光を含む光の強度を検出する。制御手段50は、光検出手段の検出結果に基づき、所定の1対の第1,第2の共鳴光の周波数差がアルカリ金属原子の2つの基底準位のエネルギー差に相当する周波数差に等しくなるように、かつ、アルカリ金属原子の2つの基底準位の各々に発生した、磁気量子数が互いに1だけ異なる2つのゼーマン分裂準位のエネルギー差に相当する周波数δに対して、2×δ×n=Δω及びΔω×n=2×δ(nは正の整数)の少なくとも一方を満足するように制御する。

(もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

発振周波数制御回路

【課題】 自己の周波数を補正し、自走した時にも発振周波数を安定に保ち、更に外部からの固定電圧を可変にした制御電圧で発振できる発振周波数制御回路を提供する。

【解決手段】 電圧制御発振器15と、分周器16と、位相比較器12と、ループフィルタ14と、検波回路17と、PWM回路22と、メモリ21と、制御電圧可変回路26と、位相比較器12とループフィルタ14との接続をオン/オフすると共に制御電圧可変回路26からの制御電圧を選択出力する選択スイッチ13と、当該制御電圧選択の指示で当該制御電圧を優先的に選択出力し、当該指示がない場合に検波回路17で検出された外部基準信号のレベルが適正範囲内であれば選択スイッチ13をオンとし、レベルが適正範囲外であれば選択スイッチ13をオフとしてメモリ21に記憶されたパルス生成の情報をPWM回路22に出力するCPU20とを有する。

(もっと読む)

位相同期回路

【課題】ノイズが混入した場合であっても、所望の周波数で発振信号を生成することが可能な位相同期回路を提供する。

【解決手段】位相同期回路は、低域通過フィルタからの出力電圧に応じて発振回路から出力される発振信号を、制御信号に基づいた利得で増幅する可変利得増幅回路と、可変利得増幅回路からの増幅信号の位相に応じた第1の位相と、増幅信号の基準となる基準信号の第2の位相とを比較して、第1の位相と第2の位相とを一致させるための比較信号を低域通過フィルタに出力する位相比較回路と、出力電圧に基づいて、第1の位相と第2の位相とが一致しているか否かを検出する検出回路と、検出回路の検出結果に基づいて、第1の位相と第2の位相とが一致している場合、利得が所定の値となるような制御信号を生成し、第1の位相と第2の位相とが一致していない場合、利得を所定の値より増加させるような制御信号を生成する制御信号生成回路と、を備える。

(もっと読む)

1 - 20 / 105

[ Back to top ]