Fターム[5J106DD03]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 波形・レベル変換回路 (375) | 微分回路 (23)

Fターム[5J106DD03]に分類される特許

1 - 20 / 23

信号生成回路、レーダー装置

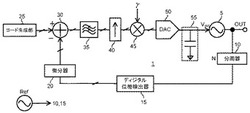

【課題】低雑音で高周波数精度かつ高線形なFMCW信号を得ることのできる信号生成回路、レーダー装置を提供する。

【解決手段】アナログ制御信号により発振信号の周波数が制御される発振器を有している信号生成回路は、発振信号の位相情報を検出してディジタルの位相情報を出力するディジタル位相検出部と、ディジタルの位相情報を微分してディジタルの周波数情報を出力する第1の微分部と、発振周波数を設定する周波数設定コードとディジタルの周波数情報とを比較してディジタルの周波数誤差情報を出力する比較部と、ディジタルの周波数誤差情報の高周波成分を除去するローパスフィルタ部とを備えている。さらに、高周波成分が除去されたディジタルの周波数誤差情報をアナログの周波数誤差情報に変換するD/A変換部と、アナログの周波数誤差情報を積分してアナログの位相誤差情報に変換しアナログ制御信号として出力する積分器とを備えている。

(もっと読む)

デジタルPLL回路及びクロック生成方法

【課題】位相差検出値の範囲の制限により引き込み動作が影響されることのないデジタルPLL回路を提供する。

【解決手段】デジタルPLL回路は、マスタクロックとスレーブクロックとの位相差を検出し、長さが2πの範囲内の値をとる位相差検出値を出力するデジタル位相比較器10と、位相差検出値と閾値とを比較した結果に応じて、位相差検出値を範囲に限定されない位相値に補正する補正部11と、補正部の出力する位相値に応じてスレーブクロックを生成するスレーブクロック生成部15とを含む。

(もっと読む)

デジタルクロックリカバリ回路及び半導体チップ

【課題】小型で、省電力で、かつパルスベースの超高速シリアル転送にも用いることのできるデジタルクロックリカバリ回路(CDR)を実現することを目的とする。

【解決手段】デジタルロックループ(DLL)、エッジ検出器、デジタルコンパレータ等を用いて、データ信号にDLLクロック信号をロックさせ、全ての回路要素をデジタル回路で構成し、クロックデータリカバリ(CDR)を実現する。

(もっと読む)

CDR回路

【課題】入力データと再生クロックの同期を保ったまま、再生クロックの適切なジッタ量と適切なバースト応答時間とを両立させる。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスのタイミングに合うように出力クロックの位相を調整するG−VCO3と、G−VCO3から出力されるクロックのタイミングに合うように出力クロックの位相を調整するVCO4と、入力データのデータ識別をVCO4から出力される再生クロックに基づいて行うフリップフロップ1と、G−VCO3の出力端子とVCO4の入力端子との間に設けられたバッファ増幅器6aとを備える。バッファ増幅器6aの駆動力は、CDR回路のバースト応答時間が仕様の範囲内で最大となるように予め設定される。

(もっと読む)

CDR回路

【課題】周波数安定度が高くジッタの少ない再生クロックを生成する。

【解決手段】CDR回路は、入力データ4が遷移したときにパルスを出力するゲーティング回路10と、位相同期ループ中に配置されたVCO12と、ゲーティング回路10の出力パルスのタイミングに合うように再生クロック7の位相を調整することにより、入力データ4とタイミングの合った再生クロック7を出力するG−VCO13と、入力データ4のデータ識別を再生クロック7に基づいて行うフリップフロップ3とを備える。入力データ4のデータレートと等しい周波数の参照クロック5またはVCO12の出力クロックは、注入信号9としてG−VCO13に入力される。

(もっと読む)

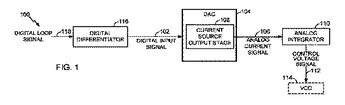

アナログ積分のためのデジタル補償を有するフェイズロックループ

フェイズロックループ(PLL)デバイスは、アナログ積分器によるアナログ電流信号の積分を少なくとも部分的に補償するために、デジタルループ信号を微分するように構成されたデジタル微分器を含む。デジタルアナログコンバータ(DAC)は、デジタル入力信号に基づいてアナログ電流信号を発生する電流源出力ステージを含む。アナログ積分器は、アナログ電流信号を積分して、電圧制御発振器(VCO)を制御するための電圧制御信号を発生する。  (もっと読む)

(もっと読む)

利得を自動的に設定する位相ロックループ

【課題】利得を自動的に設定する位相ロックループPLLを提供する。

【解決手段】PLL99は、第1の周波数SRと第2の周波数SNの差を表す第1の信号Aを供給する周波数弁別器130を備える。またPLL99は、周波数弁別器130に結合され、第1の信号Aを受信し、第1の信号Aからの情報に基づいて第2の信号Bを供給する比較器135を備えている。第2の信号Bは設定する位相ロックループに対する利得設定を表す。

(もっと読む)

信号生成回路

【課題】 プロセス要因で生じるクロック信号の位相バラツキを抑える。

【解決手段】 信号生成回路100は、クロック信号PLLCKが通るクロック信号線30に1以上のクロックバッファ31が配置され、1以上のクロックバッファ31によりクロック信号PLLCKを遅延させ、遅延したクロック信号に基づき所定の信号を生成する。この信号生成回路100は、前記クロックバッファ31と同一チップ上に形成された複数のクロックバッファ41を有して構成される参照用クロックバッファ40と、参照用クロックバッファ40の遅延量を検知し、この遅延量と予め定められた遅延量との差に基づく位相調整信号PHADJを出力する遅延検知回路50と、位相調整信号PHADJに応じて、クロック信号PLLCKの位相を変える位相調整回路20と、を備える。

(もっと読む)

デジタル位相検出器及びデジタル位相同期回路

【課題】デジタル位相検出器の時間分解能をデジタル制御し、回路規模・消費電力を低減する。

【解決手段】信号S1が入力される直列に接続された第1の遅延素子1011〜101Nと、信号S2が入力される直列に接続された第2の遅延素子1021〜102Nと、各々の第1の遅延素子の出力が与えられ、各々の第2の遅延素子の出力をクロックとするラッチ回路1031〜103Nと、前記ラッチ回路の出力値に基づいて信号S1のパルス幅を示すデジタルコードPWmを算出して出力するデコーダ回路104と、デジタルコードPWmと所定のデジタルコードPWrとを比較し、比較結果を出力する比較器105と、前記比較結果に基づいて前記第1及び第2の遅延素子の少なくともいずれか一方の遅延時間を制御する遅延制御回路106と、を備える。

(もっと読む)

デジタル制御発振器及びこれを用いた位相同期回路

【課題】発振周波数を線形に近くかつきめ細やかに制御可能なデジタル制御発振器を提供する。

【解決手段】正相発振信号を出力する正端子213と、逆相発振信号を出力する負端子214と、センタータップ210とを有し、正端子とセンタータップとの間の任意の位置に第1の接点211を備え、負端子とセンタータップとの間の第1の接点に対応する位置に第2の接点212を備える差動インダクタ200と、正端子と負端子との間に接続され、第1のデジタル制御コードによってキャパシタンスを2値に変化させる第1の可変キャパシタを複数含む第1の可変キャパシタバンク220と、第1の接点と第2の接点との間に接続され、第2のデジタル制御コードによってキャパシタンスを2値に変化させる第2の可変キャパシタを複数含む第2の可変キャパシタバンク240と、正端子と負端子との間に接続される負性抵抗230とを具備する

(もっと読む)

ディジタル位相検出器およびPLL

【課題】従来のディジタル位相検出器は、遅延素子としてインバータ等の遅延時間を使用しているが、遅延素子の配置および配線の固定が必要であることからゲート・アレイやFPGA等ではインプリメントすることが難しい。遅延素子の遅延時間はデバイスの種類やプロセスばらつきにより変動するため位相検出の精度に影響が出る。

【解決手段】2つのクロックが整数比に近い周波数を有している場合において、第1のクロックを入力とするM/N逓倍する逓倍器と、逓倍器の出力クロックを用いて第2のクロックをラッチするF/Fと、F/Fの出力を微分する微分回路と、逓倍器の出力クロックを入力とするカウンタと、微分回路の出力に応じて前記カウンタの出力を保持するラッチ回路と、ラッチ回路の出力を加算する第1の加算器と、第1の加算器の出力を固定値から減算する第2の加算器と、第2の加算器の出力を順次積算する積算器と、を備えるよう構成する。

(もっと読む)

CDR回路

【課題】再生クロックのジッタを低減する。

【解決手段】CDR回路は、入力データが遷移したときにパルスを出力するゲーティング回路2と、ゲーティング回路2の出力パルスにより発振位相が制御されるクロックを生成するゲーテッドVCO3と、フィードバック入力端子にゲーテッドVCO3の出力クロックが入力され、ゲーテッドVCO3の出力クロックと同じ周波数の再生クロックを生成するVCO4と、入力データを遅延させる遅延回路5と、遅延回路5を通過した入力データのデータ識別を再生クロックに基づいて行うフリップフロップ1とを備える。

(もっと読む)

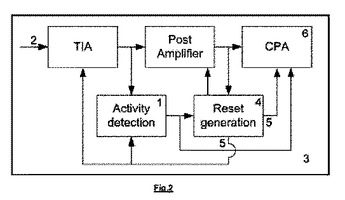

TDMAネットワークにおける信号検出のための装置及び方法

本発明は、バーストモード受信機における動作状態を検出するための回路(1)に関する。本回路は、プリアンブルを含む入力信号(2)を受けるように構成される。本回路は、入力信号(2)における信号遷移を検出する微分器(11)を備え、微分器(11)を動作させる情報をそのプリアンブルが含む。好ましい実施形態において、上記情報は時定数である。本回路は、微分器の出力が供給されるように構成された積分器(12)をさらに備える。結果として得られる信号は基準(16)に対して比較される。この基準と交差するとき、動作状態が検出される。ある実施形態ではフロントエンド回路が提供され、フロントエンド回路は、動作状態を検出する回路の後段に、フロントエンド回路をリセットするように構成されたリセット回路と、位相を復元するように構成されたクロック位相アラインメント回路を備える。  (もっと読む)

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

位相比較信号処理回路

【課題】位相比較回路の出力矩形波信号の処理する際に、簡単な回路構成を有し、PLLで引込み可能な周波数幅を拡げ、同期時間を短縮できる位相比較信号処理回路を提供する。

【解決手段】入力矩形波信号を双極性信号に変換する電圧シフタ2、入力矩形波信号のレベル変化時に制御パルス信号を発生する制御パルス信号発生器7、制御パルス信号の到来時に積分値をリセットし、その後双極性信号を積分して積分値を出力する積分回路3、積分値のリセット時のレベル変化分を微分パルスとして出力する微分回路4、制御パルス信号の到来時に微分パルスを出力するゲート回路6、前記保持回路は最新の入力微分パルスレベルを保持し、微分パルスレベルの更新時にその微分パルスレベルが保持されるように保持電圧値が順次変化する保持信号を形成するホールド回路8を備え、この保持信号を次段のループフィルタに供給する。

(もっと読む)

位相比較信号処理回路

【課題】PLLのデジタル位相比較器の出力矩形波信号を処理し、PLLの引き込み可能な周波数幅を拡げ、同期時間を短縮する位相比較信号処理回路を提供する。

【解決手段】矩形波信号を両極性信号に変換する電圧シフタ7と出力端子22間に並列接続され、整流回路8と積分保持回路9と微分回路10とゲート回路12と電圧ホールド回路13と共通の加算回路14とからなる第1信号路、及び、整流回路15と積分保持回路16と微分回路17とゲート回路19と電圧ホールド回路20と前記加算回路14とからなる第2信号路、第1信号路及び第2信号路の積分保持回路9、16とゲート回路12、19を個別制御する制御信号発生器21を備え、第1及び第2信号路で、両極性信号の整流、整流電圧の積分保持、積分保持値の微分、微分出力の保持、保持電圧の加算を行うことにより処理信号を出力する。

(もっと読む)

通信用半導体集積回路

【課題】送受信動作に使用する周波数シンサセイザとしてフラクショナルN PLL回路を含むRF通信用半導体集積回路において、PLL回路のチャージポンプ回路CPCのソース電流注入トランジスタとスィンク電流放出トランジスタとのミスマッチに起因する非線型性の影響を軽減する一方、PLL回路の位相ノイズを低減するための補償回路の回路規模を小さくして補償回路の制御も単純化すること。

【解決手段】受信動作と送信動作とに使用する周波数シンサセイザFrct_SynthとしてフラクショナルN PLL回路のクローズドループ帯域を、数十KHzのオーダーの狭帯域とする。チャージポンプ回路CPCの2つのトランジスタのミスマッチに起因する非線型性の影響の軽減を最も段純な方法であるオフセット回路MN2、MN3によるループフィルタLFCへのdc直流電流Ioffsetの注入もしくはLFCからのIoffsetの放出によって実現する。

(もっと読む)

通信用半導体集積回路

【課題】基準周波数発振器DCXOの発振出力信号をレベル変換器Lev_Convによりレベル変換する際に発生するDCXOの発振出力信号の高調波成分によるRF送信用電圧制御発振器TXVCOの発振出力信号の近傍への漏れ込みによる影響を低減すること。

【解決手段】レベル変換器Lev_ConvはDCXOの発振出力信号をレベル変換して、レベル変換信号をRF送信用電圧制御発振器TXVCOの発振周波数を制御するPLL・フラクショナルシンセサイザFrct_Synthの位相比較器PDCに供給する。このLev_Convは、基準周波数発振器DCXOの基準周波数信号を増幅する自己バイアス型電圧増幅器Self_Bias_Volt_Ampを含む。自己バイアス型電圧増幅器は、結合容量C1、増幅トランジスタQn5、負荷Qp5、バイアス素子R1を含み、外部電源電圧Vdd_extが変動しても、高調波成分のレベル変動を抑制する。

(もっと読む)

ディジタル位相同期装置

【課題】入力された正弦波と周波数が等しく、かつ位相が同期した正弦波を、簡易で正確に、出力する装置を提供する。

【解決手段】位相差検出回路1は、外部から入力された第一の正弦波と正弦波生成回路5より出力する第二の正弦波との位相差を、ディジタル信号処理により算出する。その算出値に基づいて第二の正弦波の位相と周波数を調整するので、正弦波生成回路5は入力された第一の正弦波に周波数が等しく、かつ位相が同期した第二の正弦波を簡易に正確に出力することができる。

(もっと読む)

同期装置、同期方法及び同期プログラム並びにデータ再生装置

【課題】本発明は、周波数誤差の引込範囲を広げて位相同期の能力を向上できるようにする。

【解決手段】本発明は、周波数誤差検出回路33において位相検出器54により補間信号pkにおける位相誤差Δτ(k)を検出し、差分算出器55により当該位相誤差Δτ(k)と1クロック前の位相誤差Δτ(k−1)との差分を基に周波数誤差Δf(k)及びその移動平均である平均周波数誤差Δfa(k)を算出し、位相同期部8において周波数収束ループ又は周波数初期値ループを形成して周波数誤差Δf(k)に基づく周波数補正値DF又は平均周波数誤差Δfa(k)に基づく平均周波数補正値DFAをLPF25の積分項に加算することにより、当該位相同期部8における周波数誤差Δf(k)を高速に且つ安定してほぼ0に収束させることができる。

(もっと読む)

1 - 20 / 23

[ Back to top ]