Fターム[5J106DD12]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成−副構成 (4,863) | 合成・分配回路 (405) | 乗算回路 (90)

Fターム[5J106DD12]に分類される特許

1 - 20 / 90

発振器

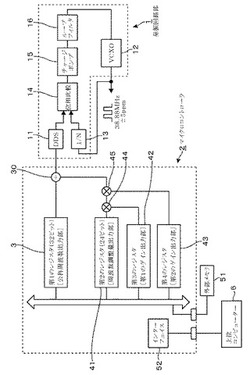

【課題】周波数の可変幅を容易に変更することができ、また周波数を高精度に調整することができる発振器を提供すること。

【解決手段】第1のレジスタ3により公称周波数に対応するディジタル値を出力する。第2のレジスタ41により、公称周波数に対して周波数比率で表した周波数の調整量を出力する。一方前記周波数調整量であるディジタル値の可変範囲(フルレンジ)と周波数比率で表わした周波数の可変幅とを対応させるようにゲインを決め、このゲインを第2のレジスタ41からのディジタル値に乗算し、この乗算値と公称周波数に対応するディジタル値とを加算して周波数設定信号とする。

(もっと読む)

PLL回路

【課題】本発明は、遅延素子の遅延時間のばらつきを補償するように、デジタルコードを補正する必要のないTDCを提供することを目的とする。

【解決手段】基準信号の周波数に対して所望倍数の周波数を有する出力信号を出力する発振部と、基準信号についての出力信号の整数分周及び小数分周の和並びに当該所望倍数について差分を計算し、発振部に当該差分を0にするように出力信号を出力させる位相比較部と、を備えるPLL回路において、TDC2は、小数分周の初期値を設定し、初期値を計測値として出力するデジタルコード発生器23と、初期値に基づく位相比較部及び発振部の動作後に、当該差分を0にする方向に、小数分周の分解能を1ステップとして段階的に、小数分周を初期値から最適値へと更新し、最適値を計測値として出力するデジタルコード発生器23及び加減算器24と、を備える。

(もっと読む)

PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

(もっと読む)

PLL回路

【課題】本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【解決手段】本発明は、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力するDCO1と、位相差を示すデジタル信号を出力する位相検出器10と、位相差を示すアナログ信号を出力し、デジタル信号の少なくとも最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有するEXOR型位相比較器21と、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える切替制御部Sと、を備えることを特徴とするPLL回路Pである。

(もっと読む)

注入同期発振装置

【課題】位相雑音を改善する注入同期発振装置を得る。

【解決手段】基準発振器1の出力波を所定の電力に調整する電力調整手段2と、電力調整された電波を分配する同相分配手段3と、分配された電波が各々入力され、入力される周波数の自然数倍の周波数で発振する複数の注入同期発振器4と、複数の注入同期発振器4の各々の出力を合成して出力する同相合成手段5とを備えた。

低離調周波数では、注入同期発振器4の出力波が、低離調周波数で位相雑音特性が良い基準発振器1の出力波に同期するので、位相雑音が改善される。一方、高離調周波数では、各々の注入同期発振器4の出力波の位相雑音が無相関のため、同相合成手段5により各々の注入同期発振器4の出力波を合成することで、位相雑音が改善される。

したがって、低離調周波数および高離調周波数の全離調周波数において位相雑音を改善することができる。

(もっと読む)

クロック生成装置および電子機器

【課題】レプリカ回路が不要で、小面積化を図ることが可能であり、しかもジッタの増加を防止でき、低ジッタ出力クロックを生成することが可能なクロック生成装置および電子機器を提供する。

【解決手段】アキュムレータの値に応じて目標とするNCOクロックと実際のNCOクロックとの位相差を取得する位相差取得部と、入力クロックに位相同期した信号に応じて入力クロックに複数の遅延を与えた複数の遅延クロックを生成する遅延同期回路と、位相差取得部の位相差情報を受けて複数の遅延クロックから目標とする上記NCOクロックの位相に近づくような遅延が与えられた遅延クロックを選択し、選択クロックとして出力する選択部と、選択部で選択された上記選択クロックに上記NCOクロックを同期させて出力クロックを得る第2の同期回路とを有する。

(もっと読む)

PLL回路

【課題】Trackingバンクの最小1bit以下の周波数分解能を実現でき、かつC/N特性の劣化を防止できるPLL回路を提供することを目的とする。

【解決手段】PLL回路101は、デジタル信号の値で周波数を離散的に調整し、微小周波数を1のアナログ信号の電圧値で調整し、所望の周波数の出力信号を出力する発振器10と、基準信号と発振器10の出力信号との位相差及び周波数差を表すデジタル値を出力する比較器11と、比較器11の出力するデジタル値を複数のデジタル信号として出力するループフィルタ44と、ループフィルタ44が出力する前記デジタル信号のうち発振器10で微小周波数の調整に対応する1のデジタル信号が直接入力され、入力されたデジタル信号をアナログ信号に変換するデジタルアナログ変換器13と、デジタルアナログ変換器13からのアナログ信号の高周波成分を除去するローパスフィルタ14と、を備える。

(もっと読む)

PLL

【課題】ジッタが抑制されたPLLを提供する。

【解決手段】PLLは,基準クロックとフィードバッククロックとの位相差信号を遅延し,異なる時間遅延させた位相差信号に応じてチャージ電流を生成する複数のチャージポンプCPを有す。また当該複数のチャージポンプが生成するチャージ電流を加算して出力するチャージポンプ等化器と,ループフィルタと電圧制御発振器の理想特性を持ち,位相差信号の位相差を有する位相差デジタル値を入力して理想特性に基づいてレプリカ出力を生成するレプリカ回路10と,レプリカ出力と理想出力との誤差信号と前記位相差信号との相関値を平滑化してチャージポンプ係数を生成し,複数のチャージポンプそれぞれに負帰還する係数生成回路20−1とを有し、複数のチャージポンプはチャージポンプ係数に応じた電流値を持つチャージ電流をそれぞれ生成する。

(もっと読む)

周波数追尾装置

【課題】異なるコヒーレント加算時間で算出した積算パワーの平方根の差分によって周波数ずれ量を算出することで、高精度な周波数ずれ量を算出する。

【解決手段】 所望の衛星信号yを加算時間MAでコヒーレント加算し、NA回ノンコヒーレント加算をして、積算パワー|yA|2を算出する積算器17と、衛星信号yを加算時間MAと異なる加算時間MBでコヒーレント加算し、NB回ノンコヒーレント加算をして、積算パワー|yB|2を算出する積算器18と、積算器17によって算出される積算パワーの平方根|yA|と、積算器18によって算出される積算パワーの平方根|yB|との差分から、周波数ずれ量Δf2を算出する周波数ずれ演算器20と、を備え、周波数ずれ演算器20で算出された周波数ずれ量Δf2に基づいて、所望の衛星信号yを追尾する。

(もっと読む)

PLL回路、PLL回路の誤差補償方法及び通信装置

【課題】デジタル制御発振器を持つPLL回路に用いられるTDC回路の有限な分解能により発生する周期性誤差を補償することが可能なPLL回路を提供する。

【解決手段】発振回路の累積クロック数をデジタル値として検出する累積クロック数検出部と、前記発振回路の累積クロック数の小数部のデジタル値の、第1の基準クロックを基準とする周期性を検出する周期検出部と、前記発振回路の出力クロックの1周期のデジタル値、前記発振回路の累積クロック数の小数部が持つ周期性の1周期のデジタル値、および前記発振回路の累積クロック数の小数部が持つ周期性の各周期の開始点から前記第1の基準クロック数をカウントした値から補正値を算出する補正値算出部と、前記周期性の各周期の開始点から前記第1の基準クロックの周期で、前記累積クロック数の小数部に前記補正値を加算する加算部と、を備える、PLL回路が提供される。

(もっと読む)

デジタルPLL回路、情報再生装置、ディスク再生装置および信号処理方法

【課題】複数の倍速に対応できることを前提に、再生性能を落とすことなくトータルの回路規模および消費電力が小さく、しかもループ遅延が小さい安定なPLLを提供する。

【解決手段】A/D変換器は入力チャネルレートに依存せず高速なサンプリングを行い、ダウンコンバータにより必要なチャネルレートに落とす。これにより倍速数に依存せずにAAFの特性を単一化できるためアナログ回路を小型化できる。また、デジタル位相追従部は補間型完全デジタル位相追従構成とすることでループ遅延を最小化できる。一方、CAV再生時には入力レートに応じてタウンコンバータのデシメーション比Mを変更することでデジタル回路の動作クロックが必要以上に上がることを押さえ消費電力増加を防ぐ。デシメーション比Mの切り替え時はデジタル回路内部遅延を考慮してデジタル位相追従部の内部周波数切り替えタイミングを遅らせることで位相周りのないシームレスな切り替えを実現する。

(もっと読む)

半導体集積回路および無線通信装置

【課題】小規模かつ低消費電力で発振信号を生成可能な半導体集積回路およびこれを用いた無線通信装置を提供する。

【解決手段】半導体集積回路は、デジタル制御発振器と、カウンタと、時間デジタル変換器と、加算器と、制御信号生成部と、を備える。時間デジタル変換器は、発振信号と参照信号との位相差に対応する第3のデジタル信号を生成する。前記時間デジタル変換器は、分周器と、複数のインピーダンス素子と、位相差検出部と、を有する。分周器は、前記発振信号を分周して複数の分周信号を生成する。複数のインピーダンス素子は、前記複数の分周信号を分圧して、前記発振信号を遅延させた複数の遅延信号を生成する。位相差検出部は、前記参照信号と、前記複数の遅延信号のそれぞれと、を比較することにより、前記参照信号と前記発振信号との位相差に対応する前記第3のデジタル信号を出力する。

(もっと読む)

原子発振器

【課題】光検出器で吸収される光のレベルを高めてS/Nを改善した原子発振器を提供す

る。

【解決手段】この原子発振器50は大きく分けると、アルカリ金属原子と該アルカリ金属

原子の同位体とを混合した気体を封入したセル2と、可干渉性(コヒーレント性)を有し

、1つの中心周波数に対して2つの異なる周波数成分を有する第1の共鳴光対と第2の共

鳴光対を含む複数の光を気体に照射する光源(LD)1と、気体を透過した光の強度に応

じた検出信号を生成する光検出部(PD)3と、検出信号の強度に基づいて、アルカリ金

属原子に電磁誘起透過現象(以下、EIT現象と呼ぶ)を生起させるように第1の共鳴光

対の周波数を制御すると共に、アルカリ金属原子の同位体にEIT現象を生起させるよう

に、第2の共鳴光対の周波数を制御する周波数制御部12と、を備えて構成されている。

(もっと読む)

TDC回路

【課題】検出可能範囲の拡大と分解能の向上とを両立可能なTDC回路を提供する。

【解決手段】2n個の遅延量の異なる反転遅延素子を直列接続して形成されたループをそれぞれ含む第1の遅延回路および第2の遅延回路に、第1パルス信号駆動回路および第2のパルス信号駆動回路により、第1の遅延回路および第2の遅延回路にそれぞれ検出対象エッジとリセットエッジを有するパルス信号伝搬させる構成を持つバーニアディレイに、第1の遅延回路の反転遅延素子のいずれかと第2の遅延回路の反転遅延素子のいずれかに対して、伝搬されるリセットエッジの入力に対応する論理反転を選択的に遮断する操作をそれぞれ行う遮断回路と、第1の遅延回路および第2の遅延回路に含まれる遮断対象の反転遅延素子に対して、伝搬された検出対象エッジの入力に応じて反転した論理をリセットする操作をそれぞれ行うリセット回路とを備える。

(もっと読む)

クロックアンドデータリカバリ回路

【課題】ジッタトレランスの低下、引き込み時間の増大、引き込みが不能等の問題を解消するクロックアンドデータリカバリ回路を提供する。

【解決手段】多相の抽出クロック信号で入力データをサンプリングするデータサンプリング回路11からのサンプリングデータ信号群の比較結果に基づきクロック信号の位相を進める信号(UP1)又は位相を遅らせる信号(DOWN1)、エラー検出時エラー信号(ERR)を出力する位相検出器12と、UP1/DOWN1信号を積分する第1の積分器13と、第2の積分器14と、第1の積分器の出力値(PPM)に基づき所定のパターンを生成するパターン発生器15と、第2の積分器の出力とパターン発生器の出力を合成する混合器16と、入力クロックを入力し前記混合器の出力信号に基づき位相を可変させた前記多相の抽出クロックを生成する位相補間器17から構成される。

(もっと読む)

基準信号発振器

【課題】優れた長期安定度を有する高安定発振器を用いた基準信号発振器において、高安定発振器に短時間の障害が発生したときにおいても、継続して安定して基準信号を出力すること。

【解決手段】高安定発振器としてルビジウム発振器やセシウム発振器を用い、これら発振器に比べて長期間の周波数安定度が劣るが、短期間の周波数安定度が高い準安定発振器であるOCXOをバックアップとして用いる。高安定発振器に異常が発生してからの経過時間と、両発振器の使用の重み付け(利用比率)とを対応させたテーブルを用意し、このテーブルを用いることで、高安定発振器が復帰した後、初めは準安定発振器の発振周波数を100%利用するが、その後段階的に準安定発振器の使用の重み付け(利用比率)を小さくし、高安定発振器の利用比率を大きくする。

(もっと読む)

局部発振器

【課題】デジタル制御発振器の出力と参照信号とが非同期であっても、安定したPLL動作を確立できる局部発振器を提供することを目的とする。

【解決手段】デジタル制御発振器の発振信号と前記参照信号との位相差を発振器分数位相として出力し、また、前記発振信号の位相が、前記参照信号の位相に対して、前記発振信号の半周期よりも位相が遅れている場合に「−1」、遅れていない場合に「+1」の補整情報を出力する時間デジタル変換器と、|前記補整情報−予測位相情報|>|前記補整情報+前記第1位相情報−前記予測位相情報|の場合に、前記第1位相情報に前記補整情報を加算したものを第2位相情報として出力し、|補整情報−発振器予測位相|>|補整情報+第1位相情報−発振器予測位相|でない場合に、前記第1位相情報を第2位相情報として出力する補正部と、を備えている。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

受信装置及びゲイン設定方法

【課題】受信特性を向上させることのできる受信装置を提供する。

【解決手段】受信装置は、受信データD1に基づいて抽出クロックCLKを生成するクロックデータリカバリ回路2と、受信データD1のジッタ量に応じて、上記クロックデータリカバリ回路2内のフィルタ回路11のゲインパラメータG1を設定するゲイン設定部3とを有する。

(もっと読む)

1 - 20 / 90

[ Back to top ]