Fターム[5J106GG05]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 制御対象 (2,074) | 周波数比較(弁別)回路 (29)

Fターム[5J106GG05]に分類される特許

1 - 20 / 29

PLL回路

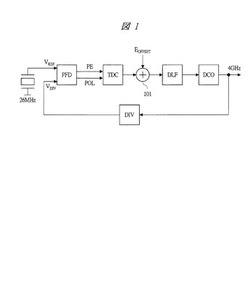

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

位相平均化に基づくクロック及びデータ回復の方法、回路及びシステム

【課題】入力データビットストリームとともに伝達される周波数ジッタ及びクロック信号発生器によって生成される周波ジッタを減衰させることができる、位相平均化に基づくクロック及びデータ回復の方法等を提供する。

【解決手段】一実施形態で、方法は、第1のクロック信号の第1の周波数を第1の周波数と基準クロック周波数の基準クロック周波数との間の周波数差に基づき調整するステップ(603)と、第1のクロック信号の第1の周波数及び第1の位相を第1のクロック信号と入力データビットストリームとの間の位相差及び第1の周波数と基準クロック周波数との間の周波数差に基づき更に調整して、第1のクロック信号の第1の周波数及び第1の位相を入力データビットストリームの入力データビット周波数及び入力データビット位相に略固定するステップ(606)とを有する。

(もっと読む)

位相同期ループのための線形位相周波数検出器およびチャージポンプ

【課題】位相同期ループ(PLL)における位相周波数検出器およびチャージポンプの線形動作を達成する。

【解決手段】位相周波数検出器は、基準信号とクロック信号とを受け取り、基準信号とクロック信号とに基づいて第1および第2の信号を生成し、第1の信号のみに基づいて第1および第2の信号をリセットする。第1および第2の信号は、それぞれ、upおよびdownの信号であってもよいし、それぞれ、downおよびupの信号であってもよい。位相周波数検出器は、予め定められた量の分、第1の信号を遅らせ、遅れた第1の信号と第2の信号とに基づいて、リセット信号を生成し、リセット信号を用いて第1および第2の信号をリセットすることができる。チャージポンプは、第1および第2の信号を受け取り、基準信号とクロック信号との間の位相誤差を示す出力信号を生成する。

(もっと読む)

位相周波数比較回路及びPLL回路

【課題】入力クロックが停止しても出力クロックの周波数を保持するPLLを用いて、ロジック回路を駆動する方法を提供する。

【解決手段】位相周波数比較回路をPFD主要部と基準クロック停止検出部202Bの二つのモジュールから構成する。基準クロック停止検出部202BはPFD主要部のRS−FFのデータ端子に基準データ信号pfd_in_enを出力する。この基準データ信号pfd_in_enは、基準クロック停止検出部202B内のフリップフロップ202B−1に由来して生成される。このフリップフロップ202B−1は位相比較動作の終了を表すオーバラップ信号overlapをタイミングとし、基準クロックref_clkによってリセットされる。基準クロックref_clkが停止すると、基準データ信号pfd_in_enは「L」のままとなり、結果PFD主要部の動作が停止する。

(もっと読む)

位相比較器およびクロックデータリカバリ回路

【課題】充放電流を切り替えるスイッチを確実に動作させ、高速化に対応できチャージポンプ回路の機能を保持できる位相比較器およびクロックデータリカバリ回路を提供する。

【解決手段】入力データと第1のラッチ111のラッチデータの論理不一致を検出する第1の検出回路と、第1のラッチのラッチデータと第2のラッチ112のラッチデータの論理不一致を検出する第2の検出回路と、第1の検出回路および第2の検出回路の検出結果に応じて、電流を充電または放電を切り替えるための切替スイッチ機能を含むチャージポンプ回路と、を有し、第1の検出回路、第2の検出回路、およびチャージポンプ回路は、第1および第2の検出回路の論理不一致判定部とチャージポンプ回路の充放電流を切り替える切替スイッチとが複合化された検出回路複合型チャージポンプ回路120として形成されている。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

半導体集積回路

【課題】チップ面積の更なる縮小化を図ることができる半導体集積回路を提供する。

【解決手段】ディジタル制御発振器50−1〜50−nと、位相データ出力部100−1〜100−nと、積分処理部150と、フィルタ部151と、フィルタ部151からの時分割された出力信号に所定の係数を乗算した値を発振器制御値OTWとして出力する乗算器(第1の乗算器)40と、リファレンス周波数Frefに同期して、発振器制御値OTWを各ディジタル制御発振器50−1〜50−nに振り分ける出力セレクタ(制御値分離部)42と、を備える。

(もっと読む)

位相周波数比較器およびシリアル伝送装置

【課題】ループ帯域幅を安定させる位相周波数比較器を簡易な回路で提供する。

【解決手段】基準クロック102とフィードバッククロック103とを入力とし、周波数シンセサイザへのアップ信号と周波数シンセサイザへのダウン信号とを出力する位相周波数比較器において、第1位相周波数比較回路106と、第2位相比較回路107と、前記基準クロック102と前記フィードバッククロック103とを入力とし、前記第1位相周波数比較回路106の入力と前記第2位相比較回路107の入力とに、所定の相対的な遅延を与える遅延回路部108とを備え、周波数比較を前記第1位相周波数比較回路106で行い、位相比較を前記第1位相周波数比較回路106とラッチを制御した前記第2位相比較回路107とで行う位相周波数比較器。

(もっと読む)

クロックデータリカバリ回路、表示装置用データ転送装置及び表示装置用データ転送方法

【課題】回路規模、消費電力が小さく、EMI特性に優れるクロックデータリカバリ回路の提供。

【解決手段】2倍オーバーサンプリングにより、入力データをサンプリングするサンプリング回路SCと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの周波数差を検出する周波数検出回路FDと、サンプリング回路SCによりサンプリングされた入力データとリカバリクロックとの位相差を検出する位相検出回路PDと、少なくとも位相検出回路PDにより検出された位相差に基づいて、サンプリング回路SCに対し、リカバリクロックを出力する電圧制御発振回路VCOと、入力データとして表示データを受信している間、周波数検出回路FDの動作を停止する周波数検出制御回路FDCと、を備えるクロックデータリカバリ回路。

(もっと読む)

クロックデータリカバリ回路

【課題】ジッタに高速に追従可能なCDR回路を提供する。

【解決手段】フリップフロップFF1〜FF4はそれぞれ、入力データDINを対応するクロック信号CKのタイミングでラッチする。i(iは自然数)番目の第1論理ゲートG1iは、(2×i−1)番目のフリップフロップFFの出力と(2×i)番目のフリップフロップFFの出力とが不一致のときアサートされる内部アップ信号UPを生成する。j(jは自然数)番目の第2論理ゲートG2jは、(2×j)番目のフリップフロップFFの出力と(2×j+1)番目のフリップフロップFFの出力とが不一致のときアサートされる内部ダウン信号dnを生成する。第3論理ゲートG3は、複数の内部アップ信号up1〜up2にもとづきアップ信号UP_Aを生成する。第4論理ゲートG4は、複数の内部ダウン信号dn1、dn2にもとづきダウン信号DN_Aを生成する。

(もっと読む)

クロック信号生成装置、電子装置、及び、PLL(PhaseLockedLoop)制御装置

【課題】所定のクロック信号の周波数を短時間で変更するとともに、クロック信号の周波数の変更時にクロック信号の供給先の動作が不安定になることを防止又は軽減するクロック信号生成装置等を提供する。

【解決手段】クロック信号生成装置等は、目標周波数が変更されると、第1制御部の代わりに、予め設定されている期間内に予め設定されている間隔かつ予め設定されている変更値で、クロック信号生成部に印加する電圧を順次変更し、クロック信号生成部が新たに生成するクロック信号の周波数を目標周波数に近づかせる第2制御部を備える。

(もっと読む)

OFDMAシステムのための2重周波数追跡ループ

無線デバイスによって受信された信号の搬送周波数とこのデバイスにとってローカルな基準信号との間の周波数誤差を修正するための方法および装置。ある幾つかの態様ではこのような方法は一般に、基準周波数を生成するLOと無線周波数(RF)位相ロックループ(PLL)とディジタルローテータとを有する受信機において信号を受信することと、上記受信された信号の搬送周波数と上記LO基準周波数との間の周波数差を推定することと、上記推定された周波数差を上記RF PLLと上記ディジタルローテータとに適用することと、を含む。  (もっと読む)

(もっと読む)

タイム/デジタルコンバーター及びデジタル位相ロックループ

【課題】 本発明の目的は、入力される2つの信号の位相差だけでなく周波数の差まで検出することができるタイム/デジタルコンバーター及びこれを用いるデジタル位相ロックループを提供することを目的とする。

【解決手段】 タイム/デジタルコンバーターが開示される。本タイム/デジタルコンバーターは、第1信号及び第2信号を受信し、直列接続された複数の遅延素子を用いて第2信号を段階的に遅延させ、遅延された第2信号と第1信号とを比較して第1信号に対する第2信号の位相エラーを出力するコンバーターと、第1信号及び複数の遅延素子のノードのうち一つのノードから第3信号を受信し、第1信号及び第3信号に対する位相差を出力する位相周波数検出器と、位相周波数検出器の出力信号と第2信号を用いて、第1信号に対する第2信号の周波数エラーをデジタルコードに出力する周波数検出器と、を含む。これにより、本タイム/デジタルコンバーターは入力される2つの信号間の位相差だけでなく周波数の差まで検出することができる。

(もっと読む)

ディスプレイ駆動装置

【課題】本発明は、ディスプレイ駆動装置に関する。

【解決手段】本発明はディスプレイ装置、特にディスプレイ装置に使用されるバックライトユニット駆動装置において、映像信号が正常である場合には映像信号の周波数に同期された周波数を有する駆動信号を提供し、映像信号が異常状態である場合には予め設定された周波数を有する駆動信号を提供して、安定的な動作を行うため、入力された映像信号の周波数と分周された駆動信号の周波数の差を検出する周波数検出部と、上記周波数検出部からの検出結果により、上記映像信号の周波数と同期された周波数を有する上記駆動信号を生成する駆動信号生成部と、上記周波数検出部からの上記検出結果が異常動作である場合、上記周波数検出部の周波数検出動作を停止させる制御部とを含むディスプレイ駆動装置を提供する。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

周波数シンセサイザ

【課題】広帯域を細かく設定でき、周波数の引き込み範囲が広い周波数シンセサイザを提供する。

【解決手段】電圧制御発振部の出力周波数の正弦波信号を直交検波し、検波に用いた周波数信号の周波数との差分の周波数(速度)で回転するベクトルを利用したPLLにて、周波数引き込み手段は、PLLから電圧制御発振部への制御電圧が予め設定した設定範囲よりも大きい場合には、出力周波数を上昇させるための第1の定数を引き込み用電圧として積分し、また当該制御電圧が前記設定範囲よりも小さい場合には、出力周波数を低下させるための第2の定数を引き込み用電圧として積分する。そして加算手段は、PLLからの制御電圧と周波数引き込み手段からの引き込み用電圧とを加算し、電圧制御発振部へ出力する。

(もっと読む)

信号追跡を行う信号生成器

入力信号を追跡するように出力信号の周波数及び位相が調整される。前記出力信号が導き出される発振信号の周波数を制御するように制御信号が調整される。幾つかの側面においては、前記発振信号の前記周波数は、発振器回路に結合されたリアクティブ回路の再構成によって調整される。前記出力信号の位相は、前記発振信号と調整可能スレショルドの比較に基づいて調整することができる。例えば、前記調整可能スレショルドは、トランジスタ回路に関する調整可能バイアス信号を備えることができ、それにより、前記発振信号は、前記トランジスタ回路への入力として提供され、前記トランジスタ回路の前記出力は、前記出力信号を提供する。 (もっと読む)

PLL回路および再生装置

【課題】データ信号からクロックを復調する際に、周波数ロックがはずれることを防ぎ、再生装置の再生品質を高める。

【解決手段】PLL回路200は位相追従ループと周波数追従ループを備える。周波数追従ループは、周波数比較器202とローパスフィルタLPF225とを備える。周波数比較器202は、復調クロックCLKとデータ信号S1との周波数差を検出し、検出結果に応じた周波数誤差信号を出力する。LPF225は、周波数誤差信号に応じて充放電するコンデンサ226の充放電により周波数誤差信号を平滑して周波数制御電圧信号FVCを得る。第1の制御部240と第2の制御部250は、周波数ロック状態において、周波数比較器202からLPF225への出力が遮断されるオフ期間と遮断されないオン期間が交互に繰り返されるように制御し、オフ期間においてリーク電流に起因するFVCの変動を補正する。

(もっと読む)

周波数/位相比較器

【課題】フルレートとハーフレートの両方に対応して、周波数比較モードおよび位相比較モードで正常動作を行うことのできる周波数/位相比較器を得る

【解決手段】フルレートおよびハーフレートのどちらに対してもクロック信号の振幅値をアナログホールド出力するアナログホールド位相比較部10と、フルレートの場合に1/4周期遅れのクロック信号の振幅をデジタルホールド出力し、ハーフレートの場合に1/8周期遅れのクロック信号の振幅をデジタルホールド出力するデジタルホールド位相比較部20、30と、アナログホールド値とデジタルホールド値に基づいて、入力データ信号とクロック信号の周波数比較を行う周波数比較手段50と、デジタルホールド値の極性に応じて、アナログホールド位相比較部10からの出力値と周波数比較手段50からの出力値を選択出力する最終出力信号選択手段60とを備える。

(もっと読む)

システムクロック供給装置及び基準発振器の周波数ずれ判定方法

【課題】システムクロック供給装置及び基準発振器の周波数ずれ判定方法に関し、装置内の基準発振器自身の周波数ずれを、測定用の発振器を用いずに判定し、周波数異常箇所を特定し、異常周波数クロックの送出を防ぐ。

【解決手段】二重化構成(N系及びE系)のシステムクロック供給装置内にそれぞれ備えられたOCXO等の基準発振器(#N,#E)9−1の出力クロックと、システム同期用に通常入力されるリファレンスクロック(例えば8KHz)とを、周波数ずれ測定部(#N,#E)1−1でそれぞれ比較し、所定回数の周波数ずれの発生を誤検出保護回路(#N,#E)1−2で測定し、該両系の測定結果を基に異常個所判定部(#N,#E)1−3で、自系若しくは他系の基準発振器(#N,#E)9−1の出力クロックの周波数ずれ又はリファレンスクロックの異常を判定して異常箇所を特定し、異常箇所を他系に切り替えるよう選択信号を送出する。

(もっと読む)

1 - 20 / 29

[ Back to top ]