Fターム[5J106JJ09]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素の特性改善 (824) | 同期・非同期検出回路 (38)

Fターム[5J106JJ09]に分類される特許

1 - 20 / 38

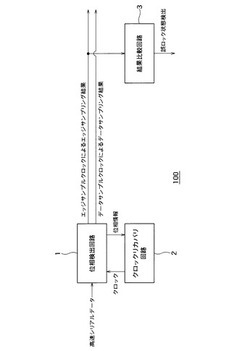

CDR回路

【課題】誤ロック状態を検出し、この誤ロック状態から復帰することが可能なCDR回路を提供する。

【解決手段】CDR回路は、受信データ信号のデータをサンプルすべきデータサンプリングクロックとして第1のクロックと、受信データ信号のエッジをサンプルすべきエッジサンプリングクロックとして第2のクロックと、を生成し、且つ第1のクロックおよび第2のクロックの位相を調整するクロックリカバリ回路を備える。CDR回路は、第1のクロックで受信データ信号をサンプルした結果をデータサンプリング結果として出力し、第2のクロックで受信データ信号をサンプルした結果をエッジサンプリング結果として出力する位相検出回路を備える。CDR回路は、エッジサンプリング結果と、予め設定されたデータパターンとを比較し、エッジサンプリング結果とデータパターンとが一致した場合、誤ロック状態であると判断し、誤ロック状態検出信号を出力する結果比較回路と、を備える。

(もっと読む)

情報処理システム

【課題】システムリセット時の起動時間を短縮可能な情報処理システムを提供する。

【解決手段】複数の機能モジュールの内の機能モジュール1では、システムリセット信号にてPLL回路10及び信号処理部12をリセットした後にPLL回路10へのリセットを解除する。リセット解除後にPLL回路10で生成された内部クロック信号がシステムクロック信号に位相ロックしていない場合には起動中を示す第1の起動状態信号を機能モジュール2に供給する。位相ロックしている場合には起動完了を示す第2の起動状態信号を機能モジュール2に供給すると共に信号処理部12へのリセットを解除する。機能モジュール2では、第1の起動状態信号にてPLL回路20及び信号処理部22をリセットする。そして、第2の起動状態信号にてPLL回路20へのリセットを解除し、リセット解除後に、位相ロックした時に信号処理部22へのリセットを解除する。

(もっと読む)

半導体装置、及び情報処理装置

【課題】

安定的な動作を確保できる半導体回路装置、及び情報処理装置を提供することを課題とする。

【解決手段】

半導体装置は、入力信号に遅延を与える遅延部と、前記遅延部から出力される出力信号の位相を検出する位相検出部と、前記位相検出部から出力される位相情報に基づき、前記出力信号の位相の安定動作範囲を設定する設定部と、前記安定動作範囲から位相が外れた前記出力信号の検出回数をカウントするカウンタと、前記遅延部の動作条件又は外的要因に応じて、前記カウンタのカウント数のディスカウント数を表すディスカウント信号を生成するディスカウント制御部と、前記カウンタのカウント数と前記ディスカウント信号が表すディスカウント数とに基づき、前記出力信号の位相のエラーの有無を判定するエラー判定部とを含む。

(もっと読む)

アンロック検出回路

【課題】2つの信号間の位相差の発生を正確に検出するアンロック検出回路を提供する。

【解決手段】アンロック検出回路は、論理値を基準信号の変化に応じて記憶する第1フリップフロップと、論理値を入力信号の変化に応じて記憶する第2フリップフロップと、当該第1及び第2フリップフロップの出力の否定論理積を算出するNAND回路とを備えた位相比較器と、第1フリップフロップの出力を基準信号の変化に応じて記憶する第3フリップフロップと、第2フリップフロップの出力を入力信号の変化に応じて記憶する第4フリップフロップとを備えた第1アンロック検出器と、NAND回路の出力を基準信号の変化に応じて記憶する第5フリップフロップと、NAND回路の出力を入力信号の変化に応じて記憶する第6フリップフロップとを備える第2アンロック検出器と、第3、第4、第5及び第6フリップフロップの出力の論理和を算出するOR回路とを具備する。

(もっと読む)

クロック装置

【課題】複数のクロック信号を出力するPLL回路において、その特性を問わず、リセットを従来よりも適切なタイミングで行うことを目的とする。

【解決手段】クロック装置は複数のクロック信号を出力するクロック回路を備え、出力するクロック信号を使用して動作している複数の周辺回路からエラー信号を受信し、受信したエラー情報を用いて、前記クロック回路をリセットするか否かを判定し、リセットすると判定した場合に、前記クロック回路をリセットする。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

デジタルロック検出装置及びこれを含む周波数合成器

【課題】デジタルロック検出装置及びこれを含む周波数合成器を提供すること。

【解決手段】本発明の一側面は、複数の制御ビートの入力を受け、複数の制御ビートのロッキング(Locking)の可否を通報するビート信号を生成し出力する比較部と、ビート信号から複数の遅延信号を生成した後、複数の遅延信号とビート信号を結合して1つのクロック信号を出力する遅延セルブロックと、クロック信号の遷移時点を検出し、その検出結果を反映するロック表示信号を生成する検出部を含むデジタルロック検出装置及びこれを用いた周波数合成器を提供することができる。

(もっと読む)

半導体集積回路装置

【課題】DLL回路においてロックはずれが発生しても、短時間で確実に正常ロック状態に復帰させる。

【解決手段】遅延回路13の遅延時間が1周期より小さくなると、遅延検出回路15から最小遅延時間検出信号K2が出力される。さらに位相周波数比較器11がUPパルスを出力していると、最小遅延時間検出信号K2とUPパルスとの2NOR論理(否定論理和回路21)によりクロックがUPパルスカウンタ19に伝達し、Hレベルのロックはずれ検出信号K3が出力され、リセット期間保持カウンタ17にLレベルが入力される。これにより、リセット期間保持カウンタ17がカウンタ動作を開始し、所定の期間、リセット信号をLレベルにして制御電圧CNTLを電源電圧にショートし、かつ位相周波数比較器11をリセットする。

(もっと読む)

デッドロック検出回路およびデッドロック復帰回路

【課題】誤検出することなく、デッドロック状態を正確に検出することができるデッドロック検出回路を提供する。

【解決手段】デッドロック検出回路は、PLL回路のデッドロック状態を検出するものであり、PLL回路の電圧制御発振器の出力信号を分周して、第1の分周クロックを出力するPLL内蔵分周器と、電圧制御発振器の出力信号を分周して、PLL回路の位相比較器へのフィードバッククロックとなる第2の分周クロックを出力するフィードバック分周器と、第1の分周クロックの周期によって決定される所定の期間に含まれる、第2の分周クロックのクロック数に基づいて、デッドロック状態であるか否かを表す判定信号を出力する誤ロック検出回路とを備えている。

(もっと読む)

CR発振クロック内蔵マイクロコンピュータ

【課題】CR発振クロックの周期調整が完了したかを判定できるCR発振クロック内蔵マイクロコンピュータの提供。

【解決手段】判定回路は、カウント数下限設定レジスタが示す値とカウント数上限設定レジスタが示す値との間に、外部発振パルスカウンタが示す値が収まっているかを判定する(S170)。収まっていると判定すると(S170でYes)、判定回路は、補正完了カウンタに格納されている値に1を足してカウントアップする(S180)。その後、出力回路が、補正完了カウンタのカウント数が補正完了カウント数設定レジスタに格納された値以上であるかを判断する(S190)。以上であると判断すると(S190でYes)、出力回路は、補正完了レジスタに「1」(周期調整が完了したことを示す情報)を入力する(S200)。そして、これらのステップを繰り返す。

(もっと読む)

タイミング回復のためのサイクルスリップ検出

【課題】タイミング回復のためのサイクルスリップ検出の提供。

【解決手段】タイミング回復のために制御ループ中のループフィルタLFの出力信号を使用するステップと、前記フィルタ処理後のタイミング誤差信号から平均タイミング誤差値を生成するステップと、第1の閾値を超えるサンプルの隣接するブロックの平均タイミング誤差値の変化を累積するステップとを含む。第2の閾値を超える隣接するブロックの累積した平均タイミング誤差変化がサイクルスリップとして表明され、サイクルスリップの数が許容閾値である第3の閾値によって決定される。さらに、先入れ先出しメモリFIFOがサンプル挿入または削除のために設けられ、それは、サンプル挿入またはサンプル削除が向上した信頼性を伴ってサンプル領域で行われ、サイクルスリップ検出の改善された方法が雑音および不適切に選ばれたタイミングループパラメータに対する頑健性の増強のために推奨される。

(もっと読む)

PLL回路

【課題】同期信号の位相が大きく変化する場合にも、短時間で位相を同期させる。

【解決手段】本PLL回路における位相比較器10は、映像信号に含まれる同期信号SYNと位相比較信号BLKとの位相誤差を示す比較出力信号PDPを出力し、VCO30は、比較出力信号PDPを積分するLPF20から与えられる直流電圧に応じた周波数のクロック信号CKを出力する。カウンタ40は、クロック信号CKを分周した位相比較信号BLKを出力する。ロック確認回路50は、位相比較信号BLKと同期信号SYNとの位相が同期すべきロック状態であるか否かを確認し、ロック状態でない場合にはリセット信号RSTを出力し、カウンタ40をリセットすることにより強制的にロック状態にすることができる。よって、短時間で位相を同期させることができる。

(もっと読む)

クロック信号生成回路、表示パネルモジュール、撮像デバイス及び電子機器

【課題】クロック生成回路が、ロック状態とは180°位相のずれた状態(擬似ロック状態)の出力クロックを出力する可能性がある。

【解決手段】遅延同期ループ型のクロック信号生成回路として、(a)第1のクロック信号を遅延して第2のクロック信号を生成する遅延線路と、(b)第2のクロック信号が第1のクロック信号に位相同期するように、遅延線路における遅延量を可変制御する遅延量制御部と、(c)第1のクロック信号と第2のクロック信号との擬似ロック状態を検出する擬似ロック検出部と、(d)擬似ロック状態の検出時、遅延線路の遅延量を変更する擬似ロック状態解除部とを有するものを提案する。

(もっと読む)

位相ロック回路

【課題】位相ロック回路において、電圧制御発振回路や分周回路の性能が設計時よりばらついた場合であっても、電圧制御発振回路が出力する高速クロックを分周回路で良好に分周できるようにして、不良品を低減する。

【解決手段】第1の分周回路4に加えて、この分周回路4よりも動作速度の遅い第2の分周回路5を備える。前記2つの分周回路4、5で分周されたクロックの周波数同士を周波数比較回路6で比較し、第2の分周回路5の分周クロックの周波数よりも第1の分周回路4の分周クロックの周波数の方が速い場合には、VCO発振抑制回路7が電圧制御発振回路3出力クロックFoutの発振周波数を抑制する。

(もっと読む)

PLL同期はずれ検出回路

【課題】電圧制御発振器から基準クロックと位相同期した出力クロックを得るPLL回路において、PLL同期はずれ検出回路の検出精度を向上させることを目的とする。

【解決手段】基準クロックと電圧制御発振器3の出力クロックの位相を比較して位相差に対応する信号を出力する位相比較器1と、位相比較器の出力により出力クロックの周波数を調整する電圧制御発振回路を有し、電圧制御発振器から基準クロックと位相同期した出力クロックを得るPLL回路において、時間を計測するタイマ6と、電圧制御発振器の出力クロックをカウントし、タイマからの信号でリセットされるカウンタ5と、カウンタのカウントした値が判定値を超えると信号を出力し、電圧制御発振器の出力クロック周波数増加方向の同期はずれを検出する検出器とを備える。

(もっと読む)

PLLロック検出回路および半導体装置

【課題】高精度のPLLロック検出信号を得るとともに、平滑回路を削除することができるPLLロック検出回路を提供する。

【解決手段】本発明に係るPLLロック検出回路は、PLL回路において、誤ってロック判定することなく、安定したロック状態においてロック判定とアンロック判定の両方を同時に行うことにより、確実なロック判定を行う。PLLロック状態が数H連続して継続しているかどうかの検出を行う連続性検出部と、PLLアンロック状態が数H連続して継続しているかどうかの判定行う連続性検出部を備え、これら連続性検出部によってPLLのロック状態が同時に検出され、その検出結果を保持するR−Sラッチ部を備えている。

(もっと読む)

アンロック信号検出方法

【課題】

解決しようとする課題は、PLL回路において周期的及びバースト的に生じるアンロックの検出を正確に行い、また、周囲温度の変化にも柔軟に対応することができるディジタル信号回路の中核となるクロック系及び無線部の搬送周波数の基準となる周波数の異常を正確に判断することを可能にすることである。

【解決手段】

PLL回路におけるアンロック検出方法であって、予め定められた周期でサンプリングし、アンロックであればカウンタでカウントアップし、予め定められた周期回数でカウントアップした値と予め定められたしきい値を制御部で比較し、カウントアップした値が予め定められたしきい値を超えている場合にアラーム信号を出力すること実現した。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、NCLK信号およびMCLK信号等の周波数が一致しているか否かを正しく判定できるようにする。

【解決手段】NCLP信号の分周信号であるNCLP2信号と、MCLP信号の分周信号であるMCLP2信号とを生成する。次に、MCLP2信号がHレベルのときはNCLP信号をアップ信号としてカウントし、MCLP2信号がLレベルのときはNCLP信号をダウン信号としてカウントし、そのカウント値をQN1、QN0信号で出力する。また、NCLP2信号がHレベルのときはMCLP信号をアップ信号としてカウントし、NCLP2信号がLレベルのときはMCLP信号をダウン信号としてカウントし、そのカウント値をQM1、QM0信号で出力する。そして、QN1、QN0、QM1、QM0の各信号に基づいて、NCLP信号とMCLP信号の各周波数が一致しているか否かを判定する。

(もっと読む)

周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法

【課題】周波数比較回路を少ない素子数で構成できるようにすると共に、第1、第2の信号(例えば、NCLK信号およびMCLK信号)の周波数が一致しているか否かを正しく判定できるようにした周波数比較回路、PLL周波数シンセサイザテスト回路及びそのテスト方法を提供する。

【解決手段】NCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたUP信号を生成するエッジ検出回路111aと、MCLK信号の立ち上がりもしくは立ち下がりのエッジを検出し、基準クロックで同期化されたDown信号を生成するエッジ検出回路111bと、UP信号及びDown信号をカウントし、そのカウント値をQ1、Q0信号で出力する2ビットアップダウンカウンタ112と、Q1、Q0信号に基づいて、NCLK信号の周波数とMCLK信号の周波数とが一致しているか否かを判定する判定回路113と、を有する。

(もっと読む)

DLL回路

【課題】Delay Locked Loop回路(DLL回路)の源クロック停止、動作中の源クロック周波数変化などの異常動作時にも、自動的にリセットを行い、正常ロックさせることが可能な擬似ロック防止回路を提供することを目的とする。

【解決手段】1はチャージポンプ回路、2は位相遅延回路、3は位相比較器、4は位相制御回路、5はリセット回路、8はチャージポンプ電圧比較回路、9は擬似ロック基準電圧発生回路である。ロック周波数による必要電圧は1のチャージポンプの電圧によって決定されるため、このチャージポンプ電圧を8のチャージポンプ電圧比較回路によりモニターし、9の擬似ロック基準電圧発生回路によって生成される、周波数ごとに変化する擬似ロック判定電圧レベル、源クロック停止判定電圧レベルと比較することで擬似ロック、源クロック停止、源クロック周波数変動を認識する。

(もっと読む)

1 - 20 / 38

[ Back to top ]