Fターム[5J106KK40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 省電力化 (216)

Fターム[5J106KK40]に分類される特許

141 - 160 / 216

撮像装置

【課題】サンプルホールドタイミングを高精度に決定しながらも消費電力を抑えることが可能な撮像装置を提供する。

【解決手段】撮像素子と、撮像素子から出力される撮像信号OSに相関二重サンプリング処理等を行うAFEとを有するデジタルカメラであって、DLL回路40と、AFEを制御するための制御信号(サンプルホールドタイミングパルスshp)をDLL回路40から出力されるクロックpulseに基づいて生成するパルス発生回路と、ブランキング期間中、DLL回路40を、そのロック状態を維持させたまま停止させる制御を行うDLL制御部51とを備える。

(もっと読む)

ヘテロダイン受信機、PLL発振回路及び間欠受信制御方法

【課題】PLL発振回路を使用して間欠受信動作を行う受信機のオン・オフ時間の比率を大きくして、省電力効果の向上を図ったPLL発振回路、ヘテロダイン受信機及びその間欠受信制御方法を提供する。

【解決手段】PLL発振回路の要部への電源制御用第一のスイッチと、位相比較器と低域フィルタとの間に挿入した第二のスイッチ回路とを備え、これらを間欠的に制御することにより、PLLの同期を促進する。

(もっと読む)

半導体集積回路

【課題】本発明は、Ser/Des回路において、休眠ステートからパワーアップの状態へ遷移した際の受信エラーを減少できるようにする。

【解決手段】たとえば、受信機21が、休眠ステートP1からパワーアップの状態P0に遷移したとする。すると、リセット制御回路21mは、ディレイ回路21m-1によって、PLL31からのシステムクロックのカウントを開始する。そして、ディレイ回路21m-1がXサイクルをカウントした後に、リセット制御回路21mは、ディジタルフィルタ21eおよびPI制御回路21fのリセットを解除するように構成されている。

(もっと読む)

クロック制御回路

【課題】発振回路からの基準クロックを供給し続けなくても、PLL回路からの所定のクロックの出力を継続させることができるようにする。

【解決手段】電圧信号V0に応じた周波数の動作クロックCKを生成する電圧制御発振器3と、動作クロックから比較クロックCKrを生成する分周回路4と、比較クロックを発振回路1の基準クロックCK0と位相比較して位相比較信号S1を生成する位相比較器5と、位相比較信号を第1の電圧信号V1に変換するローパスフィルタ7と、第1の電圧信号から第2の電圧信号V2を生成する電圧制御回路8と、第1の電圧信号と第2の電圧信号の一方を選択して電圧制御発振器3へ出力する選択回路9と、選択回路9に初期には第1の電圧信号を選択させ、電圧制御回路8が第2の電圧信号を生成した後は、選択回路に第2の電圧信号を選択させるとともに、発振回路1の動作を停止させる制御手段(CPU)10を備える。

(もっと読む)

遅延同期ループ回路

【課題】遅延同期ループ回路を提供する。

【解決手段】入力された外部クロック信号を精密遅延量ほど遅延させて第1内部クロック信号として出力する第1遅延ライン、及び第2クロック信号を粗い遅延量ほど遅延させて第2内部クロック信号として出力する第2遅延ラインを具備する遅延同期ループ回路であり、該第1遅延ライン及び第2遅延ラインは順次に配され、第2クロック信号は、第1内部クロック信号を利用して生成される。これにより、粗い遅延調節と精密調節とをそれぞれ異なる形態の遅延セルを利用することによって、パワー消耗が少なく、かつジッタ発生及びPVT変数に強靭な特性を有する遅延同期ループ回路が得られる。

(もっと読む)

電圧制御発振回路およびPLL回路

【課題】出力クロックの変動を抑えることができる電圧制御発振回路およびPLL回路を提供する。

【解決手段】この電圧制御発振回路によれば、第2の電源生成回路1−2が出力するゲート制御信号103,104によって、一部の反転回路10−nの遅延時間を変更制御するが、残りの反転回路10−1〜10−(n−1)の遅延時間は第1の電源生成回路1−1によって一定に制御する。したがって、第2の電源生成回路1−2が制御する電源電圧103−n,104−nが変化(変動)しても出力クロック100の周波数の変化(変動)は従来のように全ての反転回路の遅延時間を変更制御する場合に比べて小さい。

(もっと読む)

リアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器

【課題】低消費電流および安定動作を実現することができるリアルタイムクロック装置および該リアルタイムクロック装置を用いた半導体装置ならびに電子機器を提供すること。

【解決手段】水晶発振回路11と、該水晶発振回路11の出力を分周する計時回路(高速部)13と、計時回路(高速部)13の出力を分周する計時回路(低速部)14と、外部との間で信号のやり取りをするインターフェース回路15からなり、水晶発振回路11は第一の電圧VR1で駆動され、計時回路の少なくとも一部分(高速部)13は第二の電圧VR2で駆動され、計時回路の残りの部分およびインターフェース回路15は第三の電圧VDDで駆動され、第一の電圧VR1<第二の電圧VR2<第三の電圧VDDの大小関係を有する。第一の電圧VR1と第二の電圧VR2は第三の電圧VDDから生成される。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】DLL回路を備えた半導体記憶装置のチップを複数備えた半導体装置の消費電力の低減。

【解決手段】DLL(Delay Lock Loop)を備えた半導体記憶装置の積層モジュールまたは半導体記憶装置を複数有するマルチチップモジュール(MCM)において、DLLで遅延調整されたクロック信号(CLK)を、一の半導体記憶装置と他の半導体記憶装置間で共用するための専用パッド(PAD)を有し、一の半導体記憶装置のDLLを動作させ、他の半導体記憶装置ではDLLを動作させず、一の半導体記憶装置の前記専用パッドから、DLLで遅延調整されたクロック信号(CLK)から作られる、差動の外部クロック信号(CLK、CLKB)に同期した、フライングロッククロック信号を出力し、他の半導体記憶装置は、フライングロッククロック信号を、専用パッドから入力する。

(もっと読む)

インピーダンス回路およびこれを用いた信号生成回路

【課題】基準周波数を得る場合、安定した周波数、もしくは遅延要素を得る回路を提供する。

【解決手段】第1の温度変動率を持つ第1のインピーダンス回路1と第1の能動回路3で構成した第1の発振回路6と、第1の温度変動率とは逆の変動方向となる第2の温度変動率を持つ第2のインピーダンス回路2と第2の能動回路4で構成した第2の発振回路7との出力を時系列的に交互に切替器5で選択する。第1のインピーダンス回路1の温度係数の絶対値が第2のインピーダンス回路2の温度係数より大きいとき、第1の発振回路6の使用時間を短くし、温度係数の小さい第2の発振回路7の使用時間を長く動作させるように、温度係数の比と逆の比率で発振回路の使用時間の比率を設定する。温度変動方向が逆の2つの温度係数を有することから、平均値として温度変動がほぼなく軽減される。時間平均値として温度変動が極めて小さく温度変動率の改善された発振周波数を得る。

(もっと読む)

マルチモジュラス・デバイダ・リタイミング回路

マルチモジュラス・デバイダ(MMD)がMMD入力信号を受信しかつMMD出力信号SOUTを出力する。MMDはモジュラス・デバイダ・ステージ(MDSs)のチェーンを含む。各MDSは入力信号を受信し、それを2又は3で割り、そしてその結果を出力信号として出力する。各MDSは、それが2で割るか又は3で割るかを制御するそれ自体のモジュラス制御信号に応答する。1つの実例では、順次論理素子がSOUTを出力する。前記チェーンの第1のMDSステージのうちの1つのロージッタ・モジュラス制御信号が、順次論理素子を第1の状態に置くために用いられる。前記チェーンの中間におけるMDSステージうちの1つの出力信号が、前記順次論理素子を第2の状態に置くために用いられる。前記順次論理素子は前記MMD入力信号の高い周波数でクロックされないので、電力消費は低い。  (もっと読む)

(もっと読む)

光ディスク装置のPLL回路

【課題】回路規模や消費電力の増加を抑えつつ、充分な性能を有するウオブルPLLを構成する。

【解決手段】ウオブリングされたトラックを有する光ディスク1の反射光に基づいてウオブリング信号を検出するウオブル検出器と、入力に応じて出力の発振周波数が変化するVCO10とを有し、ウオブリング信号出力とVCO10の出力との位相誤差により、VCOを制御する光ディスク装置のPLLにおいて、ウオブリング信号を所定のクロックでデルタシグマ変調する変調器7と、変調器出力とVCOの出力とをクロックで演算する演算器8と、演算器8の出力の低域成分だけを通過させるロー・パス・フィルタ9と、を有し、ロー・パス・フィルタ9の出力に基づいて、VCO10を制御する。

(もっと読む)

CDR回路

【課題】入力データに含まれているジッタを削除した再生データを得る。

【解決手段】入力データのデータレート周波数と同じ周波数の参照クロックを入力データにより位相合わせして再生クロックを作成し、該再生クロックにより前記入力データをFIFO101に書き込む。該FIFO101からの読み出しには、前記再生クロックと同期関係にない前記参照クロック又は別のクロックを使用し、前記FIFO101から再生データを出力させる。

(もっと読む)

低電力のモジュラス分周器ステージ

モジュラス分周器ステージ(MDS)は、第1と第2のステージを含んでいる。MDSは、MDSが2分割モードまたは3分割モードのいずれで動作するかを決定するモジュラス除数制御信号Sを受信する。MDSのステージは、他のMDSからフィードバック・モジュラス制御信号も受信する。MDSは、2分割モードの場合、フィードバック・モジュラス制御信号にかかわらず、2で分割(分周)する。電力を節約して使用するため、MDSステージが2分割モードで動作するとき、第1のステージには電力が供給されない。MDSは、3分割モードの場合、フィードバック・モジュラス制御信号に依存して2または3のいずれかで分周する。電力消費をさらに減らすため、MDSステージが3分割モードにあるにもかかわらず2分割動作を行っているとき、第1のステージには電力が供給されない。第1のステージが電力供給されていないとき、電力ダウントランジスタは、第1のステージの出力を適正な論理レベルに維持する。 (もっと読む)

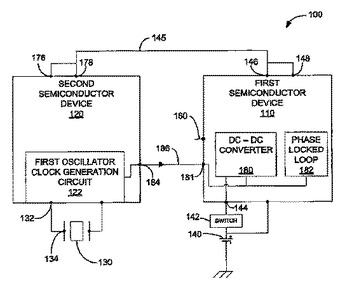

半導体デバイス及び水晶発振体を共有するシステム並びに方法

システムは、第1の半導体デバイス、第2の半導体デバイス、及び外部水晶発振器を含む。第1の半導体デバイスは、電源電圧出力及び外部ピン入力を含む。第1の半導体デバイスは、電源電圧出力を提供する直流−直流(DC-DC)変換回路を含む。第2の半導体デバイスは、第1の半導体デバイスの電源電圧出力に接続された電源電圧入力とクロック信号出力とを含む。外部水晶発振器は、第2の半導体デバイスを介して第1の発振クロック発生回路に接続されている。  (もっと読む)

(もっと読む)

チャージポンプ回路及び位相同期ループ回路

【課題】回路規模や消費電流の増大を抑えつつ、スプリアス成分を十分に抑制できるチャージポンプ回路とこれを備えたPLL回路を提供する。

【解決手段】第1駆動信号Supとその複数の遅延信号に応じて複数の電流が生成されて共通のノードN1へ流出し、第2駆動信号Sdnとその複数の遅延信号に応じて複数の電流が生成されて共通のノードN2から流入する。これにより、チャージポンプ回路自体に櫛型フィルタとしての機能を併せ持たせる。

(もっと読む)

周波数シンセサイザ、および周波数シンセサイザの発振制御方法

【課題】 ロック状態を維持したまま発振周波数帯域の切り替え動作が可能な周波数シンセサイザを、小規模であって低消費電流な回路構成で実現する周波数シンセサイザ、および周波数シンセサイザの発振制御方法を提供すること

【解決手段】 発振周波数帯域の切り替えが可能な発振制御回路2を備える周波数シンセサイザ1は、発振周波数帯域の違いによる発振制御回路2へのバイアス信号IBの差を、差分バイアス信号ΔIBとして出力する差分バイアス部5と、発振周波数foが発振周波数帯域fbの限界値を越えて遷移したことを検出する帯域限界検出部3と、帯域限界検出部3による検出に応じて、発振周波数帯域fbの切り替えのために差分バイアス部5の動作が切り替えられる過渡期間において、差分バイアス部5に対して、出力されるバイアス信号IBを漸次遷移する制御を行なう過渡制御部4とを備えている。

(もっと読む)

位相同期ループ回路、半導体集積回路、および、受信装置

【課題】使用する電圧制御発振器の選択、および、その発振周波数範囲の設定をより効率的に行うことができる位相同期ループ回路を実現する。

【解決手段】位相同期ループ回路100の制御部103は、位相同期ループ回路100に接続する電圧制御発振器として、複数の電圧制御発振器VCO1〜VCOnのうちから、選局周波数を含む主発振周波数範囲をもつ電圧制御発振器を選択し、その後、選択された電圧制御発振器の発振周波数範囲を、選局周波数を含む副発振周波数範囲に設定する。

(もっと読む)

PLLシンセサイザ

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足させるPLLシンセサイザを構成する。

【解決手段】 可変整数分周器と可変分数分周器としての機能を有し、外部からの切換信号によりこの2つの分周器の機能を切り換える手段を含む切換型可変分周器と、外部からの切換信号により分周比の切り換えが可能な切換型基準分周器と、切換型可変分周器を可変分数分周器として機能させ、かつ切換型基準分周器の出力信号の周波数が電圧制御発振器の出力信号の周波数チャネル間隔より大きくなるようにその分周比を設定する分数分周モードと、切換型可変分周器を可変整数分周器として機能させ、かつ切換型基準分周器の出力信号の周波数が電圧制御発振器の出力信号の周波数チャネル間隔に等しくなるようにその分周比を設定する整数分周モードを切り換える切換制御回路を備える。

(もっと読む)

クロック生成回路、情報再生装置、電子機器及びクロック生成回路の設計方法

【課題】 PLLを用いることなく、低コスト且つ低消費電力で、複数のクロックを生成するクロック生成回路、情報再生装置、電子機器等を提供する。

【解決手段】 クロック生成回路200は、周波数fHを有する入力クロックiclkに基づいて、第1の出力クロック及び周波数f0を有する第2の出力クロックを生成する。クロック生成回路200は、前記入力クロック又は該入力クロックを間引いたクロックを第1の分周比d1(d1は正の整数)で分周した前記第1の出力クロックを生成する第1の分周カウンタと、前記第1の出力クロックを第2の分周比d2(d2は正の整数)で分周し前記第2の出力クロックを生成する第2の分周カウンタと、前記第2の出力クロックに基づいて、前記第1の分周カウンタで分周される前記入力クロックの間引き制御を行う間引き制御部とを含む。

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループ及びそこから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

141 - 160 / 216

[ Back to top ]