Fターム[5J106KK40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 省電力化 (216)

Fターム[5J106KK40]に分類される特許

41 - 60 / 216

局部発振器

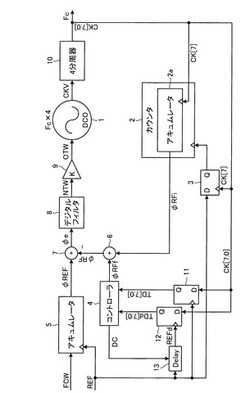

【課題】消費電力を増大させることなく、TDCレスが可能な局部発振器を提供することを目的とする。

【解決手段】発振器制御ワードに応じた発振周波数のN倍の周波数の発振信号を出力するデジタル制御発振器と、前記発振信号をN分周して、2N相のクロックを出力する分周器と、前記クロックを前記参照信号でラッチして、第1位相情報として出力する第1のフリップと、前記参照信号を遅延させて、遅延参照信号として出力する可変遅延回路と、前記クロックを遅延参照信号でラッチして、第2位相情報として出力する第2のフリップフロップと、前記可変遅延回路の遅延量を制御する遅延制御手段と、前記1および第2の位相情報に基づいて、発振器整数位相を出力するデータ変換手段と、発振器整数位相と前記発振器分数位相とを加算し、加算値を第3位相情報として出力する加算器とを備えている。

(もっと読む)

デジタル制御発振器

【課題】周波数制御により生じるノイズを低減すると共に、制御線を減少させて消費電力および面積を削減することが可能なデジタル制御発振器を提供する。

【解決手段】発振器制御ワードに応じた発振周波数の発振信号を出力するデジタル制御発振器であって、Nビットの前記発振器制御ワードを、上位N−A(但し、A≧1で、N>A)ビットと下位Aビットに分割し、前記上位N−AビットをN−AビットのBynary制御を行う第1のコードOTWbに、前記下位Aビットを2^(A+1)−2ビットのUnary制御を行う第2のコードOTWuに変換して出力する制御手段と、前記制御手段から出力される前記第1および前記第2のコードに応じた発振周波数の発振信号を出力する発振器24と、を備えている。

(もっと読む)

サブサンプリングされた周波数ロックループを備える送受信機

位相同期ループ回路、半導体集積回路、電子機器、位相同期ループ回路の制御方法

【課題】位相同期ループ回路において、制御応答の改善や消費電力の低減を図る。

【解決手段】発振器制御部255と分周器制御部257は、発振制御信号と分周制御信号が、引込み過程およびロック時の双方において、ループフィルタ電圧に基づいて比例関係を持って連動して変化するようにする。発振部210と分周部220が引込み過程およびロック時の双方において連動した動作をする。引込み過程およびロック時の双方における任意のループフィルタ電圧に対応する分周部220の最高動作周波数が発振部210の発振出力信号の周波数よりも常に高くなるように各制御信号の関係を設定する。ロック時の分周制御信号は、引込み過程における発振部210の発振出力信号の最高周波数と対応するループフィルタ信号に基づくバイアス電流よりも小さなバイアス電流を分周部220に自動的に設定するようになる。このことにより、ロック時の電力消費を低減できる。

(もっと読む)

記憶装置およびDLL回路制御方法

【課題】セルフリフレッシュ動作後にDLL回路がロック動作を実行しない状況での記憶装置の評価を行うことが可能な記憶装置を提供する。

【解決手段】通常モードとテストモードとを有しセルフリフレッシュ動作を行う記憶装置は、DLL回路と制御部とを含む。DLL回路は、入力信号を受け付けると入力信号を遅延した遅延信号を出力し、また、入力信号と遅延信号との位相差が所定値になるように遅延信号の遅延量を設定するロック動作を行い、その後、位相差が所定値である状態を維持する。制御部は、通常モード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させ、テストモード下でセルフリフレッシュ動作が実行された後には、DLL回路にロック動作を実行させない。

(もっと読む)

原子発振器

【課題】回路部分の小型化や省電力化が容易な原子発振器を提供する。

【解決手段】原子発振器1は、アルカリ金属原子に共鳴光対を照射することにより生じる電磁誘起透過現象を利用する原子発振器であって、光源10、気体状のアルカリ金属原子20、光検出部30、周波数制御部40を含む。光源10は、可干渉性を有し、周波数が異なる第1の光と第2の光を含む複数の光を発生させて、アルカリ金属原子20に照射する。光検出部30は、アルカリ金属原子20を透過した複数の光22を受け取り、当該複数の光22の干渉により得られる所定の周波数のビート信号を含む検出信号32を生成する。周波数制御部40は、検出信号32に含まれる所定の周波数のビート信号に基づいて、第1の光と第2の光がアルカリ金属原子20に電磁誘起透過現象を起こさせる共鳴光対となるように、第1の光及び第2の光の少なくとも一方の周波数制御を行う。

(もっと読む)

差動論理回路、分周回路、及び周波数シンセサイザ

【課題】動作電流を変えても直流出力電圧の変わらない差動論理回路及び分周回路、さらには、周波数シンセサイザにおける動作電流の調整方法を提供する。

【解決手段】複数対の差動論理信号を入力し論理演算を行ってその結果を一対の差動信号出力端子から出力する差動論理部と、差動論理部に電流を供給する電流源回路であって前記電流の大きさが制御可能な電流源回路と、差動信号出力端子に接続された負荷回路と、負荷回路に接続され、一対の差動信号出力端子の直流出力電圧が一定の電圧になるように負荷回路の負荷を制御する負荷制御回路と、を備える。

(もっと読む)

CDR回路

【課題】入力データに対する瞬時応答特性を備えかつジッタが大きな入力データが入力された時にも出力ジッタを低減可能な小型低消費電力のCDR回路を提供する。

【解決手段】CDR回路は、入力データ4のタイミングに合うように出力クロックの位相を調整するVCO11と、VCO11の出力クロックのタイミングに合うように再生クロック7の位相を調整するVCO13と、VCO11,13の発振周波数を制御する制御信号8を発生する周波数制御回路である周波数比較器2およびVCO12と、VCO11の出力端子とVCO13の入力端子との間に挿入された減衰器30とを備える。

(もっと読む)

位相検出回路および方法

【課題】 相当量の電力を消費し、かつジッタを生成する分周器回路を必要とせずに、高周波周期出力信号を生成する位相ロックループを提供すること。

【解決手段】 位相検出器回路は、第1および第2周期入力信号の位相を比較して、出力信号を生成する。位相検出器は、第1および第2周期入力信号の2つの異なる組み合わせを作り、第3および第4周期信号を生成する回路を備える。この回路は、第3周期信号を、第1相対位相シフトを付与する、第1周期信号および第2周期信号の第1の組み合わせに基づかせる。この回路は、第4周期信号を、第1周期信号および第2周期信号の第2の組み合わせに基づかせて、異なる相対位相シフトを提供する。位相検出器は、また、第3周期信号の電力の大きさを第4周期信号の電力の大きさと比較して、位相比較出力信号を生成する比較回路も備える。

(もっと読む)

レジスタ制御ディレイロックループを備えた半導体デバイス

【課題】DLLクロックの無用なトグリングによる電流の消耗を低減することができるレジスタ制御ディレイロックループを備えた半導体デバイスを提供する。

【解決手段】レジスタ制御ディレイロックループから出力されたDLLクロックを用いる内部回路を備えた半導体デバイスにおいて、半導体デバイスに対する作動信号及び非作動信号に応答して、内部回路に印加されるDLLクロックをイネーブルしたりディスエーブルしたりするクロックイネーブル信号を生成する手段を備える。その場合、クロックイネーブル信号を生成する手段は、作動信号又は非作動信号に応答してプルダウン又はプルアップ動作を行う駆動手段と、半導体デバイスに対する作動信号に応答して駆動手段の出力ノードをリセットするリセット手段と、駆動手段の出力ノードに印加された信号をラッチし、バッファリングして出力する出力手段とを備えている。

(もっと読む)

ディレイロックループのディレイロック状態の情報の使用が可能な半導体素子

【課題】階層的遅延ラインを有するディレイロックループのディレイロック状態を検出し、ディレイロック状態の情報の使用が可能な半導体素子を提供する。

【解決手段】

コース遅延ライン及びファイン遅延ラインを有する階層的遅延ライン構造のディレイロックループブロックと、ディレイロックループブロックから出力された位相比較信号及びコース遅延調整終了信号に応答してコース遅延調整終了時点での比較対象クロックの位相状態を記憶する位相状態記憶手段と、位相比較信号、コース遅延調整終了信号及び位相状態記憶手段から出力された位相状態信号に応答して、ファイン遅延調整に係る位相比較信号の遷移時点を検出して、その時点にアサートされるディレイロック信号を生成するディレイロック状態検出手段とを備えてなる。

(もっと読む)

プログラマブルロジックデバイス回路に結合されるクロックデータリカバリ回路

【課題】プログラマブルロジックデバイス上またはこれと結合して設けられるクロックデータリカバリ回路の提供

【解決手段】プログラマブルロジックデバイス(“PLD”)が多数のCDRシグナリングプロトコルのうちの任意のものによって交信することを可能にするため、このPLDにプログラマブルクロックデータ復元(“CDR”)回路を装備する。CDR回路は、PLD内に内蔵するか、完全あるいは部分的に独立した集積回路とすることができる。この回路は、CDR入力、CDR出力、またはそれらの両方を行うことができる。CDR機能は、例えば非CDR低電圧作動シグナリング(“LVDS”)等のその他の非CDRシグナリング機能と組合わせて提供することができる。この回路は、大規模なシステムの一部とすることができる。

(もっと読む)

パルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置

【課題】 駆動中の論理ゲートを減らして消費電力を少なくし、クロックが通る論理ゲート数を減らしてクロック遅延を短くしたパルスエッジ選択回路と、それを使ったパルス生成回路、サンプルホールド回路及び固体撮像装置を提供する。

【解決手段】 パルスエッジ選択回路が、複数のクロックから1つのクロックを選択して通過させる入力段と、前記1つのクロックをエッジ検出回路に出力する出力段とを有し、クロックの立ち下がりエッジを検出して、第1のクロックの立ち下がりエッジで立ち上がり、第2のクロックの立ち下がりエッジで立ち下がるパルスを生成するエッジ検出回路の場合に、前記出力段は、複数の入力端を有する複数のNORゲート及び複数の入力端を有する複数のNANDゲートを交互に組み合わせて接続されており、前記第1及び第2のクロックを出力する出力ゲートにはNORゲートが使用される。立ち上がりエッジでパルスを生成する場合、出力ゲートにはNANDゲートが使用される。

(もっと読む)

周波数−電流フィードバックを有する温度安定形発振回路

フェーズロックループや低周波温度安定形発振器を必要としない信号生成回路(600)および方法が開示される。この方法は、振動出力信号の周波数を制御するフィードバック信号(608)に応じて振動出力信号(CLK1〜CLKN)を生成することと、振動出力信号の周波数に対応する大きさを有する電流出力信号を生成することと、フィードバック信号を生成するために電流出力信号を基準信号(654)と比較することとを含んでよい。信号生成回路(600)は、フィードバック信号(608)に反応する発振回路(602)と、振動出力信号の周波数に対応する周波数依存性電流信号を生成する周波数−電流変換回路(620)とを含んでよい。発振回路へ向けてフィードバック信号(608)を生成するため、フィードバック変換回路(612)は出力信号を基準信号(654)と比較する。  (もっと読む)

(もっと読む)

内部コマンド生成回路

【課題】電流消耗を減少させることができる内部コマンド生成回路を提供する。

【解決手段】本発明の内部コマンド生成回路は、読出しまたは書込み動作のためのコマンドを受信して、所定の周期で発生する複数のパルスを含む第1バーストパルスを生成するバーストパルス発生部と、前記第1バーストパルスをシフトして内部コマンドを生成するパルスシフト部と、を含み、前記内部コマンドは、バースト終了信号またはバーストコマンドのパルスが入力されるとディセーブルされる。

(もっと読む)

電圧制御発振器及びそれを備えた無線通信装置

【課題】バイアス抵抗の抵抗値を大きい値に維持して省電力化及び発振効率の向上を図りつつ、広帯域の変調信号に対応することができる電圧制御発振器及びそれを備えた無線通信装置を提供すること。

【解決手段】

印加される電圧に応じて静電容量値が変化するバラクタM1,M2を有し、当該バラクタM1,M2に制御端子T2を介して印加される制御信号に応じて共振周波数が変化する共振回路30と、共振回路30と並列に接続された負性抵抗回路40とを備え、制御信号の逆相信号が制御端子T3を介して印加されるキャパシタC3、C4をバラクタM1,M2に接続した。

(もっと読む)

半導体装置

【課題】デジタルDLL回路における消費電力を低減するとともに、ノイズによる電源電圧の変動の影響を軽減することが可能な半導体装置を提供すること。

【解決手段】デジタルDLL回路を備える半導体装置において、位相比較の間欠間隔を設定する間欠間隔設定回路を設ける。間欠間隔設定回路による間欠間隔の設定は、外部から入力される設定信号に基づいて制御する。これにより、ノイズによる電源電圧の変動の影響を軽減し、平均化された遅延素子の段数の調整が可能となる。

(もっと読む)

クロック信号を生成できる、または各トランシーバに関連付けられたデジタル・システムのデータのバイパスを可能にする、電力管理されたトランシーバのネットワークを使用する通信システム

【課題】感知回路の雑音感受性を最小にするとともに、回路の少なくとも一部に対する電力を管理して、消費電力を少なくした通信システムを提供する。

【解決手段】通信システムはノードのセットを含む。各ノードはトランシーバ・インターフェイスとデジタル・システムを含む。トランシーバは、通信回線とデジタル・システムとの間に結合されており、伝送フォーマットおよび/または伝送プロトコルを対応するノード内の1つまたは複数のデジタル・システムにより認識されるビットのシーケンスに修正する。トランシーバは、デジタル・システムを支持する回路基板から分離された1つまたは複数のモノリシック回路基板に配置される。

(もっと読む)

クロック生成回路及びこれを備える半導体装置並びにデータ処理システム

【課題】クロック生成回路の消費電力を低減する。

【解決手段】内部クロック信号LCLKを生成するディレイライン110と、ディレイライン110を制御することによって内部クロック信号LCLKの位相を調整する位相制御部120と、位相制御部120の動作モードを切り替えるモード切り替え回路130とを備える。位相制御部120は、サンプリングクロック信号SYNCLK2に同期して内部クロック信号LCLKの位相を変化させる第1の動作モードと、内部クロック信号LCLKの位相を固定させる第2の動作モードを有しており、モード切り替え回路130は、リフレッシュ信号REFBなどのトリガ信号に応答して位相制御部120を第1の動作モードに遷移させ、内部クロック信号LCLKが所望の位相に達したことに応答して位相制御部120を第2の動作モードに遷移させる。

(もっと読む)

チャージポンプ回路及びそれを用いるPLL回路

【課題】電流供給および吸入用の定電流源と、それらの定電流源の間に設けられる2つの直列に接続されたスイッチ素子から成り第1の出力端子を持つ主出力側電流路と、同様に2つのスイッチ素子から成り第2の出力端子を持つ副出力側電流路とを備え、位相比較器からの駆動信号に応答して、主出力側電流路のスイッチと副出力側電流路との各スイッチ素子が開閉し、第1の出力端子から正負の電流パルスが出力される差動スイッチング方式のチャージポンプ回路において、ダイ面積を縮小するとともに、消費電力を削減する。

【解決手段】主出力側電流路のスイッチ素子Q7,Q8間の電位と副出力側電流路のスイッチ素子Q5,Q6間の電位との差に起因して定電流源Q3,Q4の寄生容量の充放電に伴い発生する緩慢なグリッチを補償するために、コンパレータ37と、ラッチ回路38と、コンデンサC1と、充放電器Q9,Q10とを用いてグリッチ補償回路36を構成する。

(もっと読む)

41 - 60 / 216

[ Back to top ]