Fターム[5J106KK40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 省電力化 (216)

Fターム[5J106KK40]に分類される特許

61 - 80 / 216

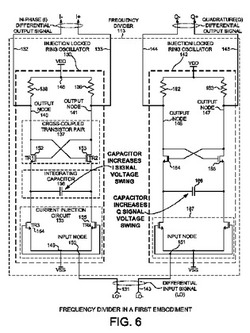

2分周インジェクションロックリング発振器回路

【解決手段】周波数分周器は、複数のインジェクションロックリング発振器(ILRO)を含む。第1ILROは、クロスカップルされたNチャネルトランジスタの対、負荷抵抗の対、インテグレイトキャパシタ、及び電流注入回路を含む。各トランジスタのドレインは、他方のトランジスタのゲートに結合される。各負荷抵抗は、各トランジスタのドレインを回路電圧源に結合する。インテグレイトキャパシタは、各トランジスタのソースに結合する。電流注入回路は、第1周波数の発振入力信号に応答して、各トランジスタのソースから回路グランドへのパスを交互にオープン及びクローズする。これに応答して、各トランジスタのドレインの電圧状態は交互にラッチ及びトグルされて、2分周された発振信号の差動対が生成される。逆位相で駆動される第1及び第2ILROは、位相直交する2つの差動出力信号を生成する。 (もっと読む)

復調器及び通信装置

【課題】受信信号と局部発振信号とに位相差があっても復調できるようにする。

【解決手段】復調器1は、変調器2で送信された受信信号D3をアンテナ11で受信し、この受信した受信信号D3をVCO13に注入して、自走発振周波数を有する局部発振信号D6を発振する。この発振した局部発振信号D6を90度移相器で90度移相する(局部発振信号D7になる)。アンテナ11で受信した受信信号D3の位相と90度移相器で90度移相した局部発振信号D7の位相とを位相比較器15で比較して、局部発振信号D6の位相を調整するための位相調整信号Vctを生成する。この生成した位相調整信号Vctに基づいて、受信信号D3と局部発振信号D6とをVCO13で同期させ、該同期させたものである局部発振信号D8をミキサ17に入力する。注入同期後の局部発振信号D8と受信信号D3とをミキサ17で演算して当該受信信号D3を復調する。

(もっと読む)

位相同期ループ回路および通信機

【課題】低消費電力化と小型化とが両立されたPLL回路を提供する。

【解決手段】PLL回路の位相比較器2は、カウンタ16と時間デジタル変換器13とを含む。カウンタ16は、参照クロック信号REFと、デジタル制御発振器の出力を分周した低周波クロック信号CLKAおよび高周波クロック信号CLKBとを受ける。カウンタ16は、高周波クロック信号CLKBのクロック数をカウントすることによって参照クロック信号REFと低周波クロック信号CLKAとの位相差を検出する。時間デジタル変換器13は、参照クロック信号REFと低周波クロック信号CLKAとを受ける。時間デジタル変換器13は、カウンタ16の出力が所定範囲になってから、参照クロック信号REFと低周波クロック信号CLKAとの位相差を、高周波クロック信号CLKBの周期よりも短い時間の精度で検出する。

(もっと読む)

局部発振器経路内の平均消費電流を低減するためのシステムおよび方法

局部発振器(LO)経路内の平均消費電流を低減するための方法が開示される。LO信号は、マスター分周器とスレーブ分周器とで受信される。マスター分周器からの出力は、入力信号と混合されて、第1の混合出力を生成する。スレーブ分周器からの出力は、入力信号と混合されて、第2の混合出力を生成する。第2の混合出力は、第1の混合出力と同位相になるように強制される。 (もっと読む)

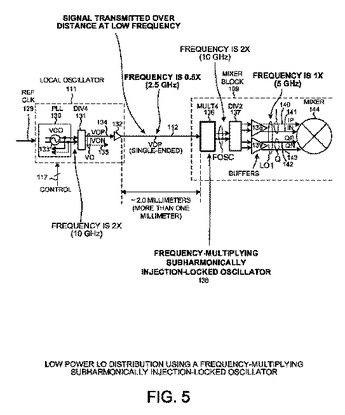

周波数逓倍サブハーモニック注入同期発振器を使用した低電力LO分配

局部発振器は、相対的に低い周波数の信号を、集積回路にわたりミキサの位置まで伝達する。ミキサの近くでは、周波数逓倍サブハーモニック注入同期発振器(SHILO)が、その信号を受信し、それからより高い周波数の信号を発生させる。SHILOがIおよびQ直交位相信号を出力する場合には、IおよびQ信号がミキサをドライブする。SHILOが直交位相信号を発生させない場合には、直交位相発生回路が、SHILO出力信号を受信し、それからミキサをドライブするIおよびQ信号を発生させる。1つの有利な態様において、局部発振器からSHILOまでの距離を越えて伝達される信号の周波数は、近くでミキサをドライブするIおよびQ信号の周波数よりも低い。距離を越えて伝達される信号の周波数を低くすることは、従来のシステムと比較すると、50パーセント以上、LO信号分配システムの電力消費を減じることができる。  (もっと読む)

(もっと読む)

クロック再生装置および電子機器

【課題】受信データ信号のエッジ位置変動が生じたとしても的確にエッジ検出を行うことが可能で、転送レートの高速化および低消費電力化を実現することが可能なクロック再生装置および電子機器を提供する。

【解決手段】ゲーティング信号生成部130Bは、位相判定部120Bの位相判定信号に応じて、エッジ検出部110の検出結果により立ち上がりエッジ検出を示す信号または立ち下がりエッジ検出を示す信号のいずれか一方の信号を第1のゲーティング信号として、他方の信号を受信データ信号の周期の半周期分を遅延させて上記第2のゲーティング信号として生成し、発振器140Bは、位相が第1のゲーティング信号SGT10および第2のゲーティング信号SGT11によって制御され、受信データ信号RDTに同期したクロック信号CLKを出力する。

(もっと読む)

クロックを並列データに整列させるための回路

【課題】クロック信号を並列データに整列させるための方法を提供する。

【解決手段】クロックシフティング回路10は、入来クロック信号8を入来データ信号16に対してシフトし、データクロッキング回路20は、シフト済みクロック信号を使用して、入来データ信号16を再クロックする。クロックシフティング回路10は、位相ロックループ回路2に直列に接続されている複数のDフリップフロップ回路4,6を連結して備える。データクロッキング回路20は、それぞれの入来データビット16を受信し、ミキサ22に対するローカルオシレータとして働く真−補数ブロック50,58を備える。複数のシフト済みクロック信号62,54,64,56は、入来クロック信号16に対して90度、180度、及び270度シフトされたものなど、が生み出される。

(もっと読む)

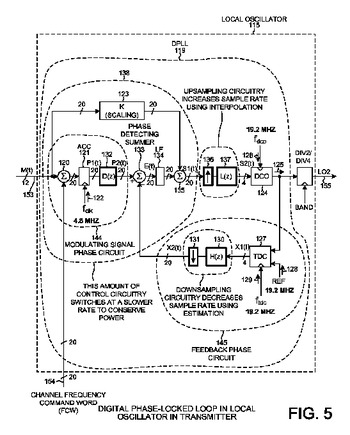

異なるサンプルレートで動作する部分を有するデジタル位相同期ループ

デジタル位相同期ループ(DPLL)は、DCO出力信号及び基準クロックを受信し及びデジタル値の第1のストリームを出力する時間−デジタル変換器(TDC)を含む。TDCを高レートでクロックすることによって量子化雑音が低減される。ダウンサンプリング回路は、第1のストリームを第2のストリームに変換する。第2のストリームは、DPLLの制御部が電力消費量を低減させるためにより低いレートで切り替わることができるようにDPLLの位相検出加算器に供給される。従って、DPLLは、マルチレートDPLLと呼ばれる。制御部によって出力されたデジタルチューニングワードの第3のストリームは、DCOをより高いレートでクロックし、それによってデジタルイメージを低減させることができるようにDCOに供給される前にアップサンプリングされる。受信機用途においては、アップサンプリングは行われず、DCOはより低いレートでクロックされ、それによって電力消費量をさらに低減させる。  (もっと読む)

(もっと読む)

時間デジタル変換器

【課題】時間遅延量の最適値制御が行える時間デジタル変換器を提供すること。

【解決手段】入力されるクロック信号を多段に遅延する複数の遅延段を有し、該複数の遅延段の少なくとも1つが可変遅延段である遅延回路と、前記遅延回路の遅延段と同数個設けられ、参照信号の入力に応答して並列に対応する遅延段の出力を取り込む複数のフリップフロップと、前記複数のフリップフロップの各出力の立ち上がりと立ち下がりの一方または両方を検出するエッジ検出回路と、前記エッジ検出回路が検出したエッジ数をカウントするカウンタ回路と、前記カウンタ回路がカウントしたエッジ数に応じて前記可変遅延段の遅延量を制御する制御回路とを備える。

(もっと読む)

PLL回路及び光ディスク装置

【課題】適切な動作モードとすることができなかった。

【解決手段】それぞれ位相が異なる複数の基準クロックを出力する多相基準クロック出力回路と、複数の基準クロックをそれぞれ所定の値で分周した複数の分周クロックを出力する多相分周回路と、複数の基準クロックのいずれか1つ、もしくは、複数の分周クロックのいずれか1つのうちのどちらかを選択し、その選択したクロックを選択クロックとして出力する選択スイッチ回路と、選択クロックを動作クロックとし、周波数制御入力データの値に応じて周波数が変動する出力クロックと、出力クロックと周波数制御入力データの値に応じて計算される理想位相との位相差を示す遅延量データとを出力するデジタルVCOと、遅延量データに応じて複数の分周クロックのうち1つに同期した出力クロックを選択して出力する選択回路と、を有するPLL回路。

(もっと読む)

デシリアライザ

【課題】PLL回路を用いずにクロックを同期させることを課題とする。

【解決手段】デシリアライザ部1は、PLL回路の代わりに、発振器2とクロック同期部10とを備える。クロック同期部10は、入力されたシリアルデータを段階的に遅延させることで異なる位相のデータを複数生成する。次に、クロック同期部10は、複数のシリアルデータそれぞれの位相と、発振器2によって発振されたクロックの位相とを比較する。そして、クロック同期部10は、比較結果に基づいて、発振器2によって発振されたクロックとの同期に適したシリアルデータを選択する。

(もっと読む)

信号周波数変更回路及びその周波数変更方法

【課題】デューティサイクルエラーを最小化し、消費電流を減少させる。

【解決手段】信号周波数変更回路は、クロック信号を遅延制御信号に相応する第1遅延時間だけ遅らせて遅延信号を生成し、前記クロック信号を前記第1遅延時間に比べて小さい第2遅延時間だけ遅らせて予備周波数変更クロック信号を生成する遅延線;位相固定完了信号を生成する検出部;前記位相固定完了信号の活性化時点の以前まで供給される前記クロック信号を利用して、前記遅延制御信号及び多重化制御信号を順次シフトさせる制御部;前記多重化制御信号に応じて、前記予備周波数変更クロック信号のうちから1つを選択して出力するマルチプレクサ;及び前記クロック信号と前記マルチプレクサの出力信号を利用して、前記クロック信号の周波数と異なるように変更された周波数を有する周波数変更クロック信号を生成する出力部を備える。

(もっと読む)

FM受信機におけるジャマー検出ベースの適応PLL帯域幅調整

FM受信機内の周波数シンセサイザは、フェーズロックドループ(PLL)を用いて、局部発振器(LO)信号を生成する。LO信号は、ミキサに提供される。FM受信機は、さらに、ジャマー検出機能性を含む。ジャマーが検出されなかった場合、PLLのループ帯域幅は、比較的高い値を有するように設定され、それによって、帯域内残留FMの抑制を促進する。ジャマーが検出された場合、PLLのループ帯域幅は、比較的低い値を有するように設定され、それによって、帯域外SSB位相雑音の抑制を促進する。ジャマーが検出されたか否かに依存してループ帯域幅を適応的に変更することによって、帯域内残留FMおよび帯域外SSB位相雑音要求を満たすと同時に、PLL内のサブ回路へのパフォーマンス要求を緩和することができる。PLLのVCOが、ループ帯域幅の適応的な変更による位相雑音をより多く生成できるようにすることによって、VCO電力消費を減らすことができる。 (もっと読む)

量子周波数標準器及び時刻制御システム

【課題】簡素な回路構成で低消費電力の量子周波数標準器。

【解決手段】化学結合している原子核間のスピン−スピン相互作用によって複数に分裂したエネルギー準位を有する物質110を含む容器120と、容器120に磁場を与える磁場発生源MGと、容器120に電磁波を照射する発振器150と、を含む核磁気共鳴部100と、核磁気共鳴部100から出力される共鳴信号RSからエネルギー準位の核磁気共鳴周波数f1を検出し第1検出信号SD1として出力する第1検出部200と、共鳴信号RSから隣り合うエネルギー準位間のエネルギー差であるスピン結合定数Jを検出し第2検出信号SD2として出力する第2検出部300と、第1検出信号SD1と第2検出信号SD2に基づき核磁気共鳴部100を駆動する駆動信号DSを生成する駆動信号生成部400と、を含み、第2検出部300は、第2検出信号SD2に基づき標準周波数信号SOを出力する。

(もっと読む)

半導体装置

【課題】リード動作時における位相調整精度を低下させることなく、DLL回路の消費電力を低減する。

【解決手段】ODT機能を有するデータ入出力回路80と、データ入出力回路80の動作タイミングを規定する内部クロックLCLKを生成するDLL回路100とを備える。DLL回路100は、内部クロックLCLKを高精度に位相制御する第1のモードと、低消費電力で動作する第2のモードとを有し、データ入出力回路80がODT動作を行っていない場合には第1のモードで動作し、データ入出力回路80がODT動作を行っている場合には第2のモードで動作する。このように、ODT動作の有無によってDLL回路100の動作モードを切り替えていることから、厳密な位相制御が不要なODT動作時における消費電力を低減することが可能となる。

(もっと読む)

発振器および位相同期ループ

【課題】発振器の位相雑音を低減し、位相同期ループの消費電力および位相雑音を低減する。

【解決手段】発振器は、共振回路の容量値に応じて発振周波数が可変する構成であって、外部から入力する外部クロックと設定データに応じて、オーバーフロー信号を間欠的に出力するアキュムレータ11と、オーバーフロー信号の間欠入力に応じてオン・オフするスイッチ12と、スイッチ12を介して共振回路に接続される固定容量値を有する容量素子C2とを備え、設定データに応じて間欠的に出力されるオーバーフロー信号の入力によりスイッチ12がオンとなるオン時間における発振周波数と、オーバーフロー信号が入力されないときにスイッチ12がオフとなるオフ時間における発振周波数との間で、オン時間とオフ時間の時間割合に応じた平均発振周波数を可変させる。

(もっと読む)

クロック位相調整回路

【課題】実装面積や消費電力を低減させることができるクロック位相調整回路を提供すること。

【解決手段】n個の第1の遅延素子15を多段に接続し、入力クロック信号INCLKをその周期の1/nずつ遅延させたクロック信号をそれぞれ出力するDLL回路2と、n個の第1の遅延素子15から出力されるクロック信号のうち1つのクロック信号を選択して出力する第1のセレクタ回路3と、この第1のセレクタ回路3から出力されるクロック信号CLK1を遅延させる遅延部4を備えている。遅延部4は、1又は複数の直列に接続された遅延回路20を有しており、この遅延回路20は、前段の遅延回路10に設けられた第1の遅延素子15の遅延量に対して1/2の遅延量を有する第2の遅延素子21と、入力されたクロック信号CLK1と第2の遅延素子21により遅延されたクロック信号のいずれかを選択して出力する第2のセレクタ回路22とを備える。

(もっと読む)

水晶発振器

【課題】実装スペースとコストの更なる低減のため、電子機器内の水晶部品を1つに集約するためには、消費電流や周波数精度の問題があった。

【解決手段】本発明の水晶発振器は、音叉型水晶振動体と、この振動体の温度による発振周波数の変化を、時間領域で連続的に補正するための温度補償回路を含んだ発振回路とを備え、この発振回路の出力を源振として高周波クロック信号を出力する、複数のPLL(フェイズロックループ)回路を備える。このような構成にすることにより、電子機器内で必要とされる全てのクロック信号を、精度良く提供することができる。

(もっと読む)

クロック分周回路、及びクロック分周方法

【課題】動作回路の通信タイミングを考慮すると共に、分周時に出力クロック信号の位相調整が可能なクロック分周回路、及びクロック分周方法を提供することである。

【解決手段】本発明にかかるクロック分周回路100は、入力クロック信号(クロックS)のクロックパルスと、通信タイミング信号26と、位相調整信号60に応じて生成されたリセット値81と、に基づき、入力クロック信号に対する通信タイミングの相対的な位相を示すカウント値55を生成し、カウント値55に基づき入力クロック信号のM個のクロックパルスのうち通信タイミング以外のクロックパルスに対してクロックパルスをマスクするマスク信号25を生成するマスク制御回路20を有する。更に、マスク信号25に応じて入力クロック信号のクロックパルスをマスクするマスク回路10を有する。

(もっと読む)

デジタルPLL回路及びデジタルPLL動作方法

【課題】CLVスピンドル制御のランダムシーク時でもスループット低下を抑え、かつ安価で消費電力を抑えたワイドキャプチャ対応のデジタルPLL回路を提供する。

【解決手段】本発明のデジタルPLL回路10Aは、周波数値fq’に応じてマスタクロックsclkの周波数を切り替えるマスタクロック切り替え手段10Bと、周波数値fq’に一定の倍率を乗じて数値制御発振器6へ出力するとともに、マスタクロックsclkの周波数が切り替わる前後で同期クロックgclkの周波数が一定になるように前記倍率を切り替える倍率切り替え手段10Cと、を備えたことを特徴とする。

(もっと読む)

61 - 80 / 216

[ Back to top ]