Fターム[5J106KK40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 省電力化 (216)

Fターム[5J106KK40]に分類される特許

201 - 216 / 216

位相同期ループ回路

【課題】 ループ利得の変動を抑圧できるループ利得検出回路を備えたPLL回路を提供する。

【解決手段】 PLL回路内の電圧発振器1で駆動されるカウンタ6と、その出力を周期的に積算するアキュームレータ(ACL)と、ACLのカウント値とレジスタ9に予め設定された設計値とを比較する比較演算回路部8を設け、ACLのカウント値がループ利得と反比例することを応用してPLL回路のループ利得を検出する。検出結果に基づいてチャージポンプ電流等でループ利得の補正を行ってループ利得を校正する。これにより、PLL回路は、PLLを構成する各素子の特性のばらつきに影響しない安定したループ特性を保つことができる。

(もっと読む)

複合回路

【課題】 電圧降下回路における電力損失を少なくすることが可能な複合回路を提供する。

【解決手段】 AC出力回路HS1とDC出力回路IC1とが電源電流の経路に対し直列に接続される。複合回路3に供給される電源電圧はAC出力回路HS1とDC出力回路IC1を並列接続する場合よりも高くなり、電圧降下回路2における電圧降下が小さくなる。よって電圧降下回路2における電力損失を小さくすることができる。高周波発振回路とDC出力回路との間に接続される高周波接地回路によって、AC出力回路とDC出力回路とが直列接続された場合でも高周波発振回路の基準電位は安定し、所望の高周波AC信号が得ることが可能になる。

(もっと読む)

周波数発生器

本発明による周波数発生器は、制御入力端および発振器出力端を備えた制御可能な発振器(16)であって、制御入力端における制御信号(SLOC)に依存する発振器周波数を持つ発振器信号(Sout)を発振器出力端で出力するように形成された制御可能な発振器(16)と、サンプル信号(Sd)を得るために、発振器信号(Sout)またはそこから取り出された制御可能な発振器(16)の信号を基準周波数でサンプリングするためのサンプリング手段(12)と、制御信号(SLOC)またはこの制御信号(SLOC)の基礎をなす信号(STP)を得るために、サンプル信号(Sd)またはそこから取り出された信号を低域ろ波するためのローパスフィルタ(14)とを含む。本発明によれば、集約の少ない構成、特に、分周器の不要と、現在発生されている周波数の迅速な調節機能とにより、電流を節約する周波数発生が得られる。  (もっと読む)

(もっと読む)

VCXOの起動時間を短縮するための方法と装置

無線端末(10)の所望の基準周波数を生成するための、低減された起動時間を有するVCXO(Voltage Controlled Crystal Oscillator)(100)のような電圧制御発振器(100)が本願明細書において記載されている。本発明によれば、VCXO(100)は、電圧コントローラ(110)によって発振器(120)に印加された可変電圧に基づいて、所望の基準周波数を生成する発振器(120)を含む。加えて、VCXO(100)は、発振器(120)に伴うキャパシタンスを低減するためバイアス電圧を発振器の入力ノードに印加し、VCXO(100)のDC電流消費または同調レンジに悪影響を与えること無く起動時間を低減する起動コントローラ(130)を含む。  (もっと読む)

(もっと読む)

遅延ロックループ回路

【課題】基準クロック信号/クロック信号間の位相を合致させるように位相制御の遅延ロックループ(DLL)回路で、回路規模縮小化、低消費電力化を図かった、電圧制御可変遅延線(VCDL)を使用するアナログDLL回路を提供

【解決手段】イニシャル信号入力により第1のクロック信号の初期位相設定を行う遅延ロックループ回路で、基準クロック信号位相と第1のクロック信号位相の比較結果に応じた信号を出力の位相比較器と、イニシャル信号入力時に位相比較器出力信号に応じた選択信号を発生の初期位相差検出器と、イニシャル信号入力時に初期位相差検出器からの選択信号で位相が異なる第2のクロック信号中の基準クロック信号に最近接位相の第2のクロックを選択し、第3のクロック信号として出力の初期位相差設定回路と、第3のクロック信号に位相比較器からの信号に応じた位相遅延を付加の第1のクロック信号を出力の電圧制御可変遅延線とを備える遅延ロックループ回路を提供。

(もっと読む)

チャージポンプ回路及びPLL回路

【課題】 PLL(Phase Locked Loop)のチャージポンプ回路でアイドルパスを間欠的に有効化することで省電力化を図る場合に、制御の誤動作の起こる可能性が高いロックイン過程において、アイドルパス制御の抑制を行うこと。

【解決手段】 PLLがロックされてロック検出器8の出力iが正論理の時に限り、アイドルパスの制御を行う。基準発振器1と周波数可変発振器2を分周するカウンタ9、10にパルス幅の制御回路11、12を付加し、ラスター信号cとローカル信号dのパルス幅をチャージポンプの電流源の起動に充分な長さに設定する。これら2信号とロック検出器8の反転出力の論理和をとることでアイドルパス有効化信号hを作る。

(もっと読む)

クォターレートクロック復元回路、及びクロック復元方法

【課題】 受信データレートの4分の1の周波数を有するクロックとして動作しかつ、四つの位相補間器を用いるクロックデータ復元回路を提供する。

【解決手段】 受信データレートの4分の1の周波数で0°、90°、180°および270°の位相差を有する第1クロック乃至第4クロックを生成するクロック生成部360と、制御信号に基づいて前記第1クロック乃至第4クロックを位相補間して受信データレートの4分の1の周波数で受信データの位相を追従する0°、45°、90°および135°の位相差を有する第5クロック乃至第8クロックを生成する位相補間部350と、受信データと前記第5クロック乃至第8クロックとの位相差に対応する信号を出力する位相検出部310と、位相検出部の出力信号を受信して位相補間部を制御するための制御信号を生成する位相補間部制御回路320とを含む。

(もっと読む)

通信用半導体集積回路および無線通信システム

受信用VCO(250)と送信用VCO(240a,240b)と中間周波数用VCO(230)のうち少なくとも1つのVCOが変復調回路と共に1つの半導体チップ上に形成された通信用半導体集積回路において、オンチップのVCOを複数の周波数帯で動作可能に構成し、また該VCOの発振周波数を測定する回路(22)および測定された値を記憶する記憶回路(18)と該記憶回路に記憶されている測定値と外部からの設定値とを比較して上記VCOの使用周波数帯を決定する回路(19)を設けるとともに、該記憶回路の記憶データを外部へ読出しまた外部から書き込むことができるように構成した。  (もっと読む)

(もっと読む)

周波数可変発振回路並びにそれを用いた位相同期回路及びクロック同期回路

【課題】低い電源電圧で動作し、かつ、高い周波数で発振することができる周波数可変発振回路並びにそれを用いた広い発振周波数範囲を有する位相同期回路及びクロック同期回路を提供すること。

【解決手段】pMOS及びnMOSトランジスタのゲートを相互に接続して入力端子とし、かつ、ドレインを相互に接続して出力端子とした相補型増幅回路を用いて差動増幅回路及び入出力端子を互いに交叉して接続した正帰還回路を構成し、差動増幅回路の出力端子間に正帰還回路を接続し、前記相補型増幅回路のソース電流を制御するための周波数制御信号をゲートに入力するMOSトランジスタと前記相補型増幅回路とを電源端子と接地端子の間に直列に接続して構成した遅延回路を環状に縦続接続して周波数可変発振回路を構成する。

(もっと読む)

クロック同期回路におけるクロック捕捉

クロック捕捉同期回路は、まず基準クロック信号から同期クロック信号を生成し、そして同期クロック信号を捕捉し、基準クロック信号が除かれた後も同期クロック信号を出力し続ける。クロック捕捉同期回路はまた、同期クロック信号の入力依存ジッタを低減する。本発明により、基準クロック信号が除かれた後、同期クロック信号を出力し続けるクロック同期回路が提供される。また、本発明により、同期クロック出力信号の入力依存ジッタをもし除去しないとしても低減はするクロック同期回路が提供される。  (もっと読む)

(もっと読む)

温度安定化された電圧制御発振器

セルラー電話のような電池から電力を得る装置中の集積回路電圧制御発振器(VCO)は、比較的狭い制御電圧範囲を使用して非常に広い周波数範囲にわたって同調するように構成されることができる。VCOの周波数応答は、VCO共振回路の一部を形成するバラクタ310a-310bに温度可変電圧ソースを与えることにより温度補償されることができる。バラクタのレファレンス端部は、バラクタ温度依存性を実質的に補償する温度依存性を有する温度依存電圧ソース370、380により供給されることができる。温度依存電圧ソース370,380は、絶対温度比例(PTAT)装置であることができる。VCOは、基板上に製造されたCMOS発振器、基板上のLC共振タンク、および共通の陽極接続を有する少なくとも一対のバラクタ310a、310b;320a、320bを含んでいる。 (もっと読む)

スイッチトキャパシタフィルタ及びフィードバックシステム

ループフィルタ(30)は、電流信号の入力端と基準電圧との間に設けられた第1の容量素子(31)と、上記入力端と第1の容量素子(31)との間に設けられたスイッチトキャパシタ回路(32)と、第1の容量素子(31)及び前記スイッチトキャパシタ回路(32)に並列に設けられた第2の容量素子(33)とを備えている。スイッチトキャパシタ回路(32)において、第3の容量素子(321)が第1の容量素子(31)側に接続されるとき、第4の容量素子(322)は第2の容量素子(33)側に接続される。上記構成のループフィルタ(30)において、第2の容量素子(33)の容量値を、第3及び第4の容量素子(321,322)の容量値よりも大きく設定する。 (もっと読む)

基準発振器の周波数安定化

従来技術の不利な点を取り除き、特性(1)高い長期安定性、(2)低位相雑音、(3)高耐熱性、(4)その基準発振器の周波数についての正確な値、を改善したMEMS基準発振器を提供することが、本発明の目的である。  (もっと読む)

(もっと読む)

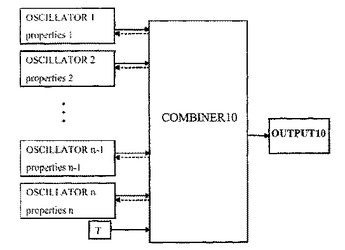

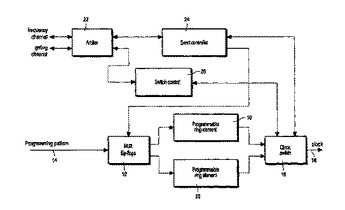

プログラマブルで一時停止可能なクロック発生ユニット

互いに排他的に動作するように配置構成された2つのプログラマブル・リング発振器(10、20)と、プログラマブル可変遅延要素(図示せず)とを含むクロック発生回路。入力プログラミング・パターン(14)が発振回路に入力として供給され、プログラミング・パターン(14)は、クロック信号を発生させる必要のある周波数のシーケンスを表すデータを提供する。2つの発振器(10、20)の出力端がクロック・スイッチ(16)に接続され、発生されたクロック信号(18)がこのスイッチから出力される。周波数変更を求める要求が受け取られたときは、まず現在アイドル状態の発振器(20)が必要とされる次の周波数で活性化され、次いで現在動作中の発振器(10)の出力が、そのクロック信号がローのときに、ゲート制御されるようになる。次に、前にゲート制御されていた発振器(20)の出力が、その出力がローのときに、ゲート制御されないようにされ、次いで発振器(10)が非活性化される。  (もっと読む)

(もっと読む)

バイアス電流補償回路を有するタイミング発生器及び方法

カレントミラーと共に使用するための電流補償回路が開示される。カレントミラー回路は、第2カレントミラー段を駆動する第1カレントミラー段によって規定される電流経路を有し、第2カレントミラー段は、供給電圧源に結合している。電流補償回路は、供給電圧及び出力ノードに結合するインピーダンス分割器を備える。インピーダンス分割器は、供給電圧源の電圧変化を表す、ノードにおける補償信号を生成するように動作する。補償回路はさらに、出力ノードに結合する入力及び電流経路に接続される電流出力を有する利得段を含む。利得段は補償信号に応答して電流経路に印加するための補償電流を生成するように動作する。  (もっと読む)

(もっと読む)

発振器の操向するための方法、及び発振器

本発明の目的は、周波数発振器を作ること、すなわち、外部外乱にも関わらず信頼性高く機能し、かつそれ専用の周波数を維持するために容易な制御を有するであろう水晶発振器をより正確に作ることである。この目的は、周波数発振器として、その出力周波数よりずっと低い範囲を持つ水晶発振器、或いは相当する機械共振器を選択することにより達され、その周波数は典型的には100kHz以下である。このような発振器は、サイズが小さく、製造するのが容易であり、それはまた、外部外乱にも関わらず、それ専用の周波数を非常によく維持する能力を持つ。その小さいサイズのおかげで、その発振器の消費電力は小さく、これは、例えばブルートゥース応用例において重要である。  (もっと読む)

(もっと読む)

201 - 216 / 216

[ Back to top ]