Fターム[5J106KK40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 省電力化 (216)

Fターム[5J106KK40]に分類される特許

121 - 140 / 216

TDD方式の通信装置及びその動作方法

本発明はクロック及びデータ復元(CDR)回路を用いてTDD方式の通信装置の送信及び受信時の動作クロック信号を提供することによって、クリスタルオシレータなしで動作安定化を具現し、電力消耗量を減少させることができるTDD方式の通信装置及びその動作方法に関する。送信時間間隔では前記CDR回路から発生した基準周波数のクロック信号を用いて送信フレームの処理を行い、受信時間間隔では前記CDR回路により受信フレームから復元されたクロック信号によって前記受信フレームを処理するように具現される。  (もっと読む)

(もっと読む)

電圧制御発振回路

【課題】発振周波数を上昇させた場合であっても、電圧制御発振回路のコンデンサの充放電電流の増加を抑制する。

【解決手段】コンデンサの充電電圧を入力電圧に応じた周波数で発振させる電圧制御発振回路であって、コンデンサの充電電圧の最低電圧が第1電圧、充電電圧の最高電圧が第1電圧より高い第2電圧となるよう、コンデンサを繰り返し充放電する充放電回路と、入力電圧に応じて第1電圧と第2電圧との差を制御する制御回路と、を備える。

(もっと読む)

周波数シンセサイザ

【課題】 低いジッター成分を持つ周波数シンセサイザと電力消耗が最小化された周波数シンセサイザを提供することを課題とする。

【解決手段】基準信号と比較信号が入力されて周波数と位相の差を検出し、これによって、アップ信号、又はダウン信号を発生させる位相比較器と、前記アップ信号又はダウン信号によって、電圧を充電又は放電して制御信号を出力する電荷ポンピング回路と、前記ポンピング回路より出力される制御信号によって、周波数を持つ信号を発振出力信号と出力する電圧制御発振器と、前記電圧制御発振器と連結されて、デューティサイクルを補正するデューティサイクル補正回路と、及び前記発振出力信号の周波数を分割して、前記位相比較器に前記比較信号を提供するフィードバッグディバイダーが含まれる。

(もっと読む)

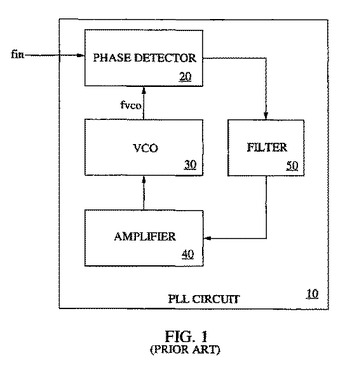

低消費電力装置を有するタイヤ圧検出器

タイヤ圧検出器は、集積回路に外付けされるように構成されるパワーアンプと、入力データストリームの論理状態に応じて動作するVCOを有するPLL回路とを備える低消費電力装置を用いる。入力データストリームは、タイヤ圧力情報を有し、複数の論理状態を有するようにエンコードされるように構成される。入力データストリームの各データビットのパターンに応じて、所定の期間、VCO及び/又はアンプをターンオン及びターンオフすると、マイクロコントローラがVCOを制御するために用いられる。このタイヤ圧検出器は、電力効率に関して最適化された回路配置をこのようにして具現化する。  (もっと読む)

(もっと読む)

半導体集積回路装置

【課題】本発明は、複数の回路モジュールにクロック信号を供給する際に、クロック信号配線における信号がトグルすることによる消費電力を削減することを特徴とする。

【解決手段】クロックジェネレータ20と、複数の回路モジュール111〜11nと、1つの回路モジュール11nにクロックジェネレータ20で発生されたクロック信号CLKnを供給するクロック信号配線41と、回路モジュール11n以外の回路モジュールに接続された電圧制御発振器311、312、313、…と、クロックジェネレータ20で発生された直流電圧を任意に分圧して、もしくは分圧せずに電圧制御発振器311、312、313、…に供給する複数の配線42を具備し、回路モジュール11nに供給されたクロック信号CLKnがクロックジェネレータ20に帰還クロック信号RetCLKとして帰還される。

(もっと読む)

PLLとその駆動方法

【課題】ロックタイムを短縮することができ、ロック動作において電力を効率的に消費することができるPLL(Phase Locked Loop)を提供すること。

【解決手段】基準クロックとフィードバッククロックとの位相差を検出し、それに対応する検出信号を生成する位相検出手段と、前記検出信号に対応する電圧レベルを有する制御電圧を生成する制御電圧生成手段と、該制御電圧のレベルに対応する周波数を有する内部クロックを生成する電圧制御発振手段と、前記基準クロックの周波数に対応するスタートアップレベル多重化信号に応答して、前記電圧制御発振手段の起動前に制御電圧端を所定のスタートアップレベルに駆動するスタートアップ駆動手段とを備えるPLLを提供する。

(もっと読む)

信号処理装置

【課題】変調信号の復調を実行する際の消費電力を低減し、かつ実装コストを抑制することが可能な信号処理装置を提供する。

【解決手段】本発明に係る信号処理装置は、互いにほぼ直交する第1及び第2のリファレンス信号を生成する発振器と、搬送波周波数からベースバンド周波数に変換された変調信号の同相成分を示す第1信号と当該変調信号の直交成分を示す第2信号を入力する入力部と、第1信号と第1リファレンス信号の位相比較を行って、比較結果に応じた位相差を示す第1位相差信号を出力する第1位相比較器と、第2信号と第2リファレンス信号の位相比較を行って、比較結果に応じた位相差を示す第2位相差信号を出力する第2位相比較器と、第2位相差信号から第1位相差信号を減算し、合成位相差信号を出力する合成部を備え、合成部から出力された信号を復調信号として出力すると共に、発信器への入力として用いる。

(もっと読む)

電圧制御発振器を内蔵したPLL(PhaseLockedLoop)回路の位相差検出回路

【課題】低電圧動作時においても、VCO信号と基準信号との位相差を検知し、その位相差に対応したデジタル信号を生成する位相比較器を提供する。

【解決手段】基準信号と対象信号との位相差をデジタル信号として出力する位相比較器において、前記位相差に対応したパルス幅の信号により第1容量素子を充電することによって前記位相差を電荷として検出する第1検出手段と、前記基準信号の周期に対応したパルス幅の信号により第2容量素子を充電することによって基準となる時間差を基準電荷として検出する第2検出手段と、前記第1検出手段により検出された電荷と前記第2検出手段により検出された電荷とを比較する電荷比較手段と、前記電荷比較手段による比較結果により、前記第2容量素子に充電された電荷に対する前記第1容量素子に充電された電荷の比をデジタル信号として出力する出力手段と、を備える。

(もっと読む)

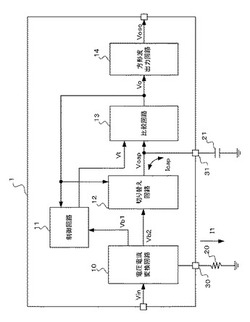

PLL回路

【課題】エクステンダ部の動作遅延時間を短縮して、分周比切り替え動作の誤動作に対するマージン時間を十分に確保し得るプリスケーラを提供する。

【解決手段】プリスケーラ21bは、分周比切り替え信号に基づいて、分周比を切り替えながら入力信号fvcoを分周する分周切り替え部Cと、分周切り替え部の出力信号を所定の分周比で分周するエクステンダ部Eとを備える。分周切り替え部Cは複数段のフリップフロップFF1〜FF3を有し、エクステンダ部Eの少なくとも一部を同期型カウンタで構成するとともに、少なくとも一部を非同期型カウンタで構成する。

(もっと読む)

パルス無線受信装置および同期方法

【課題】NRZ符号化されたパルス信号に対しても同期可能であり、かつ従来のEarly/Late DLL方式に比べフィンガー数を削減したパルス無線受信装置および同期方法を提供する。

【解決手段】相対差算出手段1505は、最大値検出手段1551A、1551Bと最小値検出手段1552A、1552Bおよび加算手段1553A、1553B、1554を備える。最大値検出手段1551Aは、サンプル手段1504から入力される連続したn個のサンプル値1504Aから最大値を検出し最大値Amaxを出力する。同期制御手段1506は、相対差算出手段1505からの相対振幅差信号iVをもとに包絡線信号とク

ロック信号のタイミングが同期するように、クロック信号の位相を制御する遅延制御信号を生成し、遅延手段1503へ出力する。

(もっと読む)

多相クロック生成回路およびシリアルデータ受信回路

【課題】位相比較時のオフセットを少なくして高精度で高分解能の等位相多相クロックが生成されるとともに、小回路規模化および低消費電力化が図れる多相クロック生成回路およびシリアルデータ受信回路を提供する。

【解決手段】複数の電圧制御遅延回路2a〜2jを直列接続し、初段の電圧制御遅延回路2aの差動出力から生成される信号F00と、最終段の前段の電圧制御遅延回路2iの差動出力から生成される信号F88Aの逆相の信号であるF00Aとを、位相比較器3で比較し、比較結果をチャージポンプ4、ローパスフィルタ5を経由してバイアス回路から出力する制御電圧信号Pnct,Ncntで信号F00とF00Aとの位相差が無くなるように電圧制御遅延回路2a〜2jの遅延を調整し、電圧制御遅延回路2a〜2jの各差動出力信号からクロック生成部7でシングル信号に変換して等位相の多相クロックを生成する。

(もっと読む)

省電力のクロッキング技術

【課題】電力消費が低減したクロック信号を提供するための方法及びシステムを提供すること。

【解決手段】ハイブリッド・クロック・システムと呼ばれる、電力消費が減少したクロック信号を提供するための方法及びシステムが提供される。ハイブリッド・クロック・システムは、高速データ転送のためにPLLを用いるが、より少ない電力を消費しながらデータを転送するための省電力モードを提供する。通常モードにおいて、ハイブリッド・クロック・システムは、PLLを駆動する、低周波数で動作する基準クロックを含む。PLLは、基準クロックの周波数をずっと高い周波数に逓倍し、基準クロックを直接データ転送回路に与える。省電力モードにおいて、ハイブリッド・クロック・システムは、PLLをオフにし、基準クロックを直接データ転送回路に接続する。

(もっと読む)

半導体装置

【課題】半導体制御装置において、供給先別にクロックの位相を制御し、且つクロック供給の供給先別優先順位を制御することによって、動作時の電源電圧変動を抑えこれにより動作時の消費電力を抑える。

【解決手段】機能により複数に分割された機能モジュールと、上記機能モジュールの夫々に供給されるクロック信号を生成するクロック発振回路と、外部から入力される上記機能モジュールの夫々に対するクロック供給イネーブル信号に従って、上記クロック発振回路の生成するクロック信号を上記機能モジュールの夫々に供給するクロック制御回路を含む半導体装置を提供する。

(もっと読む)

PLL回路

【課題】従来のPLL回路は、回路規模と消費電力とが大きい問題があった。

【解決手段】本発明にかかるPLL回路は、それぞれ位相が異なる複数の基準クロックを出力する多相基準クロック出力回路10と、複数の基準クロックのいずれか1つを動作クロックとし、周波数制御入力の値に応じて周波数が変動する出力クロックと、前記周波数制御入力の値に応じて計算される理想位相と出力クロックの位相との位相差を示す遅延量データとを出力するデジタルVCO20と、遅延量データに応じて複数の基準クロックの1つに同期した出力クロックを選択して出力する選択回路30と、を有するものである。

(もっと読む)

PLL回路

【課題】低電源電圧で高速動作すると共に温度及びプロセス条件の変動の影響を受けにくいPLL回路を提供する。

【解決手段】位相比較器101は、入力される基準クロック信号及び帰還される発振信号の位相を相互に比較した結果に基づいて上昇信号または下降信号を出力する。チャージポンプ102は、入力される信号に応じた大きさの制御電圧を出力する。ループフィルタ103は、入力される制御電圧をフィルタリングする。電圧制御発振器100は、負電圧発生回路105から基準電圧として入力される接地電圧よりも低い電圧と、ループフィルタ103から出力される電圧とに応じた発振周波数の発振信号を出力する。

(もっと読む)

PLL回路、およびそれを備えた無線装置

【課題】低消費電力で、広い発振周波数範囲に対応したPLL回路を提供する。

【解決手段】電圧制御発振器10と、電圧制御発振器10の発振信号を分周し発振分周信号を出力する分周器30と、分周器30の発振分周信号と基準信号の位相差を出力する第1の位相比較器40と、第1の位相比較器40の出力信号を電圧制御発振器10の制御用信号に変換するチャージポンプ60と、チャージポンプ60の出力信号のうちDC成分を通過させ、電圧制御発振器10に電圧を出力するフィルタと、分周器30の発振分周信号と基準信号との位相差を時間平均する第2の位相比較器90と、第2の位相比較器90において時間平均された位相差に基づいて、分周器10の動作電流を制御する電流制御回路100とを備えたものである。

(もっと読む)

DLL回路及びその制御方法

【課題】本発明は、より向上したデューティ比特性を持つクロックを出力するDLL回路及びその制御方法を提供する。

【解決手段】本発明のDLL回路は、立ち上りクロックのデューティ比及び立ち下りクロックのデューティ比を感知して、デューティ比感知信号を出力するデューティ比感知ユニットと、デューティ比感知信号に応じて、補正制御信号を生成する補正制御ユニットと、補正制御信号に応じて、内部クロックのデューティ比を補正し、基準クロックを出力するデューティ比補正ユニットとを含むことを特徴とする。

(もっと読む)

自動周波数制御回路

【課題】 自動周波数制御回路における検出部の起動および停止を簡単に制御し、消費電力を低減する。

【解決手段】 受信パケットから送信装置と受信装置との間のクロック周波数の誤差を検出し、その周波数誤差に対する補正値を出力する検出部と、検出部から出力された補正値に基づいて受信パケットの周波数誤差を補正する補正部とを備えた自動周波数制御回路において、検出部とは別のアルゴリズムで、受信パケットの周波数誤差の有無を簡易に判定し、周波数誤差があれば検出部を動作させ、周波数誤差がなければ検出部の動作を停止させ、検出部の動作時に出力した補正値を受信パケットの周波数誤差の補正に用いる制御を行う簡易判定部を備える。

(もっと読む)

PLLシンセサイザ

【課題】 高速起動性、低消費電力性、定常状態における低スプリアス性を同時に満足し、かつ性能を左右するパラメータを最適化する。

【解決手段】 分数分周モードと整数分周モードとを切り換える構成であり、PLL起動時から収束に至るまでの収束時間Tacq を設定し、その収束時間Tacq が、制動係数ζ、固有周波数ωn 、初期周波数差Ω0 に対して、

Tacq =Ω02/(2ζωn3) …(a)

で表されるときに、制動係数ζを0.5 ≦ζ≦1とし、PLL起動時に固有周波数ωn が (a)式を満たすように分数分周モードの分周比を設定し、収束したと見なすタイミングTs(=Tacq)で、ループフィルタを切り換えることなく、整数分周モードの分周比に切り換える構成である。

(もっと読む)

撮像装置

【課題】サンプルホールドタイミングを高精度に決定しながらも消費電力を抑えることが可能な撮像装置を提供する。

【解決手段】撮像素子と、撮像素子から出力される撮像信号OSに相関二重サンプリング処理等を行うAFEとを有するデジタルカメラであって、DLL回路40と、AFEを制御するための制御信号(サンプルホールドタイミングパルスshp)をDLL回路40から出力されるクロックpulseに基づいて生成するパルス発生回路と、ブランキング期間中、DLL回路40を、そのロック状態を維持させたまま停止させる制御を行うDLL制御部51とを備える。

(もっと読む)

121 - 140 / 216

[ Back to top ]