Fターム[5J106KK40]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 目的、効果 (3,441) | 省電力化 (216)

Fターム[5J106KK40]に分類される特許

101 - 120 / 216

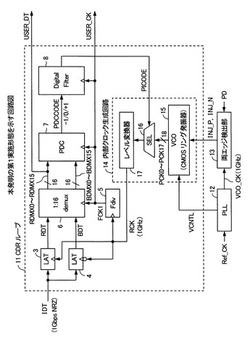

クロック及びデータ復元回路

【課題】入力データ論理判定用クロックとして、周波数の安定したクロックを得ることができ、しかも、消費電力を低減することができるCDR回路を提供する。

【解決手段】入力データの論理判定に使用する内部クロックRCKの発生源として電圧制御発振器15を設ける。電圧制御発振器15は、CMOSインバータをリング接続して構成し、常に電流を消費することがないものとする。両エッジ検出部13は、PLL12内の電圧制御発振器21の出力クロックVCO_CKの遷移タイミングを検出し、電圧制御発振器15の発振周波数がPLL12内の電圧制御発振器21の発振周波数と同一となるように電圧制御発振器15を制御する。

(もっと読む)

発振回路、発振回路を備えた電子機器及び発振回路の制御方法

【課題】高精度発振器間の位相同期を間欠動作にすることにより低消費電力化する。

【解決手段】基準となる周波数の基準信号Frefを出力する周波数確度が高い高精度発振器100と、出力信号Foutの周波数を制御電圧Vcで制御する電圧制御発振器110と、基準信号Frefの位相と出力信号Foutの位相との位相差を検出し位相差信号Poを出力する位相比較部120と、位相差信号Poに基づき制御電圧Vcを生成する制御電圧生成部130と、位相比較部120への電源VDDの接続を接続状態または非接続状態に切り替えるスイッチ回路140と、位相差信号Poに基づき位相差が無くなった時点から所定の時間が経過するまでの期間はスイッチ回路140を接続状態にし、期間以外はスイッチ回路140を非接続状態にする制御信号Swを出力するタイマ回路150と、を含む発振回路1。

(もっと読む)

デジタル位相ロックループ(DPLL)における電力消費を制御するシステム及び方法

【解決手段】相異なる周波数クロックの組から選択された参照クロックを生成するように適合されたプログラマブル周波数デバイスを備えた装置であって、プログラマブル周波数デバイスは更に、相異なる周波数クロック間での切り替えの際に、参照クロックのトリガエッジの同じ時間的関係を維持するように適合される。装置は更に、入力信号と出力信号との間の所定の位相関係を確立するために選択された参照クロックを使用する、デジタルPLL(DPLL)のような位相ロックループを備える。相異なる周波数クロック間の切り替えの際に参照信号の同じ時間的関係を実質的に維持することで、参照クロックが変化しても、位相ロックループ(PLL)の連続且つ有効な動作は、大きくはディスターブされない。これは、装置の電力消費を制御するために使用され得る。 (もっと読む)

位相補間器及びクロックデータリカバリ装置

【課題】本発明は、ミキサの数を減らすことで回路面積及び消費電力を縮小し、位相の不整合を抑制することが可能な位相補間器を提供する。

【解決手段】位相差が0度のクロックD0を与えられミキサ2個分の遅延量を有するクロックD0+2Dcを出力する2ミキサM11、M12、位相差が0度のクロックD0と位相差が90度のクロックD90とを与えられ位相差が45度の遅延量とミキサ2個分の遅延量とを有するクロックD90+2Dcを出力するミキサM1、M13、クロックD0、D90、D45+2Dcのいずれか2つを用いて位相差が所定角度の遅延量とミキサ2個分の遅延量とを有するクロックを生成して出力する少なくとも1つのミキサを備える。

(もっと読む)

チャージポンプ回路およびPLL回路

【課題】消費電流を低減しつつ、出力のオーバーシュートを抑制することが可能なチャージポンプ回路を提供する。

【解決手段】チャージポンプ回路は、入出力端子を充電する場合は、第1のスイッチ素子、第4のスイッチ素子、および第5のスイッチ素子をオンするとともに、第2のスイッチ素子、第3のスイッチ素子、および第6のスイッチ素子をオフし、入出力端子を放電する場合は、第1のスイッチ素子、第4のスイッチ素子、および第5のスイッチ素子をオフするとともに、第2のスイッチ素子、第3のスイッチ素子、および第6のスイッチ素子をオンし、入出力端子を充放電しない場合は、第1のスイッチ素子、第2のスイッチ素子、第5のスイッチ素子、および第6のスイッチ素子をオフするとともに、第3のスイッチ素子、および第4のスイッチ素子をオンする。

(もっと読む)

原子発振器

【課題】光強度を小さくしてEIT信号の半値全幅を小さくしてQ値を高めると共に、S/N比を高めて、高精度で低消費電力の原子発振器を提供する。

【解決手段】各共鳴光を出射するLD53と、金属原子ガス中に各共鳴光を通過させる共鳴ガスセル58と、透過光1を検出するPD55と、受光電流に含まれる差周波ビート成分を検出するビート成分検出手段2と、ビート成分検出手段2により検出された差周波ビート成分の振幅レベルを検波する検波手段3と、検波手段3の検波出力に基づいて水晶発振器60の制御電圧を生成する周波数制御手段59と、周波数制御手段59から生成された制御電圧に基づいて規定の周波数を発振する水晶発振器60と、水晶発振器60の発振周波数を基に合成・逓倍して生成した変調周波数ωmによりLD(コヒーレント光源)53のDC電流を変調する変調手段61と、を備えて構成されている。

(もっと読む)

誘導結合通信におけるインダクタンス補償方法及び装置

【課題】

本発明は、誘導結合(inductive coupling)送受信装置に関する。

【解決手段】

本発明の一実施例による誘導結合送受信装置は、データを送信及び/又は受信する誘導結合送受信器と、前記誘導結合送受信器に接続されたインダクタ(inductor)と、前記誘導結合送受信器及び前記インダクタに接続されて前記インダクタのインダクタンス(inductance)変化を補償する共振補償装置を含む。

(もっと読む)

起動制御回路付き水晶発振回路および位相同期回路

【課題】 水晶発振回路が定常発振に達するまでの起動時間を短くすることができる起動制御回路付き水晶発振回路、水晶発振回路の起動時間を短くすることで間欠動作の比率を大きくし、低消費電力化に寄与する位相同期回路を実現する。

る。

【解決手段】 水晶振動子と負性抵抗回路を備えた水晶発振回路の起動制御を行う起動制御回路を含み、一定の発振周波数の信号を出力させる起動制御回路付き水晶発振回路であって、水晶発振回路は、水晶振動子を励振する励振信号を外部から入力するための信号入力端子を備え、起動制御回路は、発振周波数またはそれに近い周波数を有する励振信号を生成し、水晶発振回路の起動時に励振信号を励振信号入力端子に入力し、水晶発振回路の発振周波数が安定する前に励振信号の入力を停止する構成である。

(もっと読む)

周波数および電圧制御回路、電子機器およびネットワーク装置

【課題】PLL回路を搭載する電子機器を低消費電力で運用するモードに切替えるとき、または、高速処理可能な運用モードに切替えるとき、一度回路の処理を止めてから、クロック周波数、電源電圧、MOSFETの閾値電圧を切替える必要があった。また切替えにそれぞれ別の制御回路、手法が必要であった。

【解決手段】PLL回路のループフィルタが出力する電圧値に連動させて電源電圧および、MOSFETの閾値電圧を切替えることによって、クロック周波数を変える動作をさせるだけで、被制御回路の電源電圧およびMOSFETの閾値電圧も切替える。また、PLL回路の応答特性を単調増加もしくは単調減少で緩やかな変化にすることで、回路の動作を止めずにモードが切替えを可能とする。

(もっと読む)

原子共振器を使用した周波数発生のためのデバイス、システム、および方法

固体原子クロックは、周波数標準を生成するために、超微細共振を示すことが可能な量子状態を利用する可能性がある。出力信号を生成するために自由走行発振器を超微細共振周波数に結合することが可能なデバイスが本明細書で述べられる。本発明のある態様では、原子クロックは、シリコン基材上で作製されてもよく、また、電子集積回路の一部として、チップスケールで集積化されてもよい。固体原子クロックを利用した動作原理、作製方法、およびシステムもまた開示される。 (もっと読む)

DLL回路およびその制御方法

【課題】より向上したデューティー比特性を有するクロックを生成し、半導体集積回路の動作をより安定的に支援するDLL回路およびその制御方法を提供する。

【解決手段】本発明のDLL回路は、基準クロックを所定の分周比で分周して分周クロックを生成するクロック分周手段;前記分周クロックに対する遅延固定動作を行って遅延クロックを生成するフィードバックループ;前記遅延クロックを前記基準クロックの半周期だけ遅延させて半周期遅延クロックを生成する半周期遅延手段;および前記遅延クロックと前記半周期遅延クロックを組み合わせ演算して出力クロックを生成する演算手段;を含むことを特徴とする。

(もっと読む)

信号発生回路

【課題】広帯域の信号を発生させる場合において、消費電力を低減することが可能な信号発生回路を提供することを目的とする。

【解決手段】基準信号aを出力する基準信号源51と、基準信号aと出力信号cとの位相差に対応する電圧を出力する位相比較器53と、位相比較器53から出力される電圧に基づく発振信号bを出力する電圧制御発振器55と、発振信号bを分周して出力信号cを出力する分周回路3と、ロック検出器56と、基準信号aと出力信号cとの位相差がゼロであることを示すフラグ信号fがロック検出器56から出力されている間、分周回路3に流れる電流を所定量ずつ下げ続け、その後、ロック検出器56からフラグ信号fが出力されなくなると、分周回路3に流れる電流を少なくとも上記所定量上げて再度上記位相差をゼロにさせる制御回路2とを備えて信号発生回路1を構成する。

(もっと読む)

ゲート時間/デジタル変換器を有するデジタル位相ロックドループ

デジタルPLL(DPLL)、時間/デジタル変換器(TDC)および制御ユニットを含む。TDCは、位相情報を量子化するために、短い時間の間、周期的に有効され、電力消費を削減するために、残り時間の間、無効にされる。TDCは、第1のクロック信号と第1の基準信号を受信し、第1のクロック信号と第1の基準信号との位相差を示す出力をTDCに提供する。制御ユニットは、主基準信号に基づいてイネーブル信号を生成し、イネーブル信号でTDCを有効および無効にする。ある設計において、制御ユニットは、第1の基準信号および第2の基準信号を獲得するために、主基準信号を遅らせ、主基準信号および第2の基準信号に基づいてイネーブル信号を生成し、TDCに対する第1のクロック信号を獲得するために、イネーブル信号で主クロック信号をゲートする。 (もっと読む)

半導体装置

【課題】発振信号を出力し、かつ低消費電力化を図ることが可能な半導体装置を提供する。

【解決手段】半導体装置101は、第1の制御電圧に応じた周波数で発振することにより発振信号を出力する電圧制御発振回路5と、電圧制御発振回路5から受けた発振信号の周波数を電圧に変換する周波数/電圧変換回路2と、周波数/電圧変換回路2によって変換された電圧と前回生成した第2の制御電圧との間のレベルを有する新たな第2の制御電圧を生成する制御電圧生成回路11と、第2の制御電圧を積分することにより第1の制御電圧を生成し、第1の制御電圧を電圧制御発振回路5へ出力するアナログ積分回路3とを備える。

(もっと読む)

局所発振回路

【課題】消費電力を低減できる局所発振回路を提供する。

【解決手段】周波数fsの基準振動信号と周波数fout/(m×n)の分周信号の位相を比較する位相比較器1と、上記両信号の位相のずれに応じた電流IOUTを出力する電荷ポンプ10と、上記出力電流IOUTに応じた制御電圧VCを生成するループフィルタ3と、上記制御電圧VCに応じた発振周波数foutの信号を出力する電圧制御発振器4と、電圧制御発振器4の出力信号を設定周波数に応じた分周値(m×n)で分周して上記分周信号を出力する前置分周器5および可変カウンタ6とを備え、上記発振周波数foutを上記設定周波数に引き込む局所発振回路において、上記電荷ポンプ10は、出力電流IOUTの値を上記設定周波数に応じて切り換える。

(もっと読む)

位相ロック・ループにおけるVCOの動的バイアス印加

局部発振器が位相ロック・ループを含む。前記位相ロック・ループは電圧制御発振器(VCO)と新規のVCO制御回路を含む。前記VCO制御回路はプログラム可能で設定可能であることが出来る。1つの例では、前記VCOの電力状態を変更するために、命令が前記VCO制御回路に受信される。前記命令は、セルラー電話における無線チャネル状態の検出された変化(例えば、信号対雑音判定の変化)に応答して、他の回路によって発せられる。応答して、前記VCO制御回路は、前記PLLのループ帯域幅を徐々に拡大し、次に該VCOバイアス電流を徐々に変更して該VCO電力状態を変更し、そして次に前記PLLのループ帯域幅を縮小して元の帯域幅に戻す、制御信号を出力する。PLL帯域幅を拡大すること、VCO電力状態を変更すること、及びPLL帯域幅を縮小すること、の全過程は前期PLLがロックされたままで行われる。  (もっと読む)

(もっと読む)

半導体装置

【課題】 シリアルデータの高速化にともなう受信性能の低下および連続同符合データ受信によるクロックデータリカバリー回路の精度低下を防止し、尚且つ消費電力の低いクロックデータリカバリー回路を提供する。

【解決手段】 シリアルデータを受信するSerDes回路101と、並走クロック信号を受信する参照SerDes回路102とを有し、SerDes回路101は、参照SerDes回路102の生成した位相制御信号P_CSを用いて位相制御された再生クロックにより受信したシリアルデータの直列並列変換を行う。

(もっと読む)

受信回路及び電子機器

【課題】PLLの低消費電力化、回路規模の低減、設計の困難性の低減。

【解決手段】所定の局部発振周波数IPA,QPAを出力する局部発振回路110を含み、受信信号RFと局部発振周波数IPA,QPAとを乗算した中間周波信号Iin,Qinを出力するアナログ直交復調回路100と、中間周波信号Iin,Qinを入力しフィルタ信号Iout,Qoutを出力する中心周波数と通過帯域とのどちらか少なくとも一方を可変にできる可変バンドパスフィルタ200と、フィルタ信号Iout,Qoutをデジタル信号Idi,Qdiに変換するアナログ−デジタル変換回路310,320と、所定の数値制御発振周波数IPB,QPBを出力する数値制御発振回路410を含み、デジタル信号Idi,Qdiと数値制御発振周波数IPB,QPBとを乗算した復調信号Idm,Qdmを出力するデジタル直交復調回路400と、を含む受信回路。

(もっと読む)

調整可能な周波数を備える信号発生器

発振信号の周波数は、出力信号の位相および/または周波数を調整するために一時的に調整される。例えば、発振信号の周波数は、出力信号の位相を調整するために、極めて短期間で調整されてもよい。加えて、発振信号の周波数は、出力信号の有効周波数を調整するために、反復される手法で一時的に調整されてもよい。いくつかの態様では、発振信号の周波数は、発振回路に関連したリアクタンス回路の再構成によって調整される。  (もっと読む)

(もっと読む)

信号追跡を行う信号生成器

入力信号を追跡するように出力信号の周波数及び位相が調整される。前記出力信号が導き出される発振信号の周波数を制御するように制御信号が調整される。幾つかの側面においては、前記発振信号の前記周波数は、発振器回路に結合されたリアクティブ回路の再構成によって調整される。前記出力信号の位相は、前記発振信号と調整可能スレショルドの比較に基づいて調整することができる。例えば、前記調整可能スレショルドは、トランジスタ回路に関する調整可能バイアス信号を備えることができ、それにより、前記発振信号は、前記トランジスタ回路への入力として提供され、前記トランジスタ回路の前記出力は、前記出力信号を提供する。 (もっと読む)

101 - 120 / 216

[ Back to top ]