Fターム[5J106RR11]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 増幅器・バッファ (20)

Fターム[5J106RR11]に分類される特許

1 - 20 / 20

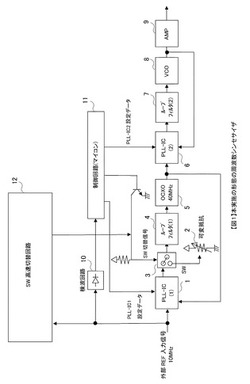

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

周波数制御装置、周波数制御方法、クロック生成回路、電子機器、及び、プログラム

【課題】クロック生成回路におけるハンチング現象を抑制することのできる新たな技術を提供する。

【解決手段】電子機器500は、周波数制御装置510と信号処理部540とを備える。周波数制御装置510は、出力クロック信号を生成するクロック生成回路(クロック生成部512)と、出力クロック信号の周波数を制御する周波数制御部514とを備える。クロック生成部512は、入力された発振制御信号に基づき出力クロック信号を生成する出力クロック生成部(発振部610)と、発振制御信号を生成して出力クロック生成部に供給する発振制御部616とを有する。周波数制御部514は、発振制御部616を制御して発振制御信号を徐々に変化させることにより、出力クロック信号の周波数を徐々に変化させる。

(もっと読む)

信号レベル調整装置及び高周波機器

【課題】電圧制御発振器の後段に設けられた可変減衰器と、検波器と、検波電圧に応じてディジタル/アナログ変換器を介して可変減衰器の減衰量調整用の制御電圧を出力する制御部と、を備えた周波数シンセサイザにおいて、ディジタル/アナログ変換器の出力変化に基づくスプリアスを抑制できる技術を提供すること。

【解決手段】ディジタル/アナログ変換器の出力側と可変減衰器との間にローパスフィルタを設けて、ディジタル/アナログ変換器の出力の変化時に発生するオーバーシュートに対応する周波数成分をカットする。そして制御部が制御電圧を出力してから検波器で検出された信号レベルを読み込むまでの時間は、ローパスフィルタのカットオフ周波数で決まる当該ローパスフィルタの時定数よりも長い時間に設定し、信号レベルの自動制御動作に影響がないようにする。

(もっと読む)

PLL周波数シンセサイザ

【課題】改善された位相雑音特性を有するPLL周波数シンセサイザを提供する。

【解決手段】VCO20は、制御電圧VCNTに応じた周波数fVCOで発振する。周波数ミキサ22は、VCO20の出力信号SVCOとローカル周波数fLOを有するローカル信号SLOを周波数ミキシングする。第1フィルタ26は、ミキサ22によるミキシングにより得られる差周波信号SDIFFを抽出する。位相誤差検出部12は、第1フィルタ26により抽出された差周波信号SDIFFと基準周波数fREFを有する基準信号SREFの位相を比較し、位相差に応じた位相誤差信号VPEを生成する。ループフィルタ18は、位相誤差信号VPEをフィルタリングし、制御電圧VCNTを生成する。第2フィルタ28は、ミキサ22によるミキシングにより得られる和周波信号SSUMを抽出し、出力端子OUTから和周波信号SSUMを出力する。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

同期回路、同期方法、および受信システム

【課題】受信機特性の固体差や時間変動に応じて適切なループゲインを設定することができるようにする。

【解決手段】周波数・位相同期回路においては、主PLL回路31−1によって同期検波を継続しながら、副PLL回路31−2によって、ループゲインを順次変化させて制御誤差値の計測が行われる。2系統のPLL回路である主PLL回路31−1と副PLL回路31−2は、同じ特性を有する部材を用い、同じ回路構成を有するようにして作成された回路である。また、主PLL回路31−1に設定しているループゲインよりも小さい制御誤差値を求めることができるループゲインが見つかる度に、主PLL回路31−1のループゲインを副PLL回路31−2のループゲインで置き換えていくことが行われる。本発明は、デジタルテレビジョン放送を受信するテレビジョン受像機、録画機器に適用することができる。

(もっと読む)

デジタル制御型の周波数発生装置

【課題】本発明は、従来の周波数発生装置から共振チップを取り替えずに、その出力のクロック信号を需要の周波数に自由に調整することができる周波数発生装置を提供する。

【解決手段】所定の振動周波数を有する第1クロック信号を発生する発振器モジュールと、操作により、需要の周波数に対応して制御信号を発生するプログラマブル制御モジュールと、前記発振器モジュールからの前記第1クロック信号と前記プログラマブル制御モジュールからの前記制御信号とを受信し、前記両信号に基づいて前記需要の周波数を有する第2クロック信号を発生することができるように前記発振器モジュールと前記プログラマブル制御モジュールとに電気的に連結されている直接デジタル周波数シンセサイザとからなっていることを特徴とするデジタル制御型の周波数発生装置を提供する。

(もっと読む)

直接変換プロセスにおける局部発振器漏洩制御

【課題】直接変換プロセスにおける局部発振器の漏洩制御。

【解決手段】ゼロ中間周波数(IF)受信機あるいは送信機における、局部発振器(LO)周波数を発生するためのシステムおよび方法が与えられる。電圧制御発振器(VCO)から信号が受信される。信号はVCO周波数を有している。VCO周波数は分周された周波数を有している信号を生成するために数値Nによって分周される。VCO周波数を有している信号はそこで、出力周波数を有している出力信号を生成するために、分周された周波数を有している信号と混合される。局部発振器漏洩が減少される。したがって、受信機あるいは送信機は、複数の無線通信帯域およびモードで動作し、そして組み合わせられた規格を満足することが可能である。

(もっと読む)

シンセサイザモジュール

【課題】 仕向け先地域にかかわらず、全世界共通で使用することができ、且つ出力周波数の設定を容易にできるシンセサイザモジュールを提供する。

【解決手段】 不揮発性メモリ12の計算式テーブルに、複数の周波数モードと、それに対応するキャリア周波数の計算式を記憶しておき、更に、装置の初期設定時に設定された周波数モードを特定のエリアに記憶しておき、CPU10が、周波数設定時にロータリーSW10からチャンネル番号が入力されると、現在設定されている周波数モードに応じた計算式に基づいて、チャンネル番号に対応するキャリア周波数を算出して、PLL部のCONT2に当該周波数を設定するシンセサイザモジュールとしている。

(もっと読む)

RF通信用半導体集積回路

【課題】RF ICで、基準周波数信号の周波数を制御するAFC制御用D/A変換器の出力信号の外部電源電圧の変動による変動を低減すること。

【解決手段】基準周波数発振器314を制御するAFC制御用D/A変換器315は、3個のボルテージフォロワAMP1、2、3を含む電圧ポテンショメータ型D/A変換器で構成される。少なくとも後段のボルテージフォロワAMP3では、NMOS差動入力回路とCMOS出力回路とバイアス回路とは外部電源電圧Vdd_extを供給する一方、PMOS差動入力回路PMOS_DAは基準電圧発生器RVGから生成された内部安定化電源電圧Vdd_intを供給する。PMOS差動のMP1、MP2のペア性のずれがあっても、外部電源電圧Vdd_extの増大によるPMOS電流源のMP3の電流の増大は抑制される。PMOS差動の入力オフセット電圧も増大せず、AFC制御アナログ出力信号の変動を低減できる。

(もっと読む)

シンセサイザモジュール

【課題】 周波数設定者の利用形態に応じて発振周波数の設定を容易できるシンセサイザモジュールを提供する。

【解決手段】 CPU10は、ロータリーSW11の状態を判断し、ロータリーSW11で設定されたCH番号が有効な値であれば、スイッチによる周波数設定を行い、有効な値でなければ、パワーオフ直前の最終設定周波数を再設定し、その後にシリアルバス13から入力されたシリアル信号による周波数設定を行うものであり、ロータリーSW11による設定とシリアル信号による設定をぶつかることなく周波数設定者の利用形態に応じて適正に行うことができるシンセサイザモジュールである。

(もっと読む)

プリスケーラ及びバッファ

【課題】広帯域化を図ることができるプリスケーラを提供すること。

【解決手段】プリスケーラ33は、バッファ部41とカウンタ43とを備える。バッファ部41は、駆動能力が異なる複数のインバータ回路52a〜52cからなる初段回路52と、直列接続された複数のインバータ回路54a〜54dと、帰還回路55とを備える。初段回路52の各インバータ回路52a〜52cは、第1スイッチ部51と第2スイッチ部53とにより、何れか1つに信号fvが入力され、出力端子が後段のインバータ回路54aに接続され、初段回路52における駆動能力が可変される。帰還回路55は、電圧V1,V2により設定される抵抗として機能する。

(もっと読む)

通信用半導体集積回路

【課題】基準周波数発振器DCXOの発振出力信号をレベル変換器Lev_Convによりレベル変換する際に発生するDCXOの発振出力信号の高調波成分によるRF送信用電圧制御発振器TXVCOの発振出力信号の近傍への漏れ込みによる影響を低減すること。

【解決手段】レベル変換器Lev_ConvはDCXOの発振出力信号をレベル変換して、レベル変換信号をRF送信用電圧制御発振器TXVCOの発振周波数を制御するPLL・フラクショナルシンセサイザFrct_Synthの位相比較器PDCに供給する。このLev_Convは、基準周波数発振器DCXOの基準周波数信号を増幅する自己バイアス型電圧増幅器Self_Bias_Volt_Ampを含む。自己バイアス型電圧増幅器は、結合容量C1、増幅トランジスタQn5、負荷Qp5、バイアス素子R1を含み、外部電源電圧Vdd_extが変動しても、高調波成分のレベル変動を抑制する。

(もっと読む)

クロック分周回路

【課題】通常は1つの分周回路で全クロック源の分周を担う回路に対して、各クロック源に分周回路を接続して配置し、バッファ回路などの消費電力の大きい回路の割合を減らして、レイアウト的な制限からくる消費電力の増加を回避する分周回路を提供する。

【解決手段】クロック信号を生成する複数のクロック生成回路と、クロック生成回路から出力したクロック信号を分周するクロック分周回路を、クロック生成回路ごとの出力の後段に配設し、クロック分周回路ごとに分周された複数のクロック信号を入力して、1つの信号を選択する選択回路を、クロック分周回路の後段に配設する、ことを特徴とする半導体集積装置である。

(もっと読む)

周波数可変シンセサイザおよび周波数可変発振器

【課題】広帯域の周波数帯で発振可能で、所望の周波数帯域への切替え機能を有する周波数可変シンセサイザを提供する。

【解決手段】負性抵抗を発生する能動素子部3の動作と周波数切替え制御信号とにより可変共振器2で可変の共振周波数で発振した信号を、分周比制御信号により可変分周器8で可変に分周して出力信号端子6Aから出力する。可変共振器2は、1ないし複数のインダクタとキャパシタとスイッチ素子とからなり、スイッチ素子を切替えることにより可変の共振周波数で発振する。可変分周器8は、可変共振器2の共振周波数の(1/i)、(1/2i)、(1/2)iまたはそれらの組み合わせで分周した周波数を出力する。インダクタに厚膜の配線金属層、裏面研磨の基板、基板から浮かした配線層のいずれかを、また、スイッチ素子にMEMSスイッチ、機械的切替え形スイッチ、FETスイッチ、ダイオードスイッチのいずれかを使用する。

(もっと読む)

VCO駆動回路及び周波数シンセサイザ

【課題】 VCOの制御端子側のインピーダンスを低くし、VCOの位相雑音特性の劣化を防ぎ、VCOの固体バラツキや温度変化に対して固有周波数を一定値に保つVCO駆動回路及び周波数シンセサイザを提供する。

【解決手段】 粗調用周波数のデジタルデータをアナログ出力する粗調用DAC4と、微調用周波数のデジタルデータをアナログ出力する微調用DAC6と、粗調用DAC4からの出力のノイズを除去してVCOの制御端子への入力とする応答速度の遅いLPF5と、微調用DAC6からの出力を電圧に変換し、信号の平滑化を行う応答速度の速いLPF7と、LPF5の入力段とLPF7の入力段とを抵抗R6 で接続し、LPF5の出力とLPF7の出力とをコンデンサC8 で容量結合し、LPF7に電圧制御手段としての可変抵抗R4 を設けたVCO駆動回路及びそれを備えた周波数シンセサイザである。

(もっと読む)

ループフィルタ部品を低減するために二重経路およびデュアルバラクタを用いるタイプII位相ロックループ

フィルタ内のオンチップ部品サイズを低減するデュアルチャージポンプおよび対応する二重信号経路を有し、低減されたループフィルタ部品を備えた位相ロックループ(PLL)。二重経路は、電圧制御発振器内のデュアルバラクタを介して有利に結合され、ループフィルタ部品をさらに低減する。PLLは、二重経路構成を加算するために通常用いられる回路によってもたらされるノイズの欠点をなくす。  (もっと読む)

(もっと読む)

周波数シンセサイザ

【課題】ロックさせる周波数の制御精度と処理速度とを共に擬制にすることなく、PLL回路の構成を1つの半導体チップに集積できるようにする。

【解決手段】アップ/ダウンカウンタ5を用いた第1のロックループによって局部発振周波数の粗調整を行うとともに、S/H回路11を用いた第2のロックループによって局部発振周波数の微調整を行うことにより、位相差に応じてコンデンサに電荷をチャージしたりポンプしたりする動作を不要とし、大容量のコンデンサを用いるLPFを周波数シンセサイザから省略できるようにする。また、S/H回路11を用いた微調整によって局部発振周波数を精度良くロックさせることができるようにするとともに、ロックさせる周波数の制御精度を上げるためにアップ/ダウンカウンタ5のビット数を大きくする必要をなくし、局部発振周波数を所望の周波数に高速にロックさせることができるようにする。

(もっと読む)

多周波出力位相同期発振器

【課題】一つの位相同期回路を用いて多周波の出力信号を得ることが可能な多周波出力位相同期発振器を提供することを目的とする。

【解決手段】本発明に係る多周波出力位相同期発振器6は、外部から入力される基準信号と、後述する電圧制御発振器が出力する信号を分周した比較信号とを位相比較し位相差信号を発生する位相比較器2と、前記位相差信号の高周波成分を除去して直流電圧とするループフィルタ3と、ある一定の自走周波数を有し、前記直流電圧により発振周波数を変化させる電圧制御発振器4と、該電圧制御発振器4が出力する信号の周波数を複数の分周器のトータルで1/N分周し、前記位相比較器2に出力する分周器7、8、9、10とにより構成する。

(もっと読む)

1 - 20 / 20

[ Back to top ]