Fターム[5J106RR12]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 制御装置 (56)

Fターム[5J106RR12]の下位に属するFターム

CPU(マイコン) (28)

Fターム[5J106RR12]に分類される特許

1 - 20 / 28

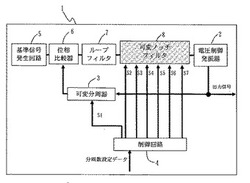

PLL周波数シンセサイザ

【課題】 フラクショナルN方式のPLL(Phase-locked loop;位相同期回路)周波数シンセサイザにおいて生じる、フラクショナルスプリアスを抑圧する。

【解決手段】 可変分周器の分周数を2つ以上の整数値で時間的に切り替えるフラクショナルN方式のPLL周波数シンセサイザにおいて、電圧制御発振器2とループフィルタ7の間に、抑圧周波数および減衰量の制御を可能とする可変ノッチフィルタ8を設けることで、フラクショナルスプリアスを抑圧することができる。

(もっと読む)

半導体集積回路

【課題】単一の回路仕様で世界各国の衛星放送に簡便に対応できる、LNB用半導体集積回路を実現する。

【解決手段】半導体集積回路100の所定の端子電圧を設定することで、PLL回路108の可変分周器110の分周比を設定し、所望の局部発振周波数を得る。供給される直流電位に対応して可変分周器の分周比を制御する第1の分周比設定部と、供給されるパルス信号の有無に対応して可変分周器の分周比を制御する第2の分周比設定部とを備え、第1の分周比設定部または第2の分周比設定部による可変分周器の分周比制御により、局部発振器109の発振周波数を所望の周波数に設定する。

(もっと読む)

信号レベル調整装置及び高周波機器

【課題】電圧制御発振器の後段に設けられた可変減衰器と、検波器と、検波電圧に応じてディジタル/アナログ変換器を介して可変減衰器の減衰量調整用の制御電圧を出力する制御部と、を備えた周波数シンセサイザにおいて、ディジタル/アナログ変換器の出力変化に基づくスプリアスを抑制できる技術を提供すること。

【解決手段】ディジタル/アナログ変換器の出力側と可変減衰器との間にローパスフィルタを設けて、ディジタル/アナログ変換器の出力の変化時に発生するオーバーシュートに対応する周波数成分をカットする。そして制御部が制御電圧を出力してから検波器で検出された信号レベルを読み込むまでの時間は、ローパスフィルタのカットオフ周波数で決まる当該ローパスフィルタの時定数よりも長い時間に設定し、信号レベルの自動制御動作に影響がないようにする。

(もっと読む)

クロック発生装置

【課題】広い温度範囲で高精度なクロック信号を出力可能な、安価でかつコンパクトなサイズのクロック発生装置を提供する。

【解決手段】クロック発生装置は、基準クロック信号を生成する基準クロック生成部11と、第1のクロック信号を生成する第1の発振器12と、前記第1のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第2のクロック信号を生成する第1の精度保証部13と、温度検知部15と、第3のクロック信号を生成する第2の発振器17と、前記第3のクロック信号を前記基準クロック信号と同周波数、同位相となるように補正した第4のクロック信号を生成する第2の精度保証部18と、温度が第1の発振器12の保証温度範囲内の場合には前記第2のクロック信号、保証温度範囲外の場合には前記第4のクロック信号を出力するクロック切替部20と備える。

(もっと読む)

タイミング同期装置、タイミング同期方法

【課題】基準タイミング信号に自装置の内部タイミング信号を正確に同期させるタイミング同期装置を提供する。

【解決手段】所定の時間間隔を示す基準タイミング信号と基準タイミング信号に対応する基準時刻を示す基準時刻情報とを取得する取得部と、クロック周波数を有する内部クロック信号を生成するクロック生成部と、内部クロック信号に基づいて、所定の時間間隔を示す内部タイミング信号と内部タイミング信号に対応する時刻を示す内部時刻情報とを生成する時刻情報生成部と、基準タイミング信号と内部タイミング信号、及び、基準時刻情報と内部時刻情報を比較することにより、基準タイミング信号に対する内部タイミング信号の進み又は遅れを検出し、且つ、基準タイミング信号に対する内部タイミング信号の位相の進み量又は遅れ量を検出する検出部と、位相の進み量又は遅れ量に応じてクロック周波数を調整する調整部と、を備えるタイミング同期装置。

(もっと読む)

スペクトラム拡散クロック生成回路及びその制御方法

【課題】変調度が安定しない。

【解決手段】周波数変調した出力発振信号を出力するPLL回路を有するスペクトラム拡散信号生成回路であって、前記PLL回路は、入力した発振制御信号の値に応じた周波数で前記出力発振信号を出力する発振回路を備え、前記PLL回路によりフィードバックされたPLL信号の周波数を変調させる前記発振制御信号を生成し、この前記発振制御信号の最大値と最小値をモニタし、そのモニタ結果により前記発振制御信号の最大値と最小値を調整し、前記出力発振信号の変調度を所定の値に制御する周波数変調部を、有するスペクトラム拡散クロック生成回路。

(もっと読む)

半導体集積回路

【課題】複数の無線通信チャンネルについて、PLL回路全体の動作特性に基づいて電圧制御発振器の精密なキャリブレーションを行う。

【解決手段】半導体集積回路は、高周波信号を生成する電圧制御発振器を含むPLL回路と、電圧制御発振器のトランジスタに選択的に負荷される複数のキャパシタと、複数の無線通信チャンネルについて電圧制御発振器の発振周波数を補正するためのキャパシタに関する情報を格納する格納部と、キャリブレーションモードにおいて、複数の無線通信チャンネルについてPLL回路のループ特性を測定することにより補正用キャパシタに関する情報を格納部に格納し、通常動作モードにおいて、選択された無線通信チャンネルに従って、格納部に格納されている情報を読み出すことにより補正用キャパシタを決定するキャリブレーション回路とを具備する。

(もっと読む)

PLL回路

【課題】 全てのチャンネルについてスプリアス特性が良好なVCO出力を得ることができ、温度変化による特性変動を抑えることができるPLL回路を提供する。

【解決手段】 制御回路3が、温度センサ31と、温度に応じてチャンネル番号毎に電圧制御発振器の出力におけるスプリアス特性が良好となる分周比を記憶した分周比テーブル32とを備え、温度センサ31で検出された温度及び入力されたチャンネル番号に対応する分周比を分周比テーブル32から読み取って、PLLIC2に設定すると共に、DDS回路(基準周波数生成回路)4にチャンネル番号と分周比とを設定し、DDS回路4が、チャンネル番号と分周比に基いて基準周波数の値を算出して、当該値に対応する基準周波数を生成するPLL回路としている。

(もっと読む)

発振器および位相同期回路のループ帯域補正方法

【課題】安定した高周波信号を発振する発振器および位相同期回路のループ帯域補正方法を実現する。

【解決手段】基準周波数の基準信号を発生する基準信号発生部と、前記基準信号とフィードバック信号との位相差に応じた電圧を出力する位相比較部と、前記位相比較部から出力された電圧が入力され、外部制御信号により、前記位相比較部から出力された電圧のゲインを調整するループフィルタと、前記ループフィルタによりゲインが調整された調整信号に応じた周波数の出力信号を発振する電圧制御発振部と、前記出力信号を分周した分周信号を前記フィードバック信号として前記位相比較部にフィードバックする分周部とを備える。

(もっと読む)

ローカル信号生成回路

【課題】従来のローカル信号生成回路は、回路面積と消費電力が大きくなる問題があった。

【解決手段】本発明にかかるローカル信号生成回路は、基準信号と帰還信号の位相差を検出し、誤差信号を出力する位相比較器21aと、誤差信号を受け昇圧電圧を生成するチャージポンプ回路22aと、昇圧電圧を整形してチューニング電圧Vtuを生成するループフィルタ23aと、チューニング電圧Vtuに基づき所定の周波数を有する第1の出力信号(I_high、Q_high)を生成する電圧制御発振器24aと、第1の出力信号(I_high、Q_high)を所定の周波数に分周した第2の出力信号(I_low、Q_low)として出力すると共に、第1の出力信号(I_high、Q_high)を前記所定の周波数に分周した分周信号を帰還信号を生成する分周器26aに出力するプリスケーラ25aと、を有するものである。

(もっと読む)

フラクショナル−N方式位相同期ループ形周波数シンセサイザ

【課題】 位相比較器の位相差に対する検波電圧特性の非線形性によって、F−N方式PLL周波数シンセサイザ出力に発生するスプリアスの抑圧を実現することを目的とする。

【解決手段】 高周波信号を生成する電圧制御発振器と、前記高周波信号より同期信号を生成する可変分周器と、基準信号を生成する基準発振源と、前記基準信号より位相差を有する2つの基準信号を生成する基準信号生成手段と、前記それぞれの基準信号と前記同期信号を入力とし、第1と第2の位相比較信号を出力する第1の位相比較器と、第3と第4の位相比較信号を出力する第2の位相比較器と、前記第1と第2の位相比較信号を差分した差分結果と、前記第3と第4の位相比較信号を差分した差分結果を合成して平滑化した合成信号を出力するループフィルタとを備え、前記合成信号に応じて電圧制御発振器を制御することにより前記高周波信号を生成する。

(もっと読む)

基準クロック信号生成装置

【課題】

デジタル映像信号処理で必要となる所定周波数の基準クロック信号を得る手法として、ジッター発生要因を有する手法を用いた場合でも、このジッターに起因する画質劣化や音質劣化を出来る限り目立たなくすることを可能とする装置を提供する。

【解決手段】

映像信号や音声信号の信号レベルが低い期間か否かを検出し、信号レベルが低くない期間は、クロック信号を生成するPLL回路の構成要素である帰還分周器5の分周比率を固定値とし、信号レベルが低い期間は、帰還分周器5の分周比率を可変して、これら各期間よりも十分に長い期間で積分すると、全体的にみれば所定周波数となる基準クロック信号を生成する。

(もっと読む)

シンセサイザまたは発振器モジュールと、このシンセサイザを用いたシンセサイザモジュール、受信装置、及び電子機器、ならびに分周器の分周比の制御方法

【課題】制御部による分周器の制御に起因したノイズの発生を抑え、受信特性の良好な受信機を実現可能なシンセサイザを提供することを目的とする。

【解決手段】制御部7は、温度を検出する温度検出部8の出力信号に基づいて第2の分周器6へ適当な整数分周数Mや分数分周数Nの制御信号を送り、第2の分周器6の分周比を変化させる。つまり、第2の分周器6は、分周数Mが入力される整数部分と、分周数Nが入力される分数部分により構成される。制御部7は、温度を検出する温度検出部8の温度信号に基づいて第2分周器6の分周比を不均一な時間間隔で変化させる。これにより、第2分周器6の制御に伴い特定周波数に多数発生するノイズを抑圧することができ、シンセサイザの位相雑音を低減することができる。

(もっと読む)

無線受信回路および入力妨害波低減回路

【課題】広い周波数領域に渡って妨害波を低減できる入力妨害波低減回路の小型化、およびそのような入力妨害波低減回路を備える無線受信回路の小型化を図る。

【解決手段】受信信号は、トランジスタQ1のゲートに与えられる。トランジスタQ1はトランジスタQA〜QDに接続され、トランジスタQ1、QA〜QDにより4個の増幅器が構成される。トランジスタQA〜QDには、それぞれ調整回路13A〜13Dが接続されている。調整回路13A〜13Dは、LC共振回路であり、その共振周波数は調整信号および微調整信号により調整される。選択信号は、4個の増幅器の中から使用すべき増幅器を選択する。選択された増幅器の利得周波数は、対応する調整回路(13A〜13D)の共振周波数に応じて決まる。選択された増幅器により増幅された信号が出力される。

(もっと読む)

分数分周PLL装置、およびその制御方法

【課題】設定すべきパラメータ数が減ぜられて使い勝手の向上が図られると共に、回路の簡略化を図ることが可能な分数分周PLL装置、およびその制御方法を提供すること

【解決手段】第1分周信号fprの初期のAサイクルの期間は、第2分周信号fAがハイレベル、第3分周信号fBがローレベルに維持される。3モジュラスプリスケーラ13は(M+1)分周値となる。引き続くBサイクルでは、第2分周信号fAがローレベル、第3分周信号fBがハイレベルである。3モジュラスプリスケーラ13は、ΣΔ変調器8から出力される擬似乱数の符号に合わせて、負値の場合に(M−1)分周値、正値の場合に(M+1)分周値となる。その後は、M分周となる。比較分周器4では、擬似乱数値Bxを含む(MN+A+Bx)の分周値が得られる。負値を含む擬似乱数をそのまま使用してΣΔ変調による分数分周を実現できる。

(もっと読む)

同期掃引シンセサイザ

【課題】 本発明は、スタート周波数からストップ周波数まで、階段状に周波数を高速変化させ、且つスイープタイミングに同期した同期パルスを出力することができる同期掃引周波数シンセサイザを提供する。

【解決手段】 電圧制御発振器11が、位相比較制御部でロックが検出されるまでは、特定のスタート周波数を提供し、ロックが検出された後は、階段波形となるスイープ周波数を提供し、位相比較制御部が、スイープのタイミングに同期した掃引同期パルスを出力する同期掃引周波数シンセサイザとしている。

(もっと読む)

信号発生装置

【課題】IC化が可能なように、VCOの出力の位相雑音のうち、中心周波数から所望の離調周波数における位相雑音を軽減化した信号発生装置を提供することである。

【解決手段】基準信号を出力する基準信号源1と、発振周波数を電圧制御可能な可変信号源3aを有し、可変信号源の出力信号を基準信号に位相同期させる複数のPLL手段31、32、・・3)と、各PLL手段の該各可変信号源の出力信号を合成する合成手段2と、各可変信号源の出力信号の位相が前記合成手段により合成後に同一となるように各可変信号源の出力信号の位相を調整する移相手段41、42、・・4Mとを備えた。

(もっと読む)

信号発生装置

【課題】本発明では、汎用DDSを使用した周波数可変の信号発生装置において、ジッター発生を抑制し、高精度の周波数可変の矩形パルス信号を発生する。

【解決手段】周波数可変の信号発生装置は、設定値に応じて変更される周波数のアナログ信号を出力するDDS1と、該アナログ信号から該周波数の第1矩形パルス信号を生成するコンパレータ3と、第1矩形パルス信号を設定される分周比で分周した第2矩形パルス信号を出力するプログラマブル分周器41と、制御部4とを備える。該周波数を高周波数領域側に変更の場合、該分周器に対し第1矩形パルス信号を出力信号Soとする。該周波数を低周波数領域側に変更の場合、DDSに対して設定値を分周比倍の値に変更制御して該分周比倍の周波数を有する第1矩形パルス信号を発生させ、分周器において当該分周比で分周した当該周波数の第2矩形パルス信号を出力信号Soとする。

(もっと読む)

RF通信用半導体集積回路

【課題】RF ICで、基準周波数信号の周波数を制御するAFC制御用D/A変換器の出力信号の外部電源電圧の変動による変動を低減すること。

【解決手段】基準周波数発振器314を制御するAFC制御用D/A変換器315は、3個のボルテージフォロワAMP1、2、3を含む電圧ポテンショメータ型D/A変換器で構成される。少なくとも後段のボルテージフォロワAMP3では、NMOS差動入力回路とCMOS出力回路とバイアス回路とは外部電源電圧Vdd_extを供給する一方、PMOS差動入力回路PMOS_DAは基準電圧発生器RVGから生成された内部安定化電源電圧Vdd_intを供給する。PMOS差動のMP1、MP2のペア性のずれがあっても、外部電源電圧Vdd_extの増大によるPMOS電流源のMP3の電流の増大は抑制される。PMOS差動の入力オフセット電圧も増大せず、AFC制御アナログ出力信号の変動を低減できる。

(もっと読む)

周波数シンセサイザ

【課題】 AD変換器への入力レベルが変化したときに、PLL制御が正常に動作しない状況を防止して周波数ずれの発生を防止できる周波数シンセサイザを提供する。

【解決手段】 キャリアリムーブ16と、逆回転ベクトル乗算部17と、位相の時間差検出部18と、加算器19と、位相差の累積加算部20と、ループフィルタ21と、パラメータ出力部25と、振幅情報検出部26と、フィルタ27と、乗算器28とをFPGAで構成し、振幅情報検出部26で検出された振幅情報の値をアンロック検出手段が監視し、当該値が適正範囲内であれば、PLL制御におけるロック(同期)処理を行い、当該値が適正範囲外であれば、PLL制御におけるアンロックを検出するようにした周波数シンセサイザである。

(もっと読む)

1 - 20 / 28

[ Back to top ]