Fターム[5J106RR13]の内容

発信器の安定化、同期、周波数シンセサイザ (26,591) | 構成要素 (681) | 制御装置 (56) | CPU(マイコン) (28)

Fターム[5J106RR13]に分類される特許

1 - 20 / 28

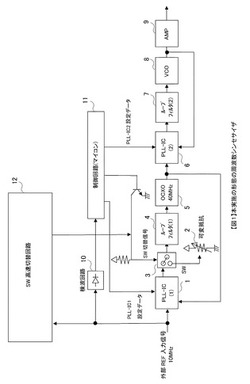

周波数シンセサイザ

【課題】 外部基準信号の入力断で高速にスイッチを切り替えて一定の電圧を発振器の制御電圧として出力でき、出力周波数の変動量を最小限に抑えることができる周波数シンセサイザを提供する。

【解決手段】 制御回路11が、検波回路10からの検波出力を入力し、外部基準入力信号「入」の場合には、SW3にPLL−IC1の出力をループフィルタ4に出力させる切替信号を出力し、外部基準入力信号「断」の場合には、SW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力し、スイッチ高速切替回路12が、外部基準入力信号の「断」を検出して制御回路11より高速にSW3に可変抵抗2の出力をループフィルタ4に出力させる切替信号を出力する周波数シンセサイザである。

(もっと読む)

クロック生成装置

【課題】 異なる複数の基準周波数に同期したクロックを生成でき、また、自走動作時に、ノイズの発生と消費電力を低減することができるクロック生成装置を提供する

【解決手段】 複数の外部基準クロックを入力可能とし、信号レベル検出回路24,25部が入力された外部基準信号の帯域毎にレベル検出し、マイクロコントローラ4が、検出された信号レベルに応じて、一つの外部基準信号のみが適正レベルであった場合に、自走制御信号によりクロック選択回路34の外部基準クロックの出力をイネーブルとし、選択制御信号により適正レベルであった外部基準クロックを選択させ、それ以外の場合には、自走制御信号によりクロック選択回路34の外部基準クロックの出力をディセーブルとすると共に、PLL−IC5をパワーダウンさせて、電圧制御発振器9に自走制御用直流電圧生成回路6からの電圧に基づいて自走発振を行わせるクロック生成装置としている。

(もっと読む)

周波数シンセサイザ装置及びその製造システム

【課題】 多数の類似機種を製造する場合でも、製造工程や検査工程における人為的なミスをなくし、適正な仕様とすることができる周波数シンセサイザ装置及びその製造システムを提供する。

【解決手段】 周波数シンセサイザ装置1のハードウェア識別子回路13が機種に対応するハードウェア識別子を記憶し、外部PC2が複数のハードウェア識別子とそれに対応するパラメータを記憶しており、マイクロコントローラ12が、外部PC2からハードウェア識別子の要求を受信すると、ハードウェア識別子回路13からハードウェア識別子を読み取って外部PC2に出力し、外部PC2が、周波数シンセサイザ装置1から取得したハードウェア識別子に対応して記憶されているパラメータを読み取って周波数シンセサイザ装置1に出力し、マイクロコントローラ12が、受信したパラメータを不揮発性メモリ14に記憶する周波数シンセサイザ装置及びその製造システムとしている。

(もっと読む)

周波数シンセサイザ

【課題】

応答性が高く維持され、かつハードウェアの構成が簡略化されるにもかかわらず、各部の変動やバラツキに対して安定に適応できる周波数シンセサイザを提供する。

【解決手段】

位相同期ループが供給する制御情報に対応した所望の周波数で出力信号を生成する可変周波発振器を有し、前記所望の周波数となり得る目標周波数毎に、前期可変周波発振器に与えられるべき制御情報の初期値が予め登録されたテーブルと、前記所望の周波数が切り替えられたときに、前記位相同期ループの応答を規制し、かつ最新の所望の周波数に対応して前期テーブルに登録されている初期値を前記可変周波発振器に供給する初期値設定手段と、前記位相同期ループのロックアップを前記位相差に基づいて検出するロックアップ検出手段と、前記ロックアップが検出されたときに、前記応答の規制を解除し、かつ前記初期値設定手段による初期値の供給を規制する位相同期再開手段とを備える。

(もっと読む)

周波数シンセサイザシステム及び周波数信号の出力方法

【課題】設定された周波数に応じて、適切なバンドパスフィルタを選択することが可能な周波数シンセサイザシステム及び周波数信号の出力方法を提供する。

【解決手段】ミキサ53は、第1、第2のシンセサイザ1、2から各々出力された第1、第2の周波数信号を混合して、予め設定された周波数の周波数信号を含む混合信号を出力し、周波数選択部41は所定の式で表されるスプリアス成分が予め設定した周波数範囲内に存在しないこととなる第1の周波数信号及び第2の周波数信号の周波数の組み合わせを選択する。フィルタ選択部42は周波数選択部41にて選択された周波数の組み合わせから得られる混合信号に含まれるスプリアス成分の信号レベルが予め設定したレベル以下まで低減されるように、複数のバンドパスフィルタから当該混合信号を処理するバンドパスフィルタを選択する。

(もっと読む)

発振器

【課題】フロア雑音または位相雑音を抑えることができ、かつ分周器の分周比の設定に手間がかからない発振器を提供すること。

【解決手段】周波数シンセサイザの出力信号を順次分周する複数の分周器と、前記複数の分周器における最終段の分周器から目的とする周波数が得られるように、当該複数の分周器の各々について、入力周波数と分周比との組み合わせを複数設定すると共に各組み合わせ毎に、各段の分周器の出力信号のフロア雑音または位相雑音の大きさを記載した分周特性データを記憶する記憶部と、前記記憶部に記憶されている分周特性データに基づいて、各分周器の許容入力周波数の範囲内でありかつ最終段の分周器からの出力信号のフロア雑音または位相雑音が良好な入力周波数と分周比との組み合わせを判断して選択する選択部と、を備えるように発振器を構成する。

(もっと読む)

周波数シンセサイザ及び周波数シンセサイザの調整方法

【課題】位相雑音を改善すると共に、安定して作動する周波数シンセサイザ等を提供する。

【解決手段】電圧制御発振部から出力された周波数信号と周波数設定部から出力された周波数信号との差分を増幅して得られた差分信号を、前記周波数設定部から出力された周波数信号と直交する検波信号と直交検波して得た両周波数信号の位相差に基づいて前記電圧制御発振部の制御電圧を調整する周波数シンセサイザを立ち上げる際に、前記差分信号を得る差動増幅器から電圧制御発振部を切り離した状態で、第1の位相補正部により予め定めた補正量だけ前記検波信号の位相を補正し、第2の位相補正部により前記検波信号をクロック単位で遅らせて出力することにより、前記周波数設定部よりディジタルの周波数信号が出力された時点から前記差分信号が得られるまでのタイミングと、検波信号が得られるまでのタイミングとをそろえる。

(もっと読む)

デジタル制御型の周波数発生装置

【課題】本発明は、従来の周波数発生装置から共振チップを取り替えずに、その出力のクロック信号を需要の周波数に自由に調整することができる周波数発生装置を提供する。

【解決手段】所定の振動周波数を有する第1クロック信号を発生する発振器モジュールと、操作により、需要の周波数に対応して制御信号を発生するプログラマブル制御モジュールと、前記発振器モジュールからの前記第1クロック信号と前記プログラマブル制御モジュールからの前記制御信号とを受信し、前記両信号に基づいて前記需要の周波数を有する第2クロック信号を発生することができるように前記発振器モジュールと前記プログラマブル制御モジュールとに電気的に連結されている直接デジタル周波数シンセサイザとからなっていることを特徴とするデジタル制御型の周波数発生装置を提供する。

(もっと読む)

分数分割電荷補償手段を有する周波数シンセサイザ

【課題】分数−N補償法で用いられる電荷ポンプを容易に整合し、分数分割によって導入された望ましくない周波数成分を濾波する。

【解決手段】VCO周波数分割器309と基準周波数信号303との間の位相不整合の分数−NPLLにおける補償が可変電荷ポンプ装置307により行われる。移相比較器305は、電荷ポンプ装置の電荷ポンプのいくつかを早くオンにし、残りの電荷ポンプを遅れてオンにするために補償論理501を有する。このプロセスは、部分電荷を適切に補償するために正確な時点で等価電荷をオンにする。

(もっと読む)

周波数出力装置の内部基準信号源を校正する方法

【課題】簡便な手法で正確な校正を行うことが可能な周波数シンセサイザの内部基準信号を校正する方法を提供する。

【解決手段】基準クロック信号と周波数設定信号とに基づいて、設定された周波数信号を出力する周波数シンセサイザ1の、前記基準クロック信号を出力する内部基準信号源16を校正する手法において、前記周波数シンセサイザ1を周波数設定信号に基づいて動作させ、その出力周波数を周波数測定装置3により測定する工程と、測定された出力周波数と前記周波数設定信号により決定される周波数設定値との周波数差に基づいて、外部制御機器2により、周波数シンセサイザ1の不揮発性メモリ17に記憶されている指令値を増減して最適な指令値とする工程と、を含む。

(もっと読む)

フェーズロックループにおけるデジタル制御された発振器の出力のディザリング

PLLのデジタル制御された発振器(DCO)は、DCO_OUT信号がディザされた間隔で変化する周波数を持つように、ディザされる。一例では、DCOは、入って来るデジタルチューニングワードのディザされていないストリームを受け取り、ディザされた基準クロック信号REFDを受け取り、DCO_OUT信号を出力し、その周波数変化がディザされた間隔で起こるようになっている。PLLがセルラー電話の送信機の局部発振器で用いられる場合、DCOの新規なディザリングは、デジタルイメージノイズが、メイン局部発振器周波数からの特定の周波数オフセットで、より少なくなるように、デジタルイメージノイズを周波数拡散する。デジタルイメージノイズの周波数拡散によって、PLL基準クロックの周波数を増大する必要なく、ノイズの仕様を満たすことが可能になる。基準クロックの周波数の増大を回避して、ノイズの仕様を満たすことにより、パワーの消費の増大が回避される。  (もっと読む)

(もっと読む)

位相差補正回路及び位相差補正方法

【課題】現用系と予備系の基準クロックの位相同期の精度を向上させる。

【解決手段】基準クロック供給システムは、現用系のクロック供給回路及び予備系のクロック供給回路の冗長構成で形成され、現用系から第1の基準クロックを供給すると共に予備系から第1の基準クロックに位相同期させた第2の基準クロックを供給する。位相差補正回路は、基準クロック供給システムから第1及び第2の基準クロックを受信する側で第1及び第2の基準クロック間の位相差を測定し、その位相差情報を基準クロック供給システムにフォードバックさせる位相差測定部を有し、位相差情報に応じて、基準クロック供給システムによる第1及び第2の基準クロックの位相同期動作に補正をかける。

(もっと読む)

局部発振器および無線通信装置

【課題】 ループ帯域内のノイズ増大を招くことなく、ヘテロダイン方式におけるローカル周波数の変調精度を向上することを目的とする。

【解決手段】

本発明の局部発振器は、基準発振器214で生成された基準信号から複数の参照周波数に対応した複数の参照信号を生成する第1PLL312と、第1PLL312からの複数の参照信号から複数のローカル周波数に対応した複数のローカル信号を生成する第2PLL314と、を備えることを特徴としている。

(もっと読む)

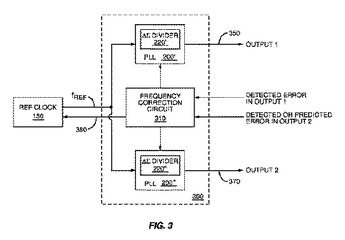

多出力周波数シンセサイザにおける周波数制御のための装置と方法

共通の基準周波数信号に位相同期した2つ以上の信号を合成(シンセサイズ)するための方法と回路とを開示する。1つの実施例では、その方法は、第1と第2の位相同期ループ回路(200′,200″)を使用して、基準クロック信号に位相同期する第1と第2の出力信号(350,370)を生成する工程を備える。第1の出力信号において検出された周波数誤差に応じて、第1の出力信号(350)は、第1の位相同期ループ回路における周波数分周比を調整することにより補正される。第2の出力信号(370)は、検出した周波数誤差から算出される調整パラメータを使用して、第2の位相同期ループ回路における周波数分周比を調整することにより、第1の出力信号への補正とは別個に補正される。別の代表的な方法では、第1と第2の出力信号は、第1と第2の位相同期ループ回路を使用して、上述したように生成される。第1の出力信号において検出された周波数誤差に応じて、第1の位相同期ループ回路における周波数分周比を調整し、制御信号(360)を生成して基準クロック信号の周波数を調整することにより、第1の出力信号が補正される。第2の出力信号(370)は共通の基準クロック信号から導出されるので、基準クロック周波数(FREF)に対する調整はまた、第2の出力信号の周波数も調整するであろう。いくつかの実施例においては、第2の位相同期ループ回路における周波数分周比を調整することにより、第2の出力信号(370)に対する付加的な調整を施すことができる。記述した方法を実施するための回路もまた開示される。  (もっと読む)

(もっと読む)

半導体装置及びそれを用いた携帯端末

【課題】PLL回路の設定を任意に行うことができる半導体装置及びそれを用いた携帯端末を提供する。

【解決手段】PLL回路と、入力画像データの解像度を判定する判定回路と、解像度に応じてPLL回路の設定を行う設定回路とを備えたことにより、PLL回路の設定を任意に行うことができる半導体装置及びそれを用いた携帯端末の提供を実現できる。

(もっと読む)

クロック生成回路

【課題】 CPUの負荷を軽減するとともに、回路規模またはシステムの規模の増大の抑制が可能なクロック生成回路を提供する。

【解決手段】 制御信号に基づいてクロック信号の周波数を制御して出力する発振回路と、所定期間、発振回路が出力するクロック信号のパルス数をカウントしてカウント値を生成するカウンタと、カウント値と、予め設定された周波数に基づいた設定値と、を減算して差分データを生成する減算回路と、差分データに基づいて、制御信号値を補正する制御信号生成補正回路と、制御値信号をアナログ信号に変換して制御信号を生成し、発振回路に出力するデジタル−アナログ変換回路と、を備えることで、上記課題を解決することができる。

(もっと読む)

位相同期発振器及びその制御方法

【課題】VCO回路の特性バラツキや温度変動によらず、簡単な構成及び制御で常に高安定なVCO出力が得られることを課題とする。

【解決手段】位相比較器と、ローパスフィルタと、主制御を行う制御部と、該制御部出力の制御電圧で駆動されるVCO回路と、その出力を分周する可変分周器とからなるPLLループを備える位相同期発振器であって、制御部は、PLLループを複数周波数でロックさせて各ロック時の制御電圧を測定し、該測定した各制御電圧に基づき、VCO回路のリニアリティー校正された変調感度を求めると共に、該PLLループを所定周波数でロックさせた後、該PLLループを開放した状態で、前記求めた変調感度に基づきVCO回路に所定周波数を中心とするリニアリティー補正された周波数変化を発生させるための制御電圧信号を生成する。

(もっと読む)

複数の通信システムのための基準信号生成

【課題】複数の通信システムのための基準信号を生成する技術について説明する。

【解決手段】装置は基準発振器、周波数制御部及び複数の周波数シンセサイザを含む。基準発振器は、水晶発振器または他のある形式の発振器であり、主基準信号を生成する。周波数制御部は、主基準信号の周波数誤差を推定し、周波数誤差推定値を出力する。複数の周波数シンセサイザは、主基準信号を受け取り、複数のシステムのための複数のシステム基準信号を生成する。少なくとも一つの(例えば各々の)周波数シンセサイザは、周波数制御部からの周波数誤差推定値に基づいて主基準信号の周波数誤差を補正する。各周波数シンセサイザは、位相同期ループ(PLL)のための分周器制御信号を生成するために使用されるシグマ・デルタ変調器を含む。分周器制御信号は、主基準信号の周波数誤差を補正する。

(もっと読む)

シンセサイザモジュール

【課題】 周波数設定者の利用形態に応じて発振周波数の設定を容易できるシンセサイザモジュールを提供する。

【解決手段】 CPU10は、ロータリーSW11の状態を判断し、ロータリーSW11で設定されたCH番号が有効な値であれば、スイッチによる周波数設定を行い、有効な値でなければ、パワーオフ直前の最終設定周波数を再設定し、その後にシリアルバス13から入力されたシリアル信号による周波数設定を行うものであり、ロータリーSW11による設定とシリアル信号による設定をぶつかることなく周波数設定者の利用形態に応じて適正に行うことができるシンセサイザモジュールである。

(もっと読む)

ディジタル処理装置のモジュール選択と機能切換方式

【課題】制御モジュール100と2台の被制御モジュール200,300をコネクタ401,402で結合し、I2Cバスインタフェースを使用してコマンドとデータ伝送するディジタル処理装置において、同じハードウェア構成の被制御モジュールを使用してその選択と機能切換を簡易にする。

【解決手段】コネクタには1本のモジュール識別用端子(ピン)を設け、制御モジュール側では識別用端子をグランドまたは開放することで論理信号を被制御モジュールに入力できるようにし、被制御モジュールでは接続するコネクタの違いによってその識別用端子の論理状態から自アドレスの設定および機能切換えを行う。

(もっと読む)

1 - 20 / 28

[ Back to top ]