Fターム[5J500AA04]の内容

Fターム[5J500AA04]に分類される特許

41 - 60 / 438

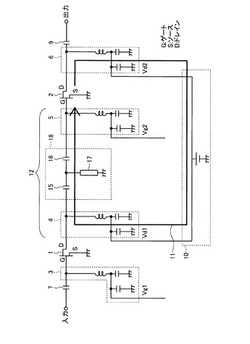

多段増幅器

【課題】低周波数帯域の利得を効果的に抑圧して発振の発生を抑制すると共に、回路の高密度実装を可能とする多段増幅器を提供する。

【解決手段】FET1,2に、ゲートバイアス電圧を印加する入力整合回路3,5と、FET1,2に、ドレインバイアス電圧を印加する出力整合回路4,6と、出力整合回路4と入力整合回路5との間に直列接続されたコンデンサ15,16、および、一端がコンデンサ15,16間の接続点に接続され他端が接地された誘導性の線路17を含み構成されたハイパスフィルタ18と、を備え、コンデンサ15,16のキャパシタンス値および線路17のインダクタンス値は、増幅素子の動作周波数よりも低い周波数帯域において、出力整合回路6と出力整合回路4とハイパスフィルタ18とを介して形成されるドレインバイアスループ11の損失が、FET2の利得よりも大きくなるように設定する。

(もっと読む)

C級増幅器

【課題】高効率でかつ広帯域化されたC級増幅器を提供する。

【解決手段】本実施の形態に係るC級増幅器は、電源電圧がVdc、最大電流がImaxの増幅素子の流通角θoがπ(rad)未満において、前記増幅素子の等価回路の従属電流源から見た基本波の負荷インピーダンスをZ1=R1+j・X1、2倍波の負荷インピーダンスをZ2=R2+j・X2とし、X1とR1の関係を−R1≦X1≦R1、R1をR1=Vdc/Imax・π・{1−cos(θo/2)}/{θo/2−sin(θo)/2}、X2/X1をX2/X1=−{θo/2−sin(θo)/2}/{sin(θo/2)−sin(1.5・θo)/3}に、あるいはそれぞれの近傍にする。

(もっと読む)

高周波用3ステージ窒化ガリウム系高電子移動度トランジスタ(GaNHEMT)ドハティ電力増幅器

【課題】窒化ガリウム系高電子移動度トランジスタ(GaN HEMT)電力素子を用いて広い範囲で高い効率を持つようにした高周波用3ステージ(Three−Stage)GaN HEMTドハティ電力増幅器を提供する。

【解決手段】そのための本発明は、キャリア増幅器及び第1及び第2のピーク増幅器を含む高周波用3ステージ窒化ガリウム系高電子移動度トランジスタドハティ電力増幅器において、前記キャリア増幅器と第1及び第2のピーク増幅器に入力信号を分配するための10dB電力分配器;前記キャリア増幅器の入力電力を調整するための第1の経路部;及び広い出力電力範囲で高い効率を維持させるための第2の経路部を含むことを特徴とする。

(もっと読む)

2段のマイクロ波のE級電力増幅器

【課題】より広い周波数範囲で同時的な高電力と高電力付加効率(PAE)をもたらす改良されたE級増幅器を提供する。

【解決手段】2段のE級の高電力増幅器100は駆動装置段102、E級段間整合ネットワーク(ISMN)104、負荷回路を使用する高電力段106を含んでいる。負荷回路はスイッチングモード回路の出力に結合されている直列の誘導性−容量性ネットワークと、スイッチングモード回路の出力に結合されているキャパシタンスを提供するための回路を含んでいる。

(もっと読む)

集積回路および中継基板

【課題】本発明は、マイクロ波帯やミリ波帯において、1つの集積回路で複数の機能を実現する集積回路と、その集積回路が表面実装される中継基板とに関し、特性の劣化の原因となる広帯域設計をすることなく、多様に異なる帯域に柔軟に対応可能とすることを目的とする。

【解決手段】基板上に個別に形成された複数の回路と、前記基板上で前記複数の回路に隔たって形成され、前記複数の回路の何れにも接続され得る特定の回路とを備え、前記特定の回路と前記複数の回路とは、表面実装型の中継基板との突起電極を介する接続に供されるパッドを有する。

(もっと読む)

集積回路、無線通信ユニット及び電源を供給する方法

無線周波数電力増幅器に電源を供給する集積回路が記載される。当該集積回路は、スイッチング・レギュレータを含む低周波数電源経路と、負荷に結合するための前記集積回路の出力ポートにおいて結合された電源の出力電圧を調整するよう構成された高周波数電源経路とを有する。結合された電源は、前記低周波数電源経路と前記高周波数電源経路とにより供給される。高周波数電源経路は、電圧帰還を含み、前記高周波数電源経路に電源信号を駆動するよう構成された増幅器と、前記増幅器の出力に結合され、前記電源信号のDCレベル・シフトを実行するよう構成されたキャパシタとを有する。  (もっと読む)

(もっと読む)

半導体装置

【課題】携帯電話機などの移動体通信機器に搭載される電力増幅器をバランスアンプから構成する場合に、電力結合器における電力合成の損失を低減することができる技術を提供する。

【解決手段】本実施の形態における技術的思想は、アイソレーション容量素子を、並列接続された対称性の高い2つの容量素子CisoAと容量素子CisoBに分割することにより、容量素子CisoAおよび容量素子CisoBを配線基板の層間容量素子として形成する場合であっても、それぞれの容量素子CisoAと容量素子CisoBに起因する寄生容量をほぼ等しくできる。

(もっと読む)

全二重伝送回路、及び電子機器

【課題】消費電力を低減すること。

【解決手段】送信信号が入力される第1の内部入力端子と、送信信号に比べて振幅が1/2であり、かつ、送信信号と同相の信号が入力される第2の内部入力端子と、特性インピーダンスZを有する伝送路に接続された外部入出力端子と、外部入出力端子から入力された受信信号が出力される内部出力端子と、ソースが電流源及び外部入出力端子に接続され、ゲートが第1の内部入力端子に接続され、ドレインが第2のMOSトランジスタのソース及び内部出力端子に接続された第1のMOSトランジスタと、ソースが第1のMOSトランジスタのドレイン及び内部出力端子に接続され、ゲートが第2の内部入力端子に接続された第2のMOSトランジスタと、を備え、第1及び第2のMOSトランジスタのトランスコンダクタンスが1/Zとなる、全二重伝送回路が提供される。

(もっと読む)

高周波電力増幅器

【課題】高出力、高効率および広ダイナミックレンジを有する低歪みな高周波信号を出力する高周波電力増幅器を提供する。

【解決手段】高周波電力増幅器100であって、増幅用トランジスタ3と、増幅用トランジスタ3の後段に配置された増幅用トランジスタ4と、増幅用トランジスタ3のベースにバイアス電流I1を供給するバイアス回路11と、増幅用トランジスタ4のベースにバイアス電流I2を供給するバイアス回路12とを備え、バイアス回路11は、高周波出力信号の出力電力値が第1電力値のとき第1電流値の電流をバイアス電流I1とし、第1電力値よりも大きい第2電力値のとき第1電流値よりも小さい第2電流値の電流をバイアス電流I1とし、バイアス回路12は、高周波出力信号の出力電力値が第1電力値であるとき第3電流値の電流をバイアス電流I2とし、第2電力値であるとき第3電流値よりも大きい第4電流値の電流をバイアス電流I2とする。

(もっと読む)

増幅回路

【課題】広い入力レベル範囲にわたって高い効率を実現することが可能な増幅回路を提供する。

【解決手段】増幅回路101において、入力側高調波整合回路3および出力側高調波整合回路4により、トランジスタTRの制御電極から前段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスと、トランジスタTRの導通電極から後段側を見たインピーダンスのうち基本周波数の高調波に対するインピーダンスとが、それぞれ、対象信号のレベルが異なる条件下において整合されている。

(もっと読む)

電力増幅器

【課題】 段間に減衰器を設けた構成において、利得切換前後での入力反射損失の劣化を抑制しつつ利得を切り換えることができる電力増幅器を提供する。また、段間に減衰器を設けた構成において、利得切換前後での通過位相差の増大を抑制しつつ利得を切り換えることができる電力増幅器を提供する。

【解決手段】 IN、OUTはRF入力・出力端子であり、Tr1、Tr2はHBT(ヘテロ接合バイポーラトランジスタ)である。Fa1、Fa2はFET(電界効果トランジスタ)である。Cc1、Cc2はデカップリング容量であり、Vc1、Vc2はパワー段Tr1、Tr2のコレクタ電源端子であり、Ra1、Ra2、Raa2、Rg1、Rg2は抵抗であり、Cs1は段間整合容量であり、Cp1は減衰器の並列容量であり、Vg1、Vg2は減衰器の制御端子である。抵抗Ra1に直列に容量Ca1が設けられている。

(もっと読む)

高周波増幅器及び整合回路

【課題】全てのトランジスタに対して最適かつ等位相で高調波を反射させ、高い出力かつ高い効率で動作する高周波増幅器を得る。

【解決手段】FET1Aのドレイン(D)に一端が接続された四角形線路部5A、FET1BのDに一端が接続された四角形線路部5B、並びに四角形線路部5A及び5Bの他端を接続する弓形線路部5Cを有する伝送線路5と、四角形線路部5A及び5Bの間に配置された伝送線路6Bと、四角形線路部5Aに対して伝送線路6Bと反対側に配置された伝送線路6Aと、四角形線路部5Bに対して伝送線路6Bと反対側に配置された伝送線路6Cとを備え、伝送線路6A、6B、6Cの電気長は、高調波の1/4波長であり、伝送線路6A、6B、6Cのそれぞれのビアホール7A、7B、7Cは、伝送線路6A、6B、6Cの一端に接続される。

(もっと読む)

高周波電力増幅装置

【課題】トークカレントの低減を実現可能な高周波電力増幅装置を提供する。

【解決手段】例えば、出力レベルに応じていずれか一方が活性化されるパワーアンプ回路PA2m,PA2sと、伝送線路LNmn,LNsubを備え、LNmn,LNsubが互いに近接配置された領域を持つ。LNsubの他端(PA2sの出力ノード)は、PA2sが活性化された際、NMOSトランジスタMNswのオンに伴い接地電源電圧GNDとの間に容量C3が接続され、PA2mが活性化された際、MNswのオフに伴い開放状態とされる。PA2sが活性化された際、LNmnとLNsubには同一方向の電流が流れるため、強め合う磁気結合が生じる。一方、PA2mが活性化された際、LNmnに流れる電流と、MNswのオフ容量に伴いLNsubに洩れる電流とは反対方向となり、LNmnとLNsubには弱め合う磁気結合が生じる。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力整合回路と、高周波半導体チップの出力側に配置された出力整合回路と、入力整合回路に接続された高周波入力端子と、出力整合回路に接続された高周波出力端子と、高周波半導体チップに接続される平滑化キャパシタ用端子とを備え、高周波半導体チップと、入力整合回路と、出力整合回路とが1つのパッケージに収納された半導体装置。

(もっと読む)

電力増幅器用バイアス回路

【課題】差分周波数Δfが数百MHzにおいても電力増幅器用バイアス回路のリップル電圧ΔVが抑制されてバイアス回路電圧が平滑化され、マイクロ波/ミリ波/サブミリ波帯の高周波に適用可能な電力増幅器用バイアス回路を提供する。

【解決手段】電力増幅器の出力側整合伝送線路のバイアス回路接続点に接続された第1ボンディングワイヤと、第1ボンディングワイヤの終端に接続された第2ボンディングワイヤと、第1ボンディングワイヤの終端に接続されたオープンスタブ伝送線路と、第2ボンディングワイヤの終端に接続されたバイパスリザバーキャパシタとを備える電力増幅器用バイアス回路。

(もっと読む)

電子回路

【課題】分布定数線路の長さの誤差または製造ばらつき等による特性変動を抑制すること。

【解決手段】制御端子と、第1端子と、第2端子と、を有する第1トランジスタT1と、制御端子に前記第1トランジスタの第2端子が接続し、第2端子に直流電源が接続される第2トランジスタT2と、前記第2トランジスタの第1端子から前記第1トランジスタの第2端子に直流電流を供給する、互いに独立した配線からなる複数の直流経路11、12と、前記複数の直流経路内にそれぞれ直列に設けられた分布定数線路L11、L12と、を具備する電子回路。

(もっと読む)

電流共有増幅器を用いた信号増幅

【課題】電流共有増幅器を用いた信号増幅を提供する。

【解決手段】電力増幅器は増幅段を有する。増幅段はトランジスターを有する。また少なくとも1つの増幅段は駆動段を有する。増幅段は、第1のトランジスターと有し及び第1の出力電力と関連付けられた第1の増幅段、並びに第2の出力電力と関連付けられた第2のトランジスターを有する第2の増幅段、を有する。電流共有結合は、第1の増幅段と第2の増幅段を結合する。第1の増幅段と第2の増幅段は、電流共有結合を通じて電流を共有する。電流共有結合は、第1の出力電力と第2の出力電力のスケーリングを助ける。

(もっと読む)

増幅器及び通信装置

【課題】増幅する信号が高周波数帯の信号であっても高効率動作が可能な増幅器を得る。

【解決手段】ドハティ増幅器5は、入力端子10と出力端子11間に2つの並列回路を有し、一方には第1のトランジスタ120を有するキャリア増幅器12、及び入力信号の略4分の1波長の電気長を有する導体線路14が直列に設けられ、他方には導体線路14の位相差に相当する電気長の導体線路15、及び第2のトランジスタ130を有するピーク増幅器13が設けられ、キャリア増幅器12とピーク増幅器13は、出力部124と出力部134が対向するよう配置され、トランジスタ120とトランジスタ130は、伝送する信号の出力方向ベクトルが180degとなるように配置されている。

(もっと読む)

高周波処理回路

【課題】発振抑制用の抵抗を備えながら高周波処理による高効率化を図る。

【解決手段】分配された高周波信号を伝送線路14a,14bの一端の入力部13a,13bに供給し、伝送線路14aは直列接続された伝送線路15aを介して被増幅用高周波信号として出力部16aから次段の増幅用トランジスタに供給する。伝送線路14bは直列接続された伝送線路15bを介して被増幅用高周波信号として出力部16bから次段の増幅用トランジスタに供給する。伝送線路14a,15aの接続点Paに一端を接続したスタブ19aと伝送線路14b,15bの接続点Pbに一端を接続したスタブ19bとの間に発振抑制用の抵抗R1を介挿接続した。接続点Pa,Pbの電位差がない場合は、抵抗R1が見えない状態となり、スタブ19a,19bは高周波信号処理の効率化に寄与し、抵抗R1はセルA,B間のループ発振の抑制させることが可能となる。

(もっと読む)

バイアス回路

【課題】受信雑音性能の低下をともなうことなく簡易な構成により受信用トランジスタを過入力による破壊から防ぐことのできるバイアス回路を得る。

【解決手段】過入力保護回路を有さない受信用増幅器に用いられるバイアス回路であって、受信用増幅器を構成する受信用トランジスタ2のゲート端子に接続されたゲートバイアス回路8と、受信用トランジスタ2のドレイン端子に接続されたドレインバイアス回路9とを備える。ゲートバイアス回路8は、過入力時における受信用トランジスタ2のゲート電流Igまたはゲート電圧Vgの変化を検知して変化信号を生成する変化検知手段を有する。ドレインバイアス回路9は、過入力時の変化信号に応答して、受信用トランジスタ2に対するドレイン電圧Vdを低減させる。

(もっと読む)

41 - 60 / 438

[ Back to top ]