Fターム[5J500AA04]の内容

Fターム[5J500AA04]に分類される特許

21 - 40 / 438

F級増幅回路及びこれを用いた送信装置

【課題】基本波周波数の異なる複数の入力信号が入力する場合でも、各基本周波数に応じた高周波処理が行えるようにする。

【解決手段】 基本角周波数の異なる複数の信号をF級増幅し、該基本角周波数の信号成分及び、その高調波の信号成分を含んだ信号を出力するF級増幅器と、F級増幅器の後段に設けられて、当該F級増幅器に寄生する寄生回路のインピーダンスを取り込んで回路設定されることにより、信号の直流成分及び偶数次高調波の信号成分に対しては短絡状態とし、奇数次高調波の信号成分に対しては開放状態となる高調波処理部と、高調波処理部の後段に設けられて、高調波の信号成分に対しては短絡状態にする短絡部と、を備える。

(もっと読む)

リミッター回路

【課題】接続される低雑音増幅器の破壊を防止すると共に、この増幅器の飽和の範囲を狭くし正常動作の範囲を広くすることが可能なリミッター回路を提供すること。

【解決手段】一例のリミッター回路は、高周波入力端子に接続され、一定の飽和入力電力範囲を有する低雑音増幅器の入力端子と接地との間に接続されたPINダイオードと、前記低雑音増幅器の入力端子に一端を接続され他端は接地される、所定周波数の1/4波長の長さの伝送線路と、前記低雑音増幅器の入力端子に前記飽和入力電力範囲に入る信号が入力されるときに、前記伝送線路の他端と接地との間に、直列接続される電力設定用抵抗器及び定電圧電源を接続し、前記低雑音増幅器の入力端子に入る信号を、この範囲より電力の小さい正常入力電力範囲の信号に下げて前記低雑音増幅器の入力端子に入力する手段と、を有する。

(もっと読む)

変調器およびそれを用いる増幅器

【課題】非線形コンポーネントを有する線形増幅(LINC)変調器による高線形性および高効率の電力増幅器を提供する。

【解決手段】LINC変調器250を有する複合高電力増幅器(C−HPA)200は、ソース信号から複数の定包絡信号を生成する分離器102と、入力信号を受け、前記入力信号の位相軌跡中の位相ジャンプを検知および除去し、連続位相軌跡を有する第一の信号および不連続位相軌跡を有する第二の信号を生成するプロセッサ202a,202bと、前記第一の信号を第二の信号と混合し、前記入力信号を再構成する直交変調器108a,108bと、再構成された信号x1(t)、x2(t)を増幅するHPA1(112a)、HPA2(112b)、増幅された出力信号y1(t)、y2(t)を加え合わせる加算器114、を含む。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

高周波加熱器

【課題】アンテナの負荷インピーダンスによらず、食品を高速に加熱すること。

【解決手段】制御部17で伝送線路15の長さのバラツキの影響を補正することによって、電力増幅器14の出力端での反射係数を高い精度で推測し、さらにその反射係数の値に従って予め用意された参照テーブルをベースにきめ細やかに電力増幅器14への入力電力を過剰に低下することなく制御することによって、高い精度で電力増幅器14の破壊や発振などを防ぎ、アンテナからの高周波出力を高いレベルに維持することが可能となる。

(もっと読む)

非線形特性解析装置及び送信機

【課題】電力増幅器の非線形特性解析の高精度化を図ることのできる非線形特性解析装置を得る。

【解決手段】レベル可変手段3は、2トーン信号発生手段2からの2トーン信号を二つの異なる平均電力レベルに変化させる。2トーン信号の一部を分岐した2トーン信号を入力信号とし、2トーン信号を電力増幅器1で増幅した2トーン信号を出力信号として、非線形特性算出手段9は、これら入力信号と出力信号とから電力増幅器1の動的非線形特性を算出する。非線形特性平均化手段10は、非線形特性算出手段9より算出された動的非線形特性を平均化する。非線形特性合成手段11は、非線形特性平均化手段10で平均化された異なる平均電力レベルの非線形特性を合成して出力する。

(もっと読む)

回路定数調整器及びそれを用いた低雑音増幅装置

【課題】 安定した発振抑制効果が得られると共に高精度に発振が抑制できるように回路定数が調整できるようにする。

【解決手段】 回路定数を調整する回路定数調整器16であって、終端が開放端に形成されたスタブ16eと、一端17bがスタブ16eに接続されると共に、他端17aが回路定数調整対象の回路12に接続され、かつ、抵抗値が設定可能に設けられた可変抵抗器16aと、可変抵抗器16aに制御信号を出力して、当該可変抵抗器16aの抵抗値を設定する抵抗値設定器16cと、を備える。

(もっと読む)

電子回路

【課題】、高出力動作が可能なカレントリユース電子回路を提供すること。

【解決手段】第1端子、第2端子および制御端子を有し、前記第1端子が接地された第1トランジスタT1と、第1端子、第2端子および制御端子を有し、前記制御端子に前記第1トランジスタの第2端子が接続され、前記第1端子が前記第1トランジスタの前記第2端子と高周波的に接続され、前記第2端子に直流電源が接続される第2トランジスタT2と、前記第1トランジスタの第2端子と前記第2トランジスタの制御端子との間のノードに一端が接続され、他端が前記第2トランジスタの第1端子に接続された第1抵抗R1と、を具備した電子回路。

(もっと読む)

増幅装置、送信装置

【課題】出力信号の歪みを抑えつつ効率を向上することのできる増幅装置、送信装置を提供する。

【解決手段】実施形態に係る増幅装置は、飽和出力電力が互いに異なる複数の増幅回路を具備している。実施形態に係る増幅装置は、入力端子に入力された入力信号の包絡線信号を検出する検波器と、前記検波器が検出した包絡線信号の信号電圧を、それぞれ異なる参照電圧と比較する複数の比較器と、前記複数の比較器の比較結果に基づいて前記複数の増幅回路のいずれか一つを選択する切替制御部とを具備している。そして、実施形態に係る増幅装置は、前記入力端子を前記切替制御部が選択した増幅回路の入力に接続するとともに、前記切替制御部が選択した増幅回路の出力を出力端子に接続する切替部とを具備することを特徴としている。

(もっと読む)

ドハティ増幅装置及び通信装置

【課題】ドハティ増幅装置の効率低下を防止する。

【解決手段】ドハティ増幅装置は、メインアンプを構成するメインアンプデバイス1と、ピークアンプを構成するピークアンプデバイス2と、メインアンプデバイス1及びピークアンプ2が実装された基板15とを有している。メインアンプデバイス1は、第1デバイス本体1c、第1入力端子1a、及び、第1出力端子1bを備え、第1入力端子1a及び第1出力端子1bが第1デバイス本体1cを挟んで対向して配置されている。ピークアンプデバイス2は、第2デバイス本体2c、第2入力端子2a、及び、第2出力端子2bを備え、第2入力端子2a及び第2出力端子2bが第2デバイス本体2cを挟んで対向して配置されている。ピークアンプデバイス2は、メインアンプデバイス1の位置に対して、メインアンプデバイス1の第1入力端子から第1出力端子に向かう入出力方向Dsにずれた位置に、実装されている。

(もっと読む)

バイアス回路を一体化した金属酸化膜半導体デバイス

【課題】デバイスの温度変動および/またはプロセス変動に起因するMOSデバイスのバイアス条件の変動を正確に補償できる技術を提供する。

【解決手段】ICデバイスがゲート端子、ソース端子およびドレイン端子を有するMOSデバイスを備え、ゲート端子はICデバイスの入力部に動作可能に結合され、ドレイン端子はICデバイスの出力部に動作可能に結合され、ソース端子は負電圧供給源に結合している。ICデバイスは、さらに、MOSデバイスのゲート端子に動作可能に結合されているバイアス発生器を備え、このバイアス発生器は、MOSデバイスにほぼ一定の静止動作点でバイアスをかけるバイアス電圧および/またはバイアス電流を発生する。バイアス発生器は、バイアス電圧および/またはバイアス電流がMOSデバイスの接合温度の関数として変化するように構成されている。このようにして、バイアス発生器が、MOSデバイスの1つまたは複数の動作条件を正確にたどり、それによってデバイスの性能を向上させる。

(もっと読む)

能動回路

【課題】2倍波処理回路の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得る。

【解決手段】バイアス回路5において、基本波整合回路4の出力側に接続され、基本波周波数成分を全通過させ、2倍波周波数成分を反射するフィルタ回路51と、基本波整合回路4の出力側とフィルタ回路51との間に接続され、基本波周波数で並列共振し、2倍波周波数に対してほぼ純抵抗となる2倍波吸収回路52と、2倍波吸収回路52に接続され、バイアス電圧を供給するバイアス電圧供給回路53とを備えた。

バイアス回路5において、2倍波周波数成分を高周波トランジスタ2側に反射させずに吸収することによって、2倍波処理回路3とバイアス回路5とで並列共振を起こすことがなく、その結果、2倍波処理回路3の動作の阻害を防ぎ、動作効率の劣化を防ぐ能動回路を得ることができる。

(もっと読む)

リニアライザ

【課題】ダイオードから見るインピーダンスが変化しても、利得特性と位相特性の単調変化を実現することができるリニアライザを得ることを目的とする。

【解決手段】アノードが信号路3に接続されて、順方向に電圧が印加されているダイオード15と、アノードが信号路4に接続されて、順方向に電圧が印加されているダイオード16とを備え、ダイオード15のカソードとダイオード16のカソードとの接続点がバイアス接地用ビアホール17に接地されている。

(もっと読む)

半導体装置

【課題】差分周波数Δfが数百MHzにおいても高周波半導体チップのドレイン端面の電圧が平滑化された半導体装置を提供する。

【解決手段】高周波半導体チップと、高周波半導体チップの入力側に配置された入力側分布回路と、高周波半導体チップの出力側に配置された出力側分布回路と、入力側分布回路に接続された高周波入力端子と、出力側分布回路に接続された高周波出力端子と、高周波半導体チップのドレイン端子電極近傍に配置された平滑化キャパシタとを備え、高周波半導体チップと、入力側分布回路と、出力側分布回路と、平滑化キャパシタとが1つのパッケージに収納されたことを特徴とする半導体装置。

(もっと読む)

パルス電力増幅装置

【課題】熱時定数による増幅利得の時間的な変化を補償でき、良好な直線性を有するパルス増幅装置を提供する。

【解決手段】パルス電力増幅装置10は、高周波信号を変調するパルス信号を入力され、前記パルス信号を入力され第1の増幅器の熱時定数に対応する時定数を有する第1の微分回路と、前記パルス信号を入力され第2の増幅器の熱時定数に対応する時定数を有する第2の微分回路と、励振回路及び最終段増幅器の入力側の負バイアス端子に供給される負バイアス電圧を出力する負バイアス電源18と、この負バイアス電源の出力する負バイアス電圧に前記第1の微分回路の出力を加算して前記第1の増幅器の入力側の負バイアス端子に供給する第1の加算回路と、前記負バイアス電源の出力する負バイアス電圧に前記第2の微分回路の出力を加算して前記第2の増幅器の入力側の負バイアス端子に供給する第2の加算回路と、を有する。

(もっと読む)

広帯域マイクロ波増幅器

【課題】クラスEのHPAが広い帯域幅にわたって同時に高いPAE及び電力を維持することを可能にする。

【解決手段】スイッチングモード電力増幅器の出力に結合されたシャント誘導素子と、前記増幅器の前記出力に結合されている直列の誘導素子と、前記直列の誘導素子に結合されている直列の容量素子とを含む構成とした。

(もっと読む)

モジュール

【課題】 平衡型増幅器の性能を損なわず、小型のモジュールを提供すること、他の回路機能とともに複合して無線通信装置の高周波回路部を構成可能なモジュールを提供することを目的とする。

【解決手段】

絶縁体層と導体パターンとを含む多層基板に、一対の増幅器の入力側に第1ハイブリッド回路を出力側に第2ハイブリッド回路を有する平衡型増幅器を構成したモジュールで、 積層方向に連なる複数のビアホールでなるビアホール群を縦列して構成されたシールドによって、前記第1ハイブリッド回路と前記第2ハイブリッド回路とを区画した。

(もっと読む)

高周波回路

【課題】 平衡型増幅器を用いて構成され、挿入損失の増大を抑え、回路の大型化を防ぎながらアンテナダイバシティが利用可能な電気的特性に優れた高周波回路を提供する。

【解決手段】

平衡型増幅器とスイッチ回路を備えた高周波回路であって、前記平衡型増幅器は複数の入力ポートと異なるアンテナと接続される複数の出力ポートを有し、各入力ポート及び各出力ポートとグランドとの間に、スイッチ素子と抵抗とを備えた終端回路を有する。

(もっと読む)

分布定数型増幅器

【課題】分布定数型差動増幅器の出力波形におけるジッタを低減する。

【解決手段】分布定数型増幅器は、複数の増幅器を有する。複数の増幅器はそれぞれ、固有の遅延時間を持って一の信号源からの入力信号を受ける。また、複数の増幅器はそれぞれ、固有の遅延時間に対応する遅延時間をもって共通の負荷に出力信号を提供する。複数の増幅器それぞれに関して、固有の遅延時間と対応する遅延時間の和は等しく設定されている。複数の増幅器のそれぞれは、一対の差動トランジスタと、該一対の差動トランジスタと当該増幅器の出力との間に直列に挿入された一対のカスコードトランジスタを含む。一対の差動トランジスタは、当該一対の差動トランジスタそれぞれのコレクタ−ベース間の接合容量が準飽和領域の接合容量となるように、バイアスされている。

(もっと読む)

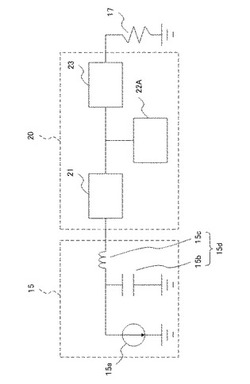

過入力保護回路及び過入力保護方法

【課題】高周波信号を受信するためのモノリシックマイクロ波集積回路で、過入力により保護回路が損傷しても、高周波特性を悪化させずに、回路を保護できるようにする。

【解決手段】過入力保護回路11は、複数段のアンチパラレルダイオード21a及び21bと、各段のFET22a及び22bとを有する。アンチパラレルダイオード21a及び21bは、過入力保護素子として動作する。FET22a及び22bは、各段のアンチパラレルダイオード21a及び21bを、高周波伝送ライン13と接地間に接続又は切り離すスイッチング素子として動作する。アンチパラレルダイオード21aが損傷すると、FET22aが高インピーダンス、FET22bが低インピーダンスの状態となり、初段のアンチパラレルダイオード21aに代わり、次段のアンチパラレルダイオード21bが過入力保護素子として機能する。

(もっと読む)

21 - 40 / 438

[ Back to top ]