Fターム[5J500AA45]の内容

Fターム[5J500AA45]に分類される特許

1 - 20 / 89

コンデンサマイクロホン用インピーダンス変換器およびコンデンサマイクロホン

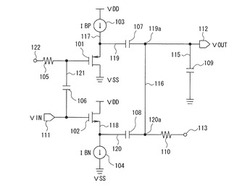

ダブルソースフォロア回路

【課題】電流源によって流れる電流量を増大させることなく、出力信号の立ち上り、立ち下りを高速化することができるダブルソースフォロア回路を提供する。

【解決手段】nMOSFET102を含むソースフォロア回路と、nMOSFET102とは極性が異なるpMOSFET101を含むソースフォロア回路と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路に入力信号を入力する入力端子111と、nMOSFET102を含むソースフォロア回路、pMOSFET101を含むソースフォロア回路から出力信号を出力する共通の出力端子112)と、を含むダブルソースフォロア回路を構成する。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、しきい値電圧や移動度にバラツキが生じてしまう影響を排除する。

【解決手段】アナログ信号を入力するトランジスタ、及び定電流源としての機能を有するトランジスタのゲート・ソース間電圧又はしきい値電圧に応じた電圧を取得、保持し、後に入力される信号電位に上乗せすることで、トランジスタ間のしきい値電圧のバラツキやゲート・ソース間電圧のばらつきをキャンセルする半導体装置を提供する。ゲート・ソース間電圧又はしきい値電圧に応じた電圧の取得、保持には、トランジスタのゲート・ソース間及びゲート・ドレイン間に設けたスイッチ、及びゲート・ソース間に設けた容量を用いる。

(もっと読む)

ソースフォロア回路

【課題】消費電力の増加を抑制しつつ、負荷回路からのキックバックを抑制する。

【解決手段】MOSトランジスタM11と、ゲートおよびドレイン間がダイオード接続されたMOSトランジスタM12と、電流源C11とを直列接続してソースフォロア回路10を構成する。MOSトランジスタM11のゲートに入力された、ソースフォロア回路10への入力信号Vinは、MOSトランジスタM11によりほぼ1倍の利得で出力され、さらに、ダイオード接続されたMOSトランジスタM12でほぼ1倍の利得で出力され、これがソースフォロア回路10の出力信号Voutとして出力されるため、結果的に、1段構成のソースフォロア回路と同様の動作をするが、その消費電力は少なくてすむ。

(もっと読む)

高速入力インターフェース回路

【課題】高周波における入力インピーダンス整合が改善された、広帯域な高速入力インターフェース回路を提供する。

【解決手段】抵抗R1は、その一端が入力端子DTに接続され、他端がインダクタL1を介して第1の電源端子VCCに接続されている。また、抵抗R2は、その一端が入力端子DCに接続され、他端がインダクタL2を介して電源端子VCCに接続されている。また、抵抗R3は、その一端が入力端子DTに接続され、他端がインダクタL3を介して第2の電源端子VEEに接続されている。また、抵抗R4は、その一端が入力端子DCに接続され、他端がインダクタL4を介して電源端子VEEに接続されている。

(もっと読む)

増幅器、液晶表示用駆動回路、及び液晶表示装置

【課題】 入力段及び出力段の電源電位にかかわらず、増幅器の電力消費を抑えつつスルーレートを向上する。

【解決手段】 増幅器は、差動入力端子及び出力端子を有し、前記出力端子が前記差動入力端子の一方に帰還され、前記差動入力端子の他方に入力される入力信号を増幅し前記出力端子から出力するボルテージフォロア回路と、前記ボルテージフォロア回路に所定の電流を供給する第1電流源と、前記差動入力端子の他方と前記出力端子との間の電位差が所定値以上である場合に前記ボルテージフォロア回路に電流を供給する第2電流源と、を備える。

(もっと読む)

半導体装置

【課題】消費電力が低減された半導体装置を提供することである。

【解決手段】入力電位および基準電位が入力される差動増幅器、利得段および出力電位が出力される出力段を有する半導体装置において、該出力段にオフ状態でのリーク電流が低いトランジスタを配置することで、該利得段から供給される電位が一定に保持される半導体装置である。また、オフ状態でのリーク電流が低いトランジスタとしては、酸化物半導体層を有し、且つ酸化物半導体層にチャネル形成領域を有するトランジスタを用いることである。

(もっと読む)

半導体装置

【課題】トランジスタは作製工程や使用する基板の相違によって生じるゲート絶

縁膜のバラツキや、チャネル形成領域の結晶状態のバラツキの要因が重なって、

しきい値電圧や移動度にバラツキが生じる。

【解決手段】本発明は、容量素子の両電極がある特定のトランジスタのゲート

・ソース間電圧を保持できるように配置した電気回路を提供する。そして本発明

は、容量素子の両電極間の電位差を定電流源を用いて設定できる機能を有する電

気回路を提供する。

(もっと読む)

液晶駆動用のソースドライバのオフセット低減出力回路

【課題】 出力アンプのオフセット電圧を適切に低減して表示品質の悪化を防止することができる液晶駆動用のソースドライバのオフセット低減出力回路を提供する。

【解決手段】 基準電圧がオペアンプの非反転入力端に印加されたオペアンプと、少なくとも通常出力動作時にオペアンプの反転入力端に接続される第1の接続点に各々の一端が接続された第1の入力コンデンサ及び第1の出力コンデンサと、リセット動作時に第1の入力コンデンサ及び第1の出力コンデンサ各々の両端を短絡してその両端に基準電圧を印加し、リセット動作後の通常出力動作時に第1の入力コンデンサの他端に階調電圧を印加しかつ第1の出力コンデンサの他端をオペアンプの出力端に接続する第1のスイッチ素子回路と、を備え、第1のスイッチ素子回路は、第1の接続点とオペアンプの出力端との間に接続され、リセット動作時にオンとなり、通常出力動作時にオフとなる直列接続の第1及び第2のスイッチ素子を有し、通常出力動作時には第1及び第2のスイッチ素子の直列接続点に基準電圧を印加する。

(もっと読む)

電子装置

【課題】電力損失を最小限にすることが可能な複数の電源を含む電子装置を提供する。

【解決手段】パワーアンプ40は、入力電圧Viに基づいた出力電圧の電力を被試験体DUTに供給する。検出回路43は、パワーアンプ40の動作電源であるスイッチング電源22から、パワーアンプ40に電流が流れたことを検出する。選択回路51は、電流が流れない場合には、スイッチング電源22の電圧値を所定値に設定し、電流が流れた場合には、スイッチング電源22の電圧値を入力電圧Viより予め定められた値αだけ大きい値に設定する。

(もっと読む)

バッファ回路

【課題】入力信号の交流成分の歪み等の影響をなるべく受けることなく、本来のデューティー比(目標デューティー比)で出力信号を出力することのできるバッファ回路を提供する。

【解決手段】バッファ回路10は、デューティー比検出部16と直流成分生成部17とから構成される負帰還回路部によって、入力信号増幅部15の入出力間で出力信号SOのデューティー比に応じた直流成分の信号を帰還させている。つまり、バッファ回路10は、出力信号SOのデューティー比に応じて、入力信号SI´の直流成分をさらに小さくしたり、大きくしたりする。これにより、バッファ回路10は、出力信号SOのデューティー比を目的デューティー比に変更した上で、その出力信号SOを出力することができる。

(もっと読む)

プリアンプ回路、及びマイクロフォン

【課題】低ノイズ特性を持つプリアンプ回路を提供すること

【解決手段】プリアンプ回路は、ソースフォロアとして機能するPMOSトランジスタM1A及びM1Bを備える。さらにプリアンプ回路は、差動増幅器として対となって機能するPMOSトランジスタM2A及びM2Bを備える。M1AのゲートとM2Bのゲートとが、可変容量C2を介して接続される。M1BのゲートとM2Aのゲートとが、可変容量C1を介して接続される。M1Aのソースと、M2Aのドレインと、が接続される。M1Bのソースと、M2Bのドレインと、が接続される。M2Aのソースと、M2Bのソースと、が接続される。

(もっと読む)

ボルテージレギュレータ

【課題】正確な出力電圧を得る事ができる位相補償回路を有するボルテージレギュレータを提供する。

【解決手段】位相補償回路を出力トランジスタのゲートに接続される第一の定電流回路と、ドレインが出力トランジスタのゲートに接続された第一のトランジスタと、ドレインが第一のトランジスタのゲート及び第二の定電流回路及び抵抗に接続され、ゲートが抵抗及び第一の容量に接続される第二のトランジスタと、もう一方が出力端子に接続される第一の容量で構成する。こうすることで、差動増幅回路の出力端子から第一のトランジスタのドレインへ電流が流れる事を防止することができ、差動増幅回路の入力トランジスタに発生するオフセット電圧が低減され、正確な出力電圧を得ることできる。

(もっと読む)

駆動回路

【課題】消費電流が小さな駆動回路を提供する。

【解決手段】駆動回路76は、入力電位VIよりも所定電圧高い電位をノードN22に出力するレベルシフト回路61と、ノードN22の電位よりも所定電圧低い電位をノードN30に出力するプルアップ回路30と、入力電位VIよりも所定電圧低い電位をノードN27に出力するレベルシフト回路63と、ノードN27の電位よりも所定電圧高い電位をノードN30に出力するプルダウン回路33と、一方電極がそれぞれ信号φB,/φBを受け、他方電極がそれぞれノードN22,N27に接続されたキャパシタ76,77とを備える。入力電位VIの変化時、信号φB,/φBは、それぞれパルス的に「H」レベルおよび「L」レベルになる。したがって、低消費電流化と応答速度の高速化が図られる。

(もっと読む)

差動増幅器及びその制御方法

【課題】オーバーシュートやアンダーシュートを低減し、安定した出力電圧を生成することが可能な差動増幅器を提供すること。

【解決手段】本発明にかかる差動増幅器は、入力信号Vinとフィードバック信号とに応じた1対の信号を出力する差動増幅段回路110と、1対の信号に基づいて出力電圧VOUTを生成する出力段回路120と、を備える。出力段回路120は、外部出力端子と高電位側電源端子との間に設けられ、1対の信号の一方に基づいて抵抗値が制御されるトランジスタ11と、外部出力端子と中間電源端子との間に設けられ、1対の信号の他方に基づいて抵抗値が制御されるトランジスタ12と、外部出力端子と2種類の電源電圧を排他的に切り替えて出力する切り替えスイッチSW3、SW4との間に設けられ、1対の信号の他方に基づいて抵抗値が制御されるトランジスタ15と、2種類の電源電圧として、中間電圧と接地電圧とを備える。

(もっと読む)

抵抗の誤差訂正を用いるコンパレータベースのバッファ

【課題】スイッチトキャパシタの負荷を有する高利得増幅器の駆動容量を高めるコンパレータベースのバッファ方法及びシステムを提供することを目的とする。

【解決手段】電流源と、コンパレータと、スイッチと、サンプリングキャパシタと、オーバーシュート訂正抵抗を含む。充電経路内の抵抗及び訂正位相を使用する訂正の解決法は、電力消費を制約し、コンポーネントを最小化する一方で、出力電圧のオーバーシュートを低減する。Spectre(登録商標)シミュレーションは、本発明の効果を確証する。

(もっと読む)

ソースフォロワ回路、ソースフォロワ型フィルタ回路

【課題】入力MOSトランジスタのオーバードライブ電圧が低い場合でも、出力信号が歪まないソースフォロワ回路を提供することを目的とする。

【解決手段】ソースフォロワ回路を、MOSトランジスタ(Tr)1、Tr2でなるTr対、ドレインがTr1のソース及び出力端子17に接続するTr3、ドレインがTr2のソース及び出力端子18に接続するTr4でなるTr対、ゲートとドレインがTr3のゲートに接続してTr3と電流ミラーを構成するTr7、Tr7のドレインに接続してTr7に電流を供給する電流源9、ゲートとドレインがTr4のゲートに接続してTr4と電流ミラーを構成するTr8、Tr8のドレインに接続してTr8に電流を供給する電流源10、Tr7のゲートと出力端子18との間に接続される容量素子11、Tr8のゲートと出力端子17との間に接続される容量素子12によって構成する。

(もっと読む)

ソースフォロア増幅器

【課題】 入力電圧レベルに関わらず、ソースフォロアトランジスタの閾値電圧を一定に保つことができるソースフォロア増幅器を提供すること。

【解決手段】 入力MOSFETの基板ノードと出力ノードとの間を、入力電位に関わらず、非零の一定電圧に保つ手段を有するソースフォロア増幅器において、上記手段は、入力MOSFETの出力ノードと第1の参照電圧源との間に設けられた第1のスイッチ素子と、該入力MOSFETの基板ノードと第2の参照電圧源との間に設けられた第2のスイッチ素子と、該入力MOSFETの基板ノードと出力ノードとの間に設けられた容量素子であって、入力MOSFETの動作時間の内の、校正時間には該第1及び第2のスイッチ素子を短絡し、使用時間には該第1及び第2のスイッチ素子を開放することを特徴とするソースフォロア増幅器。

(もっと読む)

電圧出力装置

【課題】回路規模の増大を抑制することができ、特に液晶表示パネル等の表示装置の駆動回路への適用に適したオフセット補償機能を備えた電圧出力装置を提供する。

【解決手段】電圧出力装置は、反転入力端子および非反転入力端子を有するオペアンプと、反転入力端子の非反転入力端子への接続、非接続を切替える接続切換手段と、反転入力端子と非反転入力端子の接続時において、オペアンプの反転入力側の負荷抵抗と非反転入力側の負荷抵抗の一方または双方の抵抗値を変化させる負荷抵抗変更手段と、反転入力端子と非反転入力端子を接続した状態において反転入力側の負荷抵抗と非反転入力側の負荷抵抗の一方または双方の抵抗値を順次変化させたときに、オペアンプの出力電圧が変化したときの反転入力側の負荷抵抗と非反転入力側の負荷抵抗の抵抗値を維持させる負荷抵抗設定手段と、を含む。電圧出力装置は、反転入力端子と非反転入力端子の非接続時におけるオペアンプの出力電圧を出力する。

(もっと読む)

出力バッファ回路およびそれを用いたドライバ回路

【課題】 入出力信号が変化する際の過渡期間に出力バッファを構成するトランジスタへのバイアス電流を一時的に増強することで、バッファ回路全体の定常的なバイアス電流を抑制しつつ、高スルーレートが得られるバッファ回路を提供する。

【解決手段】 ドライバ回路200は信号レベル発生回路100により発生した信号SGOを出力バッファ回路110を駆動する回路150(プリバッファ回路)を介し、出力バッファ回路110により伝送線路120を駆動することで測定対象回路DUT140に伝える。プリバッファ回路150とこれを模擬したレプリカバッファ回路160とを互いに並列に備え、信号SGOが変化する際の入出力新信号の過渡期間において、レプリカバッファ回路160の出力電流に基づいて出力バッファ回路110の出力段トランジスタQN12、QP22の入力バイアス電流を一時的に増強する。

(もっと読む)

1 - 20 / 89

[ Back to top ]