Fターム[5J500AA63]の内容

Fターム[5J500AA63]に分類される特許

81 - 100 / 154

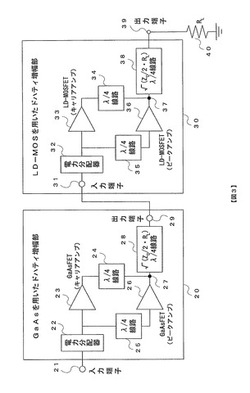

ドハティ増幅回路

【課題】 従来のドハティ増幅回路では、AM−PM特性(振幅−位相特性)の変動が複雑であって、十分な歪補償を行うのが困難であるという問題点があり、本発明は、AM−PM特性を改善し、歪の小さいドハティ増幅回路を提供する。

【解決手段】 互いにAM−PM特性の異なる複数のドハティ増幅部を縦続接続したものであって、例えば、AM−PM特性が逆特性となるGaAsFETを用いた成るドハティ増幅部20と、LD−MOSFETを用いたドハティ増幅部30とを縦続接続したものであり、それぞれのドハティ増幅部で発生する位相変化を相殺して、全体として良好なAM−PM特性を実現し、歪を低減するドハティ増幅回路である。

(もっと読む)

ドハティ増幅器

【課題】簡単な構成で隣接チャネル漏洩電力を抑制しつつ高い効率を得ることができるドハティ増幅器を提供する。

【解決手段】第1電圧とこの第1電圧とは異なる第2電圧とを供給する定電圧源21,22と、増幅部とを備え、増幅部は、入力信号を分配する分配回路11と、定電圧源の第1電圧がドレイン−ソース間に印加され、分配回路により分配された一方の信号を常時増幅するキャリア増幅器1と、定電圧源の第2電圧がドレイン−ソース間に印加され、入力信号が所定レベル以上の場合に分配回路により分配された他方の信号を増幅するピーク増幅器2と、キャリア増幅器の出力とピーク増幅器の出力とが合成されて出力される出力端とを備える。

(もっと読む)

ドハティ増幅器

【課題】変化する入力電力やピーク/平均電力比に対して最適なバイアスを印加するドハティ増幅器を提供する。

【解決手段】アクティブ・バイアス回路では、平均電力検出手段22が入力信号の平均電力を示す電圧値を検出し、包絡線検出手段26が入力信号の包絡線を検出し、しきい値演算手段24が平均電力電圧値に応じて包絡線のしきい値を演算し、電圧制限手段32が包絡線を一定値以下に制限し、これにより、入力信号の平均電力に応じたバイアス電圧を印加する。また、ピークホールド手段27が包絡線の最大電圧値を保持し、差演算手段28が包絡線最大電圧値と平均電力電圧値との差を演算し、電圧制御増幅器30が演算された電圧値を制御電圧として増幅率を変化させて包絡線を増幅し、これにより、入力信号のピーク/平均電力比に応じたバイアス電圧を印加する。

(もっと読む)

電力増幅器

【課題】アクティブバイアスを用いたドハティ増幅器において、電力効率がよく、且つ非線形歪が小さく、更に、出力信号の状態に応じた精度の高い歪補償を行うことができる電力増幅器を提供する。

【解決手段】バイアス制御部14が、入力電力に応じてバイアス制御テーブルを参照してドハティ増幅部13のピーク増幅器のゲート電圧を制御し、バイアス制御テーブルが、入力電力が小さい場合にC級にバイアスし、入力電力が大きい場合にAB級にバイアスするよう入力電力とゲート電圧とが対応付けられており、歪検出部16が、ドハティ増幅部13の出力信号中の非線形歪の電力を検出し、制御部17が、非線形歪の電力に基づいてバイアス制御テーブルを適応的に更新する。

(もっと読む)

増幅器

【課題】 高効率ドハティ増幅器の入力分配器の分配損によるゲイン低下を防止して高ゲインを図り、高次歪の増加を抑えて高次歪を低減できる増幅器を提供する。

【解決手段】 AB級で動作するキャリア増幅回路4とB級又はC級で動作するピーク増幅回路5からの出力をノード62で合成出力するものであって、分配器2で分配された信号に対して伝送線路33で線路の長さが調整されて低入力時の反射係数を変更し、キャリア増幅回路4からの信号をインピーダンス変換器64でインピーダンス変換し、ピーク増幅回路5からの信号について伝送線路65で損失がないよう低入力時のインピーダンスを大きくみせ、低入力時に、分配器2からピーク増幅回路5側の入力インピーダンスを無限大に近づけることで、低入力時の利得を上げる増幅器である。

(もっと読む)

高周波電力増幅回路

【課題】パルス動作により間歇的に高周波電力増幅を行う、高周波用のパワーMOS・FETを用いた高周波電力増幅回路において、ゲートパルスによるバイアス電圧の掛け方を工夫することで、パワーMOS・FETの出力パルス幅を拡げて、かつ安全性の高い動作を期待できる、経済的に有利な回路構成とした。

【解決手段】波形成形回路20は、ゲートパルス入力端21に入力されたゲートパルスGP(in)を出力電位が漸減する所定幅のゲートパルスGP(out)に成形して、増幅回路10のパワーMOS・FET12,13のゲート電極(G)に供給する。

(もっと読む)

動作電力の広い範囲にわたるオンチップIM3低減のためのシステムおよび方法

数組の電力増幅器のブランチは、各増幅段内で電力合成され、各組のブランチは、異なるインピーダンス特性を持つバイアス回路によって、動作の異なる級にバイアスされる。その結果、電力レベルのある範囲にわたり、出力に存在する基本周波数成分は互いに同位相になり、IMD3成分は逆位相になる。RF入力信号は前段の出力により供給され、各段は数組の電力増幅器のブランチを電力合成することにより構成される。各ブランチは、IM3成分は部分的にまたは完全にキャンセルする一方で、基本波成分は付加的になるように、個別にバイアスされる。フィードフォワード制御ループを使用して入力電力を監視すること、および個々のブランチに給電する前記バイアス回路のバイアス電流とインピーダンス特性を適切に調整することにより、出力電力の広い範囲にわたって、更なるIM3の低減、または、キャンセルを提供することができる。  (もっと読む)

(もっと読む)

高周波電力増幅回路

【課題】経済的に有利な構成の高周波電力増幅回路を提供する。

【解決手段】高周波用パワーMOS・FET11がゲート−ドレイン間ショートの故障モードに陥り、電圧制限用バリスタ13に設定電圧を超える高電圧が印加されたとき、電圧制限用バリスタ13は印加された過剰電圧分を放電する。この放電電流により過電流保護ヒューズ14がゲート電極(G)−ゲートパルス入力端(Tgb)間の電流路を遮断する。

(もっと読む)

ドハティ増幅器

【課題】変化する入力電力やピーク/平均電力比に対して最適なバイアスを印加するドハティ増幅器を提供する。

【解決手段】アクティブ・バイアス回路では、平均電力検出手段22が入力信号の平均電力を示す電圧値を検出し、包絡線検出手段26が入力信号の包絡線を検出し、しきい値演算手段24が平均電力電圧値に応じて包絡線のしきい値を演算し、電圧制限手段32が包絡線を一定値以下に制限し、これにより、入力信号の平均電力に応じたバイアス電圧を印加する。また、ピークホールド手段27が包絡線の最大電圧値を保持し、差演算手段28が包絡線最大電圧値と平均電力電圧値との差を演算し、電圧制御増幅器30が演算された電圧値を制御電圧として増幅率を変化させて包絡線を増幅し、これにより、入力信号のピーク/平均電力比に応じたバイアス電圧を印加する。

(もっと読む)

電力増幅装置および携帯電話端末

【課題】比較的大きいピークファクタを有する信号に対して比較的簡単な構成で歪みや効率の問題を解決する。

【解決手段】第1の電力増幅器10はA級またはAB級動作にバイアス設定され、入力信号を増幅する。第1の電力増幅器10の出力が出力端sigoutに接続される。第2の電力増幅器20は、入力信号の一部を分岐して入力とし、C級動作にバイアス設定され、入力信号を増幅する。この第2の電力増幅器の出力にスイッチ30の一端子が接続され、他方の端子に出力端子sigoutが接続される。この出力端子sigoutに第1の電力増幅器20の出力が接続される。

(もっと読む)

RF電力増幅器

【課題】低出力電力時にも高出力電力時にも高電力付加効率の特性を示すRF電力増幅器を提供すること。

【解決手段】RF電力増幅器は、入力端子RF_Inと出力端子RF_Outの間に並列接続の最終段増幅パワー素子としての第1と第2の増幅素子Q1、Q2とを含む。Q1とQ2とは、1つの半導体チップ上に形成されている。Q1がB級からAB級までのいずれかの級で動作しQ2が未満のC級で動作するように、Q1の第1バイアス電圧Vg1は、Q2の第2バイアス電圧Vg2よりも高い。Q1の第1実効素子サイズWgq1は、Q2の第2実効素子サイズWgq2よりも半導体チップの製造誤差以上に意図的に小さく設定されている。

(もっと読む)

歪制御機能付き増幅装置

【課題】ドハティ増幅器と歪補償器を組み合わせた場合の歪補償量をABクラス増幅器の歪補償量に近付けることができる歪制御機能付き増幅装置を提供する。

【解決手段】キャリア増幅回路及びピーク増幅回路を備えたドハティ増幅器20とプリディストータ102を組み合わせてドハティ増幅器20の非線形歪を補償する。ドハティ増幅器20の入力信号を方向性結合器162及び検波回路163で検出し、A/D変換器164を介して制御部117に入力する。又ドハティ増幅器20の出力信号に含まれる相互変調歪を歪検出部112で検出して制御部117に入力する。制御部117は、歪検出部112で検出された歪値が小さくなるようにプリディストータ102を制御すると共に、歪検出部112で検出された歪値及びA/D変換器164の出力に応じてピーク増幅回路のバイアスを任意に制御し、ドハティ増幅器20のAM−AM変換特性がAB級に近付くようにする。

(もっと読む)

増幅器制御装置

【課題】バースト性を持つ信号を増幅するアンプにおいて、その信号のオン・オフ時に発生する歪を無くす。

【解決手段】バイアス制御信号生成部1は、バースト情報に基づき、アンプ2に入力されるバースト性を持つ送信信号のON、OFFを検知する。バイアス制御信号生成部1は、アンプ2に流れるアイドル電流が、送信OFFの期間には多めに、送信ONの期間には通常時のレベルに戻るように、アンプ2に加えるバイアス電圧を制御する。

(もっと読む)

結合型零入力電流及びコモンモード制御を有するクラスAB増幅器回路

【課題】安定なコモンモード電位及び安定な増幅特性を有する差動出力信号を供給する増幅器回路を提供する。

【解決手段】出力トランジスタ(T1−T4)を介して流れる零入力電流と差動出力信号のコモンモード電位の結合した制御のために本増幅器回路の制御段へフィードバックする制御経路(24,26,30,28)と(36,38,34,32)を設ける。別個の制御ループ間における如何なる不利益的に作用する結合も、1つの且つ同一の制御経路における2つの制御機能のこの結合によって有益的に回避される。

(もっと読む)

分散型G級タイプ増幅器の切り換え方法

電力レールに対する入力信号の瞬間振幅に応じて複数の電力レール間で切り換える改良型G級増幅器。低電圧(内側)増幅器が、複数の並列増幅器デバイスを含み、高電圧(外側)増幅器が、複数の並列増幅器デバイスを含む。複数のスイッチそれぞれが、入力信号を、内側増幅器デバイスのうちのそれぞれの増幅器、又は外側増幅器デバイスのうちのそれぞれの増幅器に結合する。スイッチは順次活動化され、その結果、内側増幅器デバイスから外側増幅器デバイスへの、又は逆のスイッチングが、何らかの時間にわたって互い違いにされる。これにより、単一の大きなグリッチを出力内に有することが回避され、複数の、より小さなグリッチが十分な時間にわたって分散され、その結果、グリッチ・エネルギーの一部は、増幅器の帰還回路がそのノイズを解消することができる周波数範囲内に入ることができる。スイッチは、一連の遅延要素によって順次活動化される。  (もっと読む)

(もっと読む)

増幅器ユニット及びその故障検出方法

【課題】増幅器ユニット及びその故障検出方法に関し、ピーク増幅器の故障を簡易な構成で確実に検出してドハティ増幅器の故障を検出することができるようにし、また、ドハティ増幅器型の増幅器ユニット全体の故障も簡易な構成で検出できるようにする。

【解決手段】ピーク増幅器1−4のトランジスタデバイスのゲートバイアス電圧を、故障検出回路1−6において所定の閾値と比較し、該比較して得られる信号を基に故障の有無を示す信号を出力する。また、キャリア増幅器1−3を少なくとも含む増幅器ユニット内の増幅器の総合利得を検出する利得検出回路1−5の出力信号を故障検出回路1−6に入力し、該故障検出回路1−6はピーク増幅器1−4のゲートバイアス電圧異常及び利得検出回路1−5の利得低下を示す信号を基に、増幅器ユニットの故障の有無を示す信号を出力する。

(もっと読む)

ドハティ増幅器

【課題】ドハティ増幅器において、効率を確保しつつ、線形性を改善すること。

【解決手段】ドハティ増幅部130に並列に非線形増幅部140が設けられて、インピーダンス変換器150を経由したドハティ増幅部130の出力信号と、非線形増幅部140の出力信号とが合成器160によって合成され、合成後の出力信号が出力端子170から出力される。このとき、非線形増幅部140は、ドハティ増幅部130が非線形動作する領域で、その非線形性を補充して線形性を保つように増幅動作するようにしたので、ドハティ増幅器100は、広い領域にわたり線形増幅することができるようになる。

(もっと読む)

増幅器及びこれを用いた駆動回路

【課題】極性反転時にトランジスタのオン抵抗の低下を抑制して、貫通電流を低減し、スルーレートの低下を抑制する。

【解決手段】本発明の一態様に係る増幅器は、電源端子VDD及び接地端子GNDとの間に直列に接続されたMOSトランジスタ14及び15と、MOSトランジスタ14、15の間のノードに接続された出力端子Voutと、MOSトランジスタ14のゲートと出力端子Voutとの間に設けられた第1のミラー容量31と、MOSトランジスタ15のゲートと出力端子Voutとの間に設けられた第2のミラー容量32と、第1のミラー容量31の一端を電源端子VDDあるいはMOSトランジスタ14のゲートに接続する第1のスイッチング回路4と、第2のミラー容量32の一端を接地端子GNDあるいはMOSトランジスタ15のゲートに接続する第2のスイッチング回路5とを有する。

(もっと読む)

送信機

【課題】PAPRを低減可能な技術の提供。

【解決手段】電力増幅される入力信号から、第1のクリッピングレベルに基づく振幅レベルより高い振幅部分を切り取る第1クリッピングを行う第1リミッタと、第1クリッピングが行われた後の第1の信号から、第2のクリッピングレベルに基づく振幅レベルより低い振幅部分を切り取る第2クリッピングを行う第2リミッタと、第2クリッピングが行われた後の第2の信号を振幅変調部分と定振幅部分とに分離する分離部と、前記振幅変調部分を増幅する第1増幅器と、前記定振幅部分を増幅する第2増幅器と、前記第1増幅器で増幅された振幅部分と前記第2増幅器で増幅された定振幅部分とを合成した第3の信号を出力する合成器とを含む送信機である。

(もっと読む)

演算増幅器

【課題】電源電圧の低電圧化においても安定した高利得の演算増幅器を提供することを目的とするものである。

【解決手段】AB級演算増幅器100では、出力段5を構成するトランジスタM17、M18の閾値電圧を、前記出力段5に接続されたカスコード接続段3、4を構成するトランジスタの飽和ドレイン電圧の和よりも高くすることにより、低電源電圧においてAB級演算増幅器100を構成する全てのトランジスタを飽和領域内で動作させる。

(もっと読む)

81 - 100 / 154

[ Back to top ]