Fターム[5J500AA63]の内容

Fターム[5J500AA63]に分類される特許

121 - 140 / 154

ドハティ型増幅器

【課題】 従来のドハティ型増幅器においては、高効率特性と低歪み特性との両立が困難であった。

【解決手段】 ドハティ型増幅器1は、入力端子72と出力端子74との間の経路P1(第1の経路)中に設けられ、第1の級にバイアスされるメインアンプ10(第1の増幅器)と、経路P1と並列する経路P2(第2の経路)中に設けられ、第1の級とは異なる第2の級にバイアスされるピークアンプ20(第2の増幅器)と、経路P1におけるメインアンプ10の出力側に設けられた波長線路32と、を備えている。ここで、AB級バイアス時のFET12(第1のトランジスタ)のアイソレーションは、C級バイアス時のFET22(第2のトランジスタ)のアイソレーションよりも大きい。

(もっと読む)

増幅器

常に信号の増幅動作を行うキャリア増幅器と、高電力出力時のみに動作するピーク増幅器と、キャリア増幅器とピーク増幅器の出力を合成して出力する合成器と、入力信号をキャリア増幅器側とピーク増幅器側に分配する分配器とを含んで構成される。キャリア増幅器およびピーク増幅器は1個のパッケージ1(1パッケージトランジスタ)に内蔵される。  (もっと読む)

(もっと読む)

送信機

【課題】 出力変調波形に歪みが生じない、高効率のEER法の送信機を提供する。

【解決手段】 変調信号を振幅成分と位相成分に分離し、高周波電力増幅器110の高周波入力端子および電源電圧端子から入力するEER法の送信機において、高周波電力増幅器110の2段以上のアンプ108,109で合成される位相成分と振幅成分が最適に合成されるようにそれぞれに遅延時間を補正できる遅延時間補正手段104を設けた構成とする。その結果、各段のアンプ108,109において合成誤差を低減し、出力波形の歪み成分を低減することができる。

(もっと読む)

増幅器

【課題】AM−PM歪みを効果的に抑制することができ、小型で低コストの増幅器を提供する。

【解決手段】ドハーティ増幅器において、入力分配回路2の前段に前置歪み補償回路7が、また、ピーク増幅器4の前段に、置歪み補償回路9が夫々設けられている。入力端子1からの入力信号は、入力分配回路2により、キャリア増幅器3とピーク増幅器4とに分配され、キャリア増幅器3が飽和するまでは、キャリア増幅器3のみで増幅され、キャリア増幅器3が飽和すると、入力信号のキャリア増幅器3が飽和するレベル以上のピーク部分がピーク増幅器4で増幅されるが、キャリア増幅器3で生ずるAM−PM歪みは前置歪み補償回路7で補償され、ピーク増幅器4で生ずるAM−PM歪みは前置歪み補償回路7と前置歪み補償回路9とで補償される。

(もっと読む)

電力増幅器

【課題】高周波入力電力や制御電圧の変動、又は、温度の変動によるバイアス電流の変動を確実に補償し、安定性の高い増幅動作を確保する。

【解決手段】第1のトランジスタ1のベースへの高周波入力電力の変動や、第2のトランジスタ2のコレクタへ外部から印加される制御電圧の変動などにより、第1のトランジスタ2のベース電流が減少、又は、増加すると、第3のトランジスタ3のベース電位の変化によって、第1の抵抗器11を流れる電流とpnダイオード5を流れる電流が変化し、その電流変化によって第2のトランジスタ2のベース電位が、そのコレクタ電流、すなわち、第1のトランジスタ1のベース電流を増加させるよう変化を受けるようになっており、ベース電流の変動に対して充分な補償がなされるものとなっている。

(もっと読む)

多段モジュールを用いた高電力ドハティ増幅器

高電力ドハティRF増幅器は、それを構成する主増幅器とピーク増幅器の双方に、多段増幅器モジュールを用いている。2方路2段の実施形態では、おのおのの増幅器モジュールの初段に、信号プリディストーション機能を含み、それにより初段と次段の歪を補償することができる。設計は簡単で、高利得で高効率な増幅器が可能である。1つの実施形態では、主増幅器とピーク増幅器の双方に、市販のCREE PFM19030SM電力モジュールが用いられている。  (もっと読む)

(もっと読む)

AB級増幅器

【課題】比較的小さいアイドル電流でも良好な応答性を示すAB級増幅器を比較的小さな回路規模で実現する。

【解決手段】AB級増幅器は、差動入力電圧を増幅する入力増幅部(10)、入力増幅部10の電流出力を増幅する出力増幅部(20)、差動入力電圧に応じて入力増幅部(10)のゲインを制御するゼロゲイン補償部(40)を備えている。ゼロゲイン補償部(40)は、差動入力電圧に基づいて、差動入力電圧がゼロのときを中心とする上に凸の電流を生成し、これを入力増幅部(10)のバイアス電流として供給する。

(もっと読む)

低電圧AB級トランスコンダクタ回路

AB級トランスコンダクタ回路が、ソース−ドレイン経路を第1及び第2電圧供給源レイル(14、16)間に直列に接続させている相補型PMOS及びNMOSトランジスタ(10、12)を有する。出力端子(20)は、前記直列接続されたソース−ドレイン経路の接続点に結合される。前記PMOS及びNMOSトランジスタのゲート電極は、第1及び第2バイアス電圧供給源(32、34)を夫々に含む第1及び第2経路を用いて入力端子(18)に結合される。前記PMOS及びNMOSの静止ゲート電圧は、当該静止入力電圧から前記第1及び第2バイアス電圧供給源の等しく且つ反対である電圧(Vb)だけオフセットされ、これにより、前記バイアス電圧供給源の前記値だけ前記PMOS及びNMOSトランジスタの見掛けのしきい値電圧(Vt’)を低下する。また平衡AB級トランスコンダクタ回路も開示される。  (もっと読む)

(もっと読む)

クラスAB増幅器のための同期温度保護

本発明は、帯域幅制御信号に基づく帯域幅制御が備えられた集積化増幅器用の同期回路に関し、前記同期回路は、制御信号用の制御端子と、内部制御信号に接続され、前記内部制御信号が、前記制御信号と比べて所定のランキング基準に従ってより高いランクを有する場合、前記内部制御信号を、前記制御端子に対してエンボス(emboss)するように構成されているランクセレクタ手段と、を備える。さらに、本発明は、複数の回路向けの共通制御信号を連続的に通信および同期するための、それぞれの同期方法に関する。本発明の1つの好適な適用は、増幅器ごとに1つのみの追加の端子ピンによる、複数のクラスAB増幅器のための、同期された帯域幅制御による温度保護にある。このような複数チャンネル増幅器構成において、最も高温な増幅器は、帯域幅削減の量を決定(dictate)する。本発明によって、個別の増幅器は、それぞれの個別の温度について通信を行うことができ、これにより、実際の最も高温な増幅器の温度およびそれぞれの必要な帯域幅削減が決定され、同期された帯域幅削減のために、それぞれの個別の増幅器に提供される。よって、3チャンネルRGB増幅器において、信号の完全性が有利に維持される。  (もっと読む)

(もっと読む)

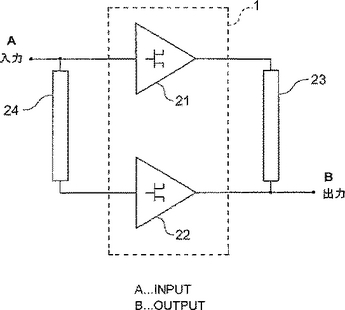

増幅器

【課題】 ドハチィ増幅器を高利得化したときの電源効率を改善する。

【解決手段】 AB級で動作する増幅回路4と、BまたはC級で動作する増幅回路5と、増幅回路4から伝送線路64を経由して増幅回路5の出力を合成する合成点62を有する回路を備えたドハチィ増幅器において、増幅回路4及び増幅回路5の前段にAB級とC級のプリアンプ91、92を設けて増幅器全体の効率を向上させた。これにより、ドハチィ増幅器の前に共通のプリアンプを接続するよりも、分配に係る損失の絶対レベルが減るので、高効率かつ低歪となる。

(もっと読む)

非対称電力駆動を用いた電力増幅装置

【課題】非対称電力駆動を用いて高効率を維持しながら最適の線形性を達成するドハーティ増幅器を提供する。

【解決手段】非対称電力駆動器500,伝送ライン502,互いに並列に連結されているキャリア増幅器504及びピーク増幅器506、オフセットライン508,第1λ/4伝送ライン510,及び第2λ/4伝送ライン512から構成される。

(もっと読む)

高周波用のドハティ型の高効率増幅器、およびその信号処理方法

【課題】 正確なリニアリティが得られる高周波用の高効率増幅器、およびその信号処理方法を実現する。

【解決手段】 メインアンプ1にピーキングアンプ2の出力を合成して出力するドハティアンプにおいて、レベル比較器8は、入力信号と出力信号の信号レベルを測定して利得のリニアリティを調べ、入力信号のレベルが変化しても利得が一定になる制御をするバイアス信号を振幅制限器4を介してピーキングアンプ2へ出力する。

(もっと読む)

ドハティ増幅器

【課題】 回路規模を増大させたり製造コストを高くすることなく、電力効率の高効率化及び高線形化を実現することができるドハティ増幅器を提供する。

【解決手段】 入力端子から入力されたRF信号は分配器1によって2つの経路に分配される。入力電力が少ないときはキャリア増幅器2のみによって線形増幅が行われて増幅されたRF信号の電力は出力端子より送出される。入力電力が所定の値より多くなると、キャリア増幅器2及びピーク増幅器6によって増幅された電力が合成器9で合成されて出力端子より送出される。このとき、ピーク増幅器6の前段の位相調整器5と後段のインピーダンス変換器8とにより、キャリア増幅器2からみた負荷インピーダンスRLをN−Wayドハティ増幅器のように減少させて電力増幅の最適動作を行わせる。これによって、ドハティ増幅器における電力増幅効率の高効率及び高線形化を実現することができる。

(もっと読む)

AB級CMOS出力回路

【課題】低電圧回路においてAB級CMOS出力回路のバイアス回路を実現する。

【解決手段】PMOSFETP10と、NMOSFETN10とからなり半導体基板上に形成され、動作電流I0により動作させるCMOS回路を備えたCMOS出力回路である。PMOSFETP10と実質的に同一又は相似のサイズを有するPMOSFETP11と、NMOSFETN10と実質的に同一又は相似のサイズを有するNMOSFETN11とを形成してレプリカ回路4を形成する。レプリカ回路4のPMOSFETP11及びNMOSFETN11を、動作電流I0に対応した基準電流Irefに基づいて動作させ、PMOSFETP11のゲートに印加されるバイアス電圧をPMOSFETP10のゲートに印加し、NMOSFETN11のゲートに印加されるバイアス電圧をNMOSFETN10のゲートに印加する。

(もっと読む)

増幅器

【課題】適切な整合を取ることにより従来のドハチィ増幅器以上の性能を得る。

【解決手段】AB級で動作するキャリア増幅回路4と、BまたはC級で動作するピーク増幅回路5と、キャリア増幅回路4からインピーダンス変換器64を経由して増幅回路5の出力を合成する合成点62を有する。伝送線路の長さを0〜λ/2の範囲で最適化して設定する事により、増幅素子52が動作しない時の増幅素子42から見たインピーダンスを、ほぼ最大出力が得られる時のインピーダンスから、任意の値へ遷移させることができる。また、キャリア増幅回路4とピーク増幅回路5のそれぞれをプッシュプル構成にしてもよい。

(もっと読む)

ドハティアンプ

【課題】 広い周波数帯域に渡って、線形性に優れ、高効率の動作が可能なドハティアンプを提供する。

【解決手段】 ドハティアンプにおいて、入力電力検出回路113,114および、ピークアンプ102の出力側に、可変容量ダイオード115とλ/4線路108を付加し、検出された入力電力にしたがって可変容量ダイオード115の容量値を変化させ、出力合成部110からピークアンプ102を見たインピーダンスを実質的にオープンにする。

(もっと読む)

高周波ドハティ増幅器

【課題】 分配ロスを発生せず、高利得を得ることが可能な高周波ドハティ増幅器を提供すること。

【解決手段】 バラン102は、入力された高周波信号の電力が所定値未満の場合には、高周波信号を主増幅器102のみに出力し、一方、電力が所定値以上の場合には、高周波信号を主増幅器103と補助増幅器104に分配して出力するようにインピーダンスが調整される。主増幅器103及び補助増幅器104は、バラン102から入力された高周波信号を増幅する。バラン105は、主増幅器103から増幅されて出力された高周波信号と、補助増幅器104から増幅されて出力された高周波信号を合成する。

(もっと読む)

電力増幅回路および電力増幅器

【課題】 歪のない安定した出力を得られる安価な電力増幅回路および電力増幅器を提供する。

【解決手段】 NチャンネルFET1のソースとNチャンネルFET2のドレインを共通接続し、この接続点に負荷3を接続するとともに、NチャンネルFET1のドレインに正極性電源、NチャンネルFET2のソースに負極性電源を接続したものであって、NチャンネルFET1のソースとNチャンネルFET2のドレインの接続点の負荷3への出力を基準として、NチャンネルFET1のゲートを制御する第1の駆動回路17と、負極性電源を基準として、NチャンネルFET2のゲートを制御する第2の駆動回路18を有する。

(もっと読む)

カスコード形態のクラスAB制御端を備える差動増幅回路

【課題】 カスコード形態のクラスAB制御端を備える差動増幅回路を提供する。

【解決手段】 入力回路、出力回路及び制御回路を備える差動増幅回路である。入力回路は、入力信号の電圧差に応答して差動電流を発生させる。出力回路は、出力ノードで出力信号を発生させる。制御回路は、入力回路と出力回路との間に連結され、静止電流を利用して出力回路をバイアスする少なくとも二つのトランジスタのカスコード連結を有するフローティング電流源を備える。フローティング電流源は、入力信号間の電圧差が0である場合、静止電流を利用して出力回路をバイアスする。これにより、差動増幅回路は、従来の差動増幅回路に比べて、クラスAB動作を制御するフローティング電流源のトランジスタがカスコード構造を有することにより、差動増幅回路の直流利得が増加する。また、直流利得の増加により、差動増幅回路のオフセットが減少する。

(もっと読む)

インピーダンス制御可能なバイアス昇圧回路を有する増幅回路

増幅回路(1)は、増幅トランジスタ(QO)と、少なくとも約180度の導電角度を得るため増幅トランジスタ(QO)をバイアスするためのインピーダンス制御可能な直流バイアス回路(2)とを有する。直流バイアス回路(2)は、潮流バイアス回路(2)の出力インピーダンスおよび増幅トランジスタ(QO)の静止電流を独立して制御するための別々の電流源(Ibias、Iclass)を備える自己バイアス昇圧回路を備えると共に、拡張ウィルソン電流ミラー回路(Q2〜Q8)を形成するためにカスコード電流ミラー回路(Q2、Q3、Q8)に統合されたウィルソン電流ミラー(Q4、Q5、Q6、Q7)を有するウィルソン電流ミラーを有し、拡張ウィルソン電流ミラー回路はレジスタ(R1)により増幅トランジスタ(QO)の制御回路に結合される出力と、拡張ウィルソン電流ミラー(Q2〜Q8)から共通端子(Gnd)への間に結合されたキャパシタ(C2)とを有する。  (もっと読む)

(もっと読む)

121 - 140 / 154

[ Back to top ]