Fターム[5J500AC11]の内容

Fターム[5J500AC11]の下位に属するFターム

Fターム[5J500AC11]に分類される特許

1 - 20 / 43

バイアス回路およびそれを有するアンプ回路

【課題】増幅トランジスタのトランスコンダクタンスgmの変動を抑制する。

【解決手段】バイアス回路は,第1のドレイン電流を生成する第1のトランジスタと,第2のドレイン電流を生成する第2のトランジスタと,直列に接続された複数の抵抗素子を有し,複数の抵抗素子に前記第2のドレイン電流と第1のドレイン電流の差電流が供給され,複数の抵抗素子間の複数のノードにそれぞれ対応する電圧を生成する抵抗回路とを有する。そして,抵抗回路の第1のノードの第1の電圧が第1のトランジスタのゲートに印加され,第2のノードの第2の電圧が第2のトランジスタのゲートに印加され,第1,第2のノードと異なる第3のノードの第3の電圧がバイアス電圧として出力される。

(もっと読む)

定電圧発生回路

【課題】定電圧発生回路の回路面積及び消費電流を削減しながら、負荷の直流的及び過渡的な変化に対する出力電圧の変化を小さくする。

【解決手段】FET4は、電圧源端子に接続されたドレインと出力端子に接続されたソースとを備える。FET2は、FET4のソースに接続されたゲートと、FET4のゲートに接続されたドレインとを有する。FET1は、FET2のソースと接地端子との間に設けられ、ダイオード接続されている。FET3は、電圧源端子とFET2のドレインとの間に接続され、そのドレインとソースとの間に所定の電位差を有し、第1の定電流源として機能する。FET5は、出力端子と接地端子との間に接続される。FET1及びFET5によりカレントミラー回路を構成することにより、FET5は第2の定電流源として機能する。

(もっと読む)

増幅回路

【課題】受光素子(フォトダイオード)の出力信号を増幅する初段増幅器を有する増幅回路において、初段増幅器の増幅率を大きくする。

【解決手段】フォトダイオード2で光電変換された電気信号を増幅する初段増幅器31の出力信号に含まれる直流成分をローパスフィルタ34にて抽出し、その抽出した直流成分を打ち消すように、初段増幅器31の入力側にバイアス電流を帰還する。このようにして初段増幅器31の入力側にバイアス電流を流すことによって、初段増幅器31に入力される電気信号の直流成分(照明光等の信号成分)を除去することができ、初段増幅器31の増幅率を大きくすることが可能になる。

(もっと読む)

信号変換装置及び信号変換方法

【課題】ADCのSNRを向上し、かつ、マイクロフォン用IC全体の歪み特性の劣化を最低限に抑えること。

【解決手段】本発明にかかる信号変換装置は、入力アナログ信号を増幅して出力するプリアンプ回路と、入力クロックのサイクルに応じて、プリアンプ回路からの出力に基づくアナログ信号をデジタル信号へ変換するAD変換器と、入力クロックの周波数に応じて、デジタル信号へ変換される前のアナログ信号である変換前アナログ信号の調整を制御する調整制御回路と、を備える。

(もっと読む)

フィルタ回路

【課題】 歪特性に優れるフィルタ回路を得る。

【解決手段】 直列に接続された複数のLPFを有するフィルタ回路において、複数のLPFはそれぞれ、スイッチトキャパシタ回路SC、および、SCの出力信号を増幅して出力する全差動型増幅器AMPを有する。1ビットDAC40の出力信号が入力されるLPF1が有するAMP10のコモンモードフィードバック回路は離散時間型であり、フィルタ回路としての出力信号を出力するLPF2が有するAMP20のコモンモードフィードバック回路は連続時間型である。

(もっと読む)

送信器

【課題】電力増幅器を高効率化及び高信頼性化する。

【解決手段】一つの実施形態によれば、送信器は、第1のバッファ、第2のバッファ、論理回路、及びE級電力増幅器が設けられる。第1のバッファは、第1の正弦波信号が入力され、第1の正弦波信号を第1の矩形波信号に変換する。第2のバッファは、第1の正弦波信号よりも位相が遅れた第2の正弦波信号が入力され、第2の正弦波信号を第2の矩形波信号に変換する。論理回路は、第1及び第2の矩形波信号が入力され、第1及び第2の矩形波信号を論理演算して所定のデューティーを有するロジック信号を生成する。E級電力増幅器は、ロジック信号が入力され、ロジック信号に基づいて増幅動作する。

(もっと読む)

増幅装置及び信号の増幅方法

【課題】増幅装置及び信号の増幅方法を提供する。

【解決手段】増幅装置は、信号入力(31)と、帰還入力(32)と、信号出力(33)とを備えた増幅器(3)を有する。第1の結合路(FB1)は、第1のインピーダンス素子(R1)を備え、帰還入力(32)を信号出力(33)に接続する。第2の結合路(FB2)は、直列に接続したフィルタ装置(4)と、バッファ回路(5)と、第2のインピーダンス素子(R2)を有し、帰還入力(32)を信号出力(33)または信号入力(31)に接続する。

(もっと読む)

増幅装置

【課題】直流電圧が含まれていることを検出する検出部がアンプ回路にとって負荷として機能しない増幅装置を提供する。

【解決手段】増幅装置1は、電圧源V1から供給される電源電圧に基づいて、スピーカーの負側入力端に供給するための基準電圧を生成する基準電圧生成部2と、入力信号を増幅して、スピーカーの正側入力端に出力するアンプ回路A1と、第1閾値電圧と第2閾値電圧とを生成する閾値電圧生成部4と、基準電圧が第1閾値電圧以上である場合、又は、基準電圧が第2閾値電圧以下である場合にアンプ回路からの出力電圧に直流電圧が含まれることを示す信号を出力し、基準電圧が第1閾値電圧よりも小さく、かつ、基準電圧が第2閾値電圧よりも大きい場合にアンプ回路からの出力電圧に直流電圧が含まれないことを示す信号を出力する検出部5とを備える。

(もっと読む)

基準電圧発生回路

【課題】スタート信号を用いて起動を行う基準電圧発生回路において、起動時に基準電圧発生回路の動作を適切に安定化する。

【解決手段】この基準電圧発生回路は、第1の電源電位及び第2の電源電位が供給されて基準電圧を発生する基準電圧発生回路であって、基準電流制御信号を生成して制御ノードに出力する第1の回路と、制御ノードにおける基準電流制御信号に従って電流を流すことにより、出力端子に基準電圧を出力する第2の回路と、スタート信号が活性化されたときに、制御ノードにおける基準電流制御信号を初期化する第3の回路とを具備し、第3の回路が、第2の電源電位と制御ノードとの間に直列に接続された第1のトランジスタ及び第2のトランジスタを含み、第1のトランジスタのゲートに、スタート信号が印加され、第2のトランジスタのゲートに、第2の回路が流す電流に基づく負帰還信号が印加される。

(もっと読む)

スイッチドキャパシター回路、検出装置及び電子機器

【課題】負荷電流による電圧ドロップを抑制するスイッチドキャパシター回路、検出装置及び電子機器等を提供すること。

【解決手段】スイッチドキャパシター回路は、出力用の演算増幅器OPBと、スイッチドキャパシター動作を行うための複数のスイッチ素子SB1〜SB8と、スイッチドキャパシター動作を行うための複数のキャパシターCB1,CB2と、スイッチドキャパシター回路の出力端子ノードNTと第1のスイッチ素子SB6との間に設けられる静電保護用の抵抗素子RB1と、を含む。

(もっと読む)

電力変換器のための制御装置

【課題】電力変換器のための制御装置を提供する。

【解決手段】電力変換器のための制御装置は、第1の増幅ステージと、第1の増幅ステージに連結される第2の増幅ステージとを備える。第1の増幅ステージは、電力変換器の出力信号に従ってエネルギー貯蔵素子の第1の端子における第1の増幅された信号を生成する。第2の増幅ステージは、エネルギー貯蔵素子の第2の端子における第2の増幅された信号を生成し、出力信号における変化に応答して、第2の増幅された信号を変化させる。第2の増幅ステージは、更に、第1の増幅された信号に基づいて、第2の増幅された信号の変化を減少させる。

(もっと読む)

電子回路

【課題】相補信号による差動出力のバイアス電圧のオフセットの入力信号に対する変化を抑制すること。

【解決手段】ベースに入力信号Vinが入力される第1トランジスタQ1と、ベースに前記入力信号を平滑化した平滑信号Vavgが入力され、エミッタが前記第1トランジスタのエミッタと共通接続された第2トランジスタQ2と、前記第1トランジスタおよび前記第2トランジスタのコレクタに接続され、相補出力をなす第1出力端子OUT1および第2出力端子OUT2と、前記第1トランジスタおよび前記第2トランジスタのそれぞれのコレクタと前記第2トランジスタのベースとの電位差をそれぞれ一定に保つ電位差生成回路20と、を具備する電子回路。

(もっと読む)

電源回路

【課題】比較的簡易な構成で、定電圧駆動と定電流駆動を所望に応じて選択可能な電源回路を提供する。

【解決手段】演算増幅器1の出力端子とグランドとの間に第1及び第2の抵抗器31,32が直列接続されて設けられ、演算増幅器1の非反転入力端子には、所定の基準電圧が印加され、演算増幅器1の出力端子には、外部からの信号により動作制御可能に構成されてなるバッファアンプ2が接続され、バッファアンプ2の出力端子とグランドとの間には、MOSトランジスタ11と第3の抵抗器33が順に直列接続されて設けられ、これらの接続が、切替制御回路4、及び、第1乃至第4のアナログスイッチ21〜24により切り替えられることで、定電圧駆動と定電流駆動が選択可能となっている。

(もっと読む)

スイッチ回路

【課題】導通開始命令からスイッチ素子が導通を開始するまでの遅延時間をより短縮するスイッチ回路を提供する。

【解決手段】外部からの第1の直流電圧を入力し第2の直流電圧を出力するスイッチ素子と、前記第2の直流電圧が前記第1の直流電圧と同等になるまでの電圧傾斜を制御する積分回路と、前記第2の直流電圧を帰還する帰還回路と、この帰還回路の出力と前記積分回路の出力との誤差を増幅する誤差増幅器とを備え、この誤差増幅器の出力により前記スイッチ素子は制御されることを特徴とするスイッチ回路。

(もっと読む)

調整可能な線形性を有するSPS受信機

【課題】衛星測位システム(SPS)受信機のバイアス電流を調整する装置を提供する。

【解決手段】SPS受信機は、該SPS受信機についての異なる複数のバイアス電流設定に関連付けられる該SPS受信機についての複数のモードのうちの1つで動作する。該複数のモードのうちの1つは、該SPS受信機と並置される送信機の出力電力レベルに基づき選択される。該SPS受信機内のLNA、ミキサ、及びまたはLO生成器のバイアス電流は、該選択されたモードに基づき設定される。一構成において、送信機出力電力レベルが切り換えポイントより低い場合、SPS受信機に対し、第1(例えば、低電力)モードが選択される。送信機出力電力レベルが切り換えポイントより高い場合、第2(例えば、高線形性)モードが選択される。第2モードは、第1モードより大きいSPS受信機についてのバイアス電流に関連付けられている。

(もっと読む)

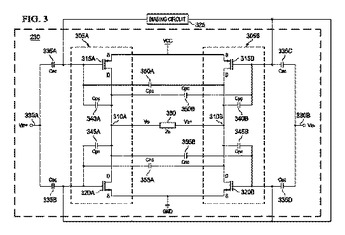

入力抵抗が改善され、コモンモード制御された増幅器

第1出力(Vo−)を規定し、第1入力端子(330A)に結合されるゲートを各トランジスタ(315A、320A)が有する第1対のトランジスタ(305A)、第2出力(Vo+)を規定し、第2入力端子(330B)に結合されるゲートを各トランジスタ(315B、320B)が有する第2対のトランジスタ(305B)、第2出力端子(310B)に及び第1対のトランジスタの第1トランジスタ(315A)のゲートに結合される第1キャパシタ(350A)、第2出力端子(310B)に及び第1対の第2トランジスタ(320A)のゲートに結合される第2キャパシタ(355A)、第1出力端子(310A)に及び第2対の第3トランジスタ(315B)のゲートに結合される第3キャパシタ(350B)、及び第1出力端子(310A)に及び第2対の第4トランジスタ(320B)のゲートに結合される第4キャパシタ(355B)を含む増幅器(230)。

(もっと読む)

(もっと読む)

スイッチング増幅器回路構成およびスイッチング増幅の方法

スイッチング増幅器回路構成は、入力端子(In)および出力端子(Out)を有する主増幅器(Amp)と、主増幅器(Amp)の入力および出力動作点を設定するための調節増幅器(rAmp)とを備える。調節増幅器rAmpは、基準レベル(Vref)に接続された第1の入力端子と、出力端子(Out)に接続された第2の入力端子(Ain)と、第1のスイッチ(S1)を介して入力端子(In)に接続された出力端子(Aout)とを有する補助増幅器(A)を備える。さらにスイッチング増幅器回路構成は、入力端子(In)に接続されたキャンセルコンデンサ(Cc)と、第1の回路ノード(n1)において出力端子(Out)とキャンセルコンデンサ(Cc)との間に接続された第2のスイッチ(S2)と、回路ノード(n1)と基準レベル(Vref)との間に接続された第3のスイッチ(S3)とを備える。  (もっと読む)

(もっと読む)

半導体集積回路

【課題】差動アンプ回路の出力信号の出力をより正確に制御することが可能な半導体集積回路を提供する。

【解決手段】半導体集積回路は、第4のMOSトランジスタと第5のMOSトランジスタとの間の接点の第1の電圧に応じた信号とイネーブル信号とが入力され、イネーブル信号が第1のレベルであり且つ第1の電圧が規定電圧以上の場合に差動アンプ回路の出力信号を出力端子に出力するための第1の信号を出力し、イネーブル信号が第2のレベルまたは第1の電圧が規定電圧未満の場合に第2の信号を出力する演算回路と、差動アンプ回路の出力信号と演算回路が出力した信号とが入力され、第1の信号が入力された場合には、出力信号を出力端子に出力し、第2の信号が入力された場合には、出力端子へ或る論理に固定した信号を出力する出力バッファ回路と、を備える。

(もっと読む)

チャージアンプ回路

【課題】 入力側にリーク電流が存在した場合であっても正確な出力を得ることが可能なチャージアンプ回路を提供する。

【解決手段】 積分回路101と増幅回路102との間に直流遮断容量103を設け、不要な直流成分であるリーク電流を遮断すると共に、直流遮断容量103の出力端にバイアス抵抗201を介して定電圧発生回路108を接続し、バイアス電圧を印加することで、増幅回路102の入力信号に増幅回路102で必要とされる適切な直流電圧レベルを与える。

(もっと読む)

ドライバ回路、及び電子回路装置

【課題】基準電流に対して所定の比の負荷電流を高い精度で得るドライバ回路を提供する。

【解決手段】MOSトランジスタM3のドレイン端子には二つの抵抗R1及びR2が接続されており、その他端には夫々電流発生装置IREF、負荷LOADが接続されている。両抵抗値は同値であるとする。またトランジスタM3のドレイン端子と両抵抗との接続部を接続点Aとする。この電子回路装置は抵抗R1と電流発生装置IREFとの接続部を接続点B、抵抗R2と負荷LOADとの接続部を接続点Cとして、夫々差動増幅器A1の入力端子へ接続したものである。該差動増幅器において、トランジスタM3のゲート端子に出力端子、つまり制御入力端子が接続されることを特徴とする。その接続部を接続点Gとする。該差動増幅器は接続点BおよびCの電位差を帰還する回路として機能する。

(もっと読む)

1 - 20 / 43

[ Back to top ]