Fターム[5J500AC13]の内容

増幅器一般 (93,357) | 目的、効果 (9,357) | 出力直流電圧の変動対策、調整 (444) | オフセット対策 (358)

Fターム[5J500AC13]に分類される特許

1 - 20 / 358

正帰還増幅器およびインターポレーション回路

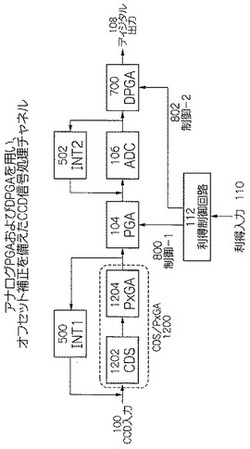

可変利得増幅システム

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】本可変利得増幅回路は、入力信号から不要の相関ノイズ成分を除去する相関二重サンプリング回路1202と、相関二重サンプリング回路の下流側に位置する第1プログラマブル利得増幅器104と、入力が前記第1プログラマブル利得増幅器の入力に接続され、出力が相関二重サンプリング回路の入力に接続され、入力信号のオフセットおよび相関二重サンプリング回路のオフセットのうちの少なくともいずれか一方のために第1オフセット補正を提供する第1オフセット補正回路500と、第1プログラマブル利得増幅器の下流側に位置するアナログ/ディジタル変換器106と、第1プログラマブル利得増幅器の下流側に位置し、第2オフセット補正を提供する第2オフセット補正回路502と、相関二重サンプリング回路の下流側であって、かつ、第1プログラマブル利得増幅器の上流側に位置する画素利得増幅器1204を備えている。

(もっと読む)

オフセット電圧補償装置

【課題】オフセット電圧補償装置において、部品点数の増加を抑えながら、増幅器のオフセット電圧を補償して、センサ部の直流出力信号の真値を検出する。

【解決手段】オフセット電圧補償装置1は、電源2と接続され物理量を計測して出力信号に変換するセンサ部3と、センサ部3の入力を短絡する切替器4と、センサ部3の出力信号を増幅する増幅器5と、増幅器5の出力に基づいて電気量を演算する演算器6とを備える。演算器6は、センサ部3の入力を短絡していない時の増幅器5の出力から、短絡時の増幅器5の出力を減算して信号成分の差分を抽出する。次に、当該信号成分の差分と、センサ部3の抵抗値及び切替器4の抵抗値から定められる所定の係数とを用いて、センサ部3の出力信号の真値を検出する。

(もっと読む)

センサ信号処理装置

【課題】簡単な構成で入力オフセット電圧の温度依存性が小さいセンサ信号処理装置を提供する。

【解決手段】センサ用電源として第1の電源電圧V´ccを供給されて動作し、センサ出力Vs1、Vs2を出力するセンサ部100と、信号処理用電源として第2の電源電圧Vccを供給されて動作し、センサ出力Vs1、Vs2が入力される差動対を使用する差動増幅部を有して信号処理を行なう信号処理部200と、を有してセンサ信号処理装置1を構成する。この第1の電源電圧V´ccは、信号処理部200の差動増幅部250の入力電圧範囲の下限領域に設定される。

(もっと読む)

液晶表示装置の駆動回路

【課題】入出力間オフセット電圧を削減しつつ消費電流を削減する。

【解決手段】第1導電型の第1差動回路は、第1入力信号と出力信号とを差動入力信号とする。第1導電型の第2差動回路は、第2入力信号と出力信号とを差動入力信号とする。第2導電型の第3差動回路は、第1入力信号と出力信号とを差動入力信号とする。第2導電型の第4差動回路は、第2入力信号と出力信号とを差動入力信号とする。出力段回路は、第1乃至第4差動回路の出力に基づいて出力信号を出力する。差動増幅器は、上記第1乃至第4差動回路、出力段回路を具備し、制御信号に基づいて、第1乃至第4差動回路を形成するトランジスタのチャネル長とチャネル幅との比を変更する。

(もっと読む)

増幅装置

【課題】 入力電圧が低く、特性を向上させた増幅装置を提供する。

【解決手段】 増幅装置は、一対の受光素子からそれぞれ入力された第1及び第2の電流信号In(+),In(−)を、第1及び第2の電圧信号Vo(−),Vo(+)にそれぞれ変換して出力する第1及び第2のトランスインピーダンスアンプ20と、第1及び第2の電流信号In(+),In(−)の各電流を分流する分流回路24と、第1及び第2の電圧信号Vo(−),Vo(+)の平均電圧値を示す平均信号を生成して出力する平均値検出回路と、平均信号Vav、及び第1及び第2の電圧信号Vo(−),Vo(+)のオフセット電圧値に基づいて、分流回路24に分流される第1及び第2の電流信号In(+),In(−)の各電流値を制御する制御回路23とを含む。

(もっと読む)

駆動回路並びに関連するエラー検出回路及び方法

【課題】

発光装置のための低出力電圧駆動回路が、本発明の例示としての実施形態に従って提供される。

【解決手段】

また、オフセット電圧キャンセル及び/又はレベルシフタが、駆動電流の精度を高くするように駆動回路に組み込まれる。更に、エラー検出回路及び方法は、本発明の駆動回路の最小の出力電圧を検出して対応できるように、用いられる。

(もっと読む)

スイッチトキャパシター積分回路、フィルター回路、多出力フィルター回路、物理量測定装置、及び電子機器

【課題】低周波数帯域の雑音の影響をより一層小さくすることができるスイッチトキャパシター積分回路等を提供する。

【解決手段】スイッチトキャパシター積分回路10は、第1の容量と第2の容量とを有する電圧電荷変換回路20と、第1の容量に充電された電荷を積分する電荷積分回路30とを含む。電圧電荷変換回路20は、第1の期間において、第1の容量に充電された電荷を転送すると共に入力信号に対応した電荷を第2の容量に充電し、第2の期間において、第2の容量に充電された電荷の一部を第1の容量に充電すると共に入力信号に対応した電荷を第1の容量に充電する。電荷積分回路30は、第3の期間において、演算増幅器の入力に接続されるオフセットキャンセル容量の他端と第1の容量の一端とを接続し、第4の期間において、オフセットキャンセル容量の他端と接地電位とを接続する。

(もっと読む)

信号処理装置

【課題】 抵抗及び小さな静電容量を用いた回路により、検出素子の出力信号を直流成分を除いて増幅する小型な信号処理装置を得る。

【解決手段】 入力信号が第1のインピーダンスを介して反転入力端子に入力される第1のオペアンプと、第1のオペアンプの反転入力端子と出力端子とに接続された第2のインピーダンスと、基準電圧が非反転入力端子に入力され、出力端子が第1のオペアンプの非反転入力端子に接続された第2のオペアンプと、第2のオペアンプの反転入力端子と出力端子とに接続された第1の静電容量と第1のスイッチと、第2のスイッチを介して第1のオペアンプの出力端子と前記第2のオペアンプの反転端子とに接続された第3の抵抗と、第3のスイッチを介して第1のオペアンプの出力端子と第2のオペアンプの反転端子とに接続された第4の抵抗とを備えた。

(もっと読む)

オフセット補正装置、及び補正方法

【課題】オフセット電圧をより高精度に補正すること。

【解決手段】オフセット補正装置は、所定の入力信号と、所定ビット前に入力された入力信号に基づいた信号と、を加算する加算手段と、加算手段により加算された信号に対してオフセット補正を行うオフセット補正手段と、オフセット補正手段により補正された信号のレベルを判定し、該判定結果を加算手段に対して出力する判定手段と、判定手段による判定結果に基づいて、オフセット補正手段を制御するオフセット補正制御手段と、判定手段による判定結果を加算手段に対して出力させる場合と遮断する場合とに切替える切替手段と、を備えている。

(もっと読む)

増幅装置、増幅システムおよび電流電圧変換装置

【課題】適切にオフセット電圧をキャンセルすることが可能な増幅装置、増幅システムおよびこれを用いた電流電圧変換装置を提供する。

【解決手段】実施形態によれば、増幅装置は、メインアンプと、第1のサブアンプと、第2のサブアンプとを備える。前記メインアンプは、第1の入力電圧と第2の入力電圧との差を増幅した電圧を出力する。前記第1のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。前記第2のサブアンプは、入力端子同士を短絡したときの出力電圧に基づいて自身のオフセットキャンセルを行い、前記第1の入力電圧および前記第2の入力電圧が入力されたときの出力電圧に基づいて前記メインアンプのオフセットキャンセルを行う。

(もっと読む)

演算増幅器

【課題】入力オフセット電圧温度変動を悪化させることなく入力オフセット電圧のゼロ調整を可能とする。

【解決手段】差動対をなすように第1及び第2のPチャネルMOSトランジスタ1,2が差動接続されてなる差動増幅回路101を有すると共に、第1及び第2のPチャネルMOSトランジスタ1,2へテール電流を供給する第3の定電流源13に対して負の温度特性を有する電流を生成、出力する負温度特性電流生成回路103と、第1及び第2のPチャネルMOSトランジスタ1,2の各々へ入力オフセット電圧補正電流を供給する入力オフセット電圧補正電流生成回路102とを具備し、入力オフセット電圧補正電流生成回路102は、負温度特性電流生成回路103の出力電流を基に、入力オフセット電圧補正電流を出力調整可能に構成されたものとなっている。

(もっと読む)

差動増幅回路及びコンパレータ

【課題】オフセット電圧の変動を低減した差動増幅回路及びコンパレータを提供する。

【解決手段】実施形態によれば、差動回路と、出力回路と、クリップ回路と、を備えたことを特徴とする差動増幅回路が提供される。前記差動回路は、一対の入力信号の電位差に応じた一対の差動電流を生成する。前記出力回路は、前記一対の差動電流を受けて、電流差に応じた出力電圧を生成する。前記クリップ回路は、前記出力電圧に応じてオンし、前記出力電圧をしきい値電圧を含みローレベルまたは前記ローレベルよりも高いハイレベルに変換できる範囲に抑制するクリップ素子を有する。

(もっと読む)

D級増幅回路

【課題】全差動オペアンプが有するオフセット電圧や抵抗器の抵抗値の相対ばらつきに起因する出力オフセット電圧のキャンセルを可能とする。

【解決手段】出力オフセット電圧キャンセル回路901は、回路起動時から全差動オペアンプ1の出力オフセット電圧の極性に応じて、出力オフセット電圧を零に漸近せしめるべく電圧を全差動オペアンプ1の入力段に印加可能に構成され、コントロールロジック回路113は、回路起動時から全差動オペアンプ1の出力オフセット電圧が零となるまでの出力オフセット電圧キャンセル期間、スイッチ回路115に、第1のフィードバック用抵抗器23を全差動オペアンプ1の反転入力端子と正出力端子との間に、第2のフィードバック用抵抗器24を全差動オペアンプ1の非反転入力端子と負出力端子との間に、それぞれ接続せしめるようになっている。

(もっと読む)

自動利得調整回路

【課題】利得可変回路の出力振幅の温度依存性を低減する。

【解決手段】自動利得調整回路は、利得可変回路3の出力信号のピーク電圧を検出するピーク検出回路10と、利得可変回路3の出力信号の平均値電圧を検出すると共に、平均値電圧に利得可変回路3の所望の出力振幅の1/2の電圧を加える平均値検出・出力振幅設定回路11と、ピーク検出回路10の出力電圧と平均値検出・出力振幅設定回路11の出力電圧との差分を増幅して、増幅結果を利得制御信号として利得可変回路3の利得を制御する高利得アンプ12とを備える。ピーク検出回路10の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数と、平均値検出・出力振幅設定回路11の入力端子から出力端子までの経路に挿入されるトランジスタのベース−エミッタ接合の数とは同一である。

(もっと読む)

電圧電流変換回路

【課題】差動入力部を有するとともに、出力部を構成するカレントミラー回路のミラー比を調整して入力オフセット電圧をもたせた電圧電流変換回路において、差動入力部および入力オフセット電圧の温度特性を平坦なものにする。

【解決手段】平坦な温度特性を有する第1の定電流Ib1に正の温度特性を有する第2の定電流Ib2を加えた電流をバイアス電流として、MP10及びMP11からなる差動入力部に供給することにより、差動入力部の温度特性とバイアス電流の温度特性とを相殺させて差動入力部の温度特性をゼロ(平坦なもの)にすることができる。また、電流吐き出し型の第1のカレントミラー回路の出力と、電流吸い込み型の第2のカレントミラー回路の出力との接続点を電圧電流変換回路の出力端子Out2とし、この接続点に第1の定電流Ib1に比例した電流を加える構成により、温度特性のない入力オフセット電圧も実現することができる。

(もっと読む)

電子回路及び光受光回路

【課題】 入出力信号のオフセットを補償して、入力電流が増大しても増幅動作を行うことができる電子回路及び光受光回路を提供する。

【解決手段】 本発明の電子回路30は、相補的な入力電流を、相補的な電圧信号に変換して出力する差動トランスインピーダンスアンプ10と、出力を入力し、出力が差動トランスインピーダンスアンプ10の入力に接続される差動回路18であって、差動回路18の電流源Is5が入力電流の平均値I2に基づいて制御される差動回路18と、を備えることを特徴とする。

(もっと読む)

オフセット調整差動増幅回路

【課題】オフセット調整差動増幅回路において、オフセット調整値を温度に対して安定して維持することを提供する。

【解決手段】オフセット調整差動増幅回路は、差動対を構成する第1、第2のMOSトランジスタM1、M2と、第1のMOSトランジスタM1のソースに一端が接続される第1の抵抗R1と、第2のMOSトランジスタM2のソースに一端が接続され、第1の抵抗R1の他端に他端が接続される第2の抵抗R2と、第1、第2の抵抗R1、R2の接続点と第1の電源端子との間に接続され、差動対の動作電流を供給する電流源M6と、第1のMOSトランジスタM1のソースにソースが接続され、第2の電源端子にドレインが接続され、ゲートにオフセット調整電圧VTが与えられ、第1の抵抗R1の両端に生じる電圧を調節するオフセット調整電流I7をオフセット調整電圧VTに応じて制御する第3のMOSトランジスタM7と、を有する。

(もっと読む)

液晶駆動用のソースドライバのオフセット低減出力回路

【課題】 出力アンプのオフセット電圧を適切に低減して表示品質の悪化を防止することができる液晶駆動用のソースドライバのオフセット低減出力回路を提供する。

【解決手段】 基準電圧がオペアンプの非反転入力端に印加されたオペアンプと、少なくとも通常出力動作時にオペアンプの反転入力端に接続される第1の接続点に各々の一端が接続された第1の入力コンデンサ及び第1の出力コンデンサと、リセット動作時に第1の入力コンデンサ及び第1の出力コンデンサ各々の両端を短絡してその両端に基準電圧を印加し、リセット動作後の通常出力動作時に第1の入力コンデンサの他端に階調電圧を印加しかつ第1の出力コンデンサの他端をオペアンプの出力端に接続する第1のスイッチ素子回路と、を備え、第1のスイッチ素子回路は、第1の接続点とオペアンプの出力端との間に接続され、リセット動作時にオンとなり、通常出力動作時にオフとなる直列接続の第1及び第2のスイッチ素子を有し、通常出力動作時には第1及び第2のスイッチ素子の直列接続点に基準電圧を印加する。

(もっと読む)

電圧出力回路、及びアクティブケーブル

【課題】面積及び消費電力を低減し、高精度に単相差動変換をすることができる電圧出力回路を提供する。

【解決手段】電圧出力回路は、第1の電圧Vopが入力される一端、及び第2の電圧Vomを出力する他端を備える抵抗素子R1と、抵抗素子R1の他端に接続される反転入力端子、及び第3の電圧Vrefが入力される非反転入力端子を備える第1の増幅器121と、第1の増幅器121からの出力が入力される一端、及び抵抗素子R1の他端が接続される他端を備えるコンデンサC1と、を備え、第1の増幅器121の出力、または抵抗素子R1の他端に接続される第2の増幅器122の出力は、第1の電圧Vopの積分値である第4の電圧Vdcocであり、コンデンサC1、及び第1の増幅器121で構成されるミラー容量と、抵抗素子R1とによって、ローパスフィルタが構成される。

(もっと読む)

1 - 20 / 358

[ Back to top ]