Fターム[5J500AK42]の内容

Fターム[5J500AK42]の下位に属するFターム

直流通過フィルタ (1)

Fターム[5J500AK42]に分類される特許

61 - 80 / 792

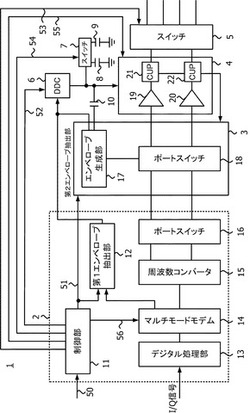

送信装置

【課題】変調信号の周波数の切り替えに対応して増幅器の電源電圧を最適化可能な送信装置を提供することを目的とする。

【解決手段】送信装置は、送信データを変調した第1変調信号に基づいて第1エンベロープ信号を抽出する第1エンベロープ抽出部と、該送信データを該第1変調信号よりも高い周波数で変調した第2変調信号に基づいて第2エンベロープ信号を抽出する第2エンベロープ抽出部と、該第1または第2変調信号を増幅する増幅部と、該第1または第2のエンベロープ信号に基づいて、該増幅部に供給する電源電圧を出力する電源生成部と、該第1または第2変調信号のいずれか一方を該増幅部に増幅させると共に、対応する該第1または第2エンベロープ信号のいずれか一方に基づいて該電源生成部に電源電圧を出力させる制御部とを有する。

(もっと読む)

定電流回路

【課題】 電流値のバラツキの小さい定電流回路を提供する。

【解決手段】 Pチャネルトランジスタ3および9は、互いに比例した定電流を出力する第1および第2の定電流源として機能する。キャパシタ5は、Pチャネルトランジスタ3に直列接続されている。放電用スイッチであるNチャネルトランジスタ6は、周期的にキャパシタ5の充電電荷を放電させる。コンパレータ7は、キャパシタ5の充電電圧V1が基準電圧Va以内である期間だけPチャネルトランジスタ4および10をONにすることにより第1および第2の定電流源による電流の出力を行わせる。キャパシタ11、抵抗12およびキャパシタ13からなる平滑化回路19は、第2の定電流源の出力電流を平滑化する。Nチャネルトランジスタ14および15からなる出力用カレントミラーは、この平滑化回路19により平滑化された電流に比例した電流を出力する。

(もっと読む)

差動増幅装置

【課題】 差動増幅装置が出力するオフセット電圧を充分に抑制する。

【解決手段】 差動増幅器10は、キャパシタCを介して+IN端子に入力される信号と、−IN端子に入力される信号の差分を増幅する。スイッチS1は、+IN端子が、キャパシタCを介した信号を入力するか否かを切り替える。抵抗RINは、+IN端子と−IN端子の間に接続される。オフセット電圧補正回路20は、+IN端子がキャパシタCを介した信号を入力しないようにスイッチS1が制御された補正期間において、差動増幅器10の出力信号に基づき差動増幅器10のオフセット電圧を補正する。

(もっと読む)

送信器

【課題】電力増幅器を高効率化及び高信頼性化する。

【解決手段】一つの実施形態によれば、送信器は、第1のバッファ、第2のバッファ、論理回路、及びE級電力増幅器が設けられる。第1のバッファは、第1の正弦波信号が入力され、第1の正弦波信号を第1の矩形波信号に変換する。第2のバッファは、第1の正弦波信号よりも位相が遅れた第2の正弦波信号が入力され、第2の正弦波信号を第2の矩形波信号に変換する。論理回路は、第1及び第2の矩形波信号が入力され、第1及び第2の矩形波信号を論理演算して所定のデューティーを有するロジック信号を生成する。E級電力増幅器は、ロジック信号が入力され、ロジック信号に基づいて増幅動作する。

(もっと読む)

チョッパ式増幅回路

【課題】従来のチョッパ式増幅装置は、チョッパクロックに同期したチョッパノイズを除去するために、チョッパノイズが重畳しない期間の電圧を保持しておき、保持しておいた電圧を出力するために、入力電圧と出力電圧の位相がずれてしまう。

【解決手段】出力側スイッチ回路18で復調した電圧を、チョッパクロックの反転前の値をチョッパクロックの反転後まで保持するサンプルホールド回路20,22で保持する。チョッパノイズの影響をサンプルホールド回路20,22で除去できる。前段チャージアンプと後段チャージアンプで増幅回路を構成することが好ましく、保持時間を短くすることができる。帰還抵抗を大きくすることで出力電圧の変動率を低減できる。5%以下の変動率とする抵抗値を用いることが好ましい。

(もっと読む)

電圧調整のための電圧制御電流源

【課題】バス調整のための電圧制御電流源を提供するシステムと方法を提供する。

【解決手段】電流源104から電気バス106に送達されるバス電流は、PWMデューティサイクルに従い、同期スイッチ112を用いて制御される。更に、PWMデューティサイクルは、電気バスの電圧と基準電圧との比較に基づくエラー信号に比例するように制御される。

(もっと読む)

オーディオ信号増幅装置及びオーディオ信号増幅方法

【課題】歪みやノイズの発生箇所を問わず、Dクラスアンプの音質の劣化を改善することができるオーディオ信号増幅装置及びオーディオ信号増幅方法を提供する。

【解決手段】出力フィルタ14aは、出力段トランジスタ13pで増幅された正相PWM信号を復調し、正相出力オーディオ信号を生成する。また、出力フィルタ14aは、出力段トランジスタ13nで増幅された逆相PWM信号を復調し、逆相出力オーディオ信号を生成する。出力検出回路20は、正相出力オーディオ信号と逆相出力オーディオ信号との電圧の差分をとることにより、出力オーディオ信号を生成する。出力可変電源装置17は、出力オーディオ信号と入力オーディオ信号との差分を示す差分信号に基づいて、出力段トランジスタ13pに印加される電圧を制御する。

(もっと読む)

遅延制御回路、チャージポンプ回路、及びチャージポンプ回路における充放電電流制御方法

【課題】トランジスタがアンバランスであってもチャージポンプ回路に最適なバイアス電圧を与えられる遅延制御回路を提供する。

【解決手段】所定の信号を受けて電流入出力端子から充放電を行うチャージポンプ回路と、電流入出力端子の端子電圧に基づく電圧が電源として供給される遅延回路と、チャージポンプ回路の充放電電流の基準となるバイアス電圧を生成するバイアス生成回路と、を備え、チャージポンプ回路及び遅延回路が、それぞれ、第1導電型トランジスタと、第2導電型トランジスタを含んで構成され、バイアス生成回路が、第1導電型トランジスタの相互コンダクタンスと第2導電型トランジスタの相互コンダクタンスの和に基づいて、バイアス電圧を生成する。チャージポンプ回路の充放電により遅延回路の電源電圧を制御し、これにより遅延回路の遅延時間を制御する。

(もっと読む)

オーディオ信号増幅装置及びオーディオ信号増幅方法

【課題】歪みやノイズの発生箇所を問わず、Dクラスアンプの音質の劣化を改善することができるオーディオ信号増幅装置及びオーディオ信号増幅方法を提供する。

【解決手段】PWM変換回路11は、入力オーディオ信号をパルス幅変調し、PWM信号を生成する。出力段トランジスタ13は、生成されたPWM信号に基づいてスイッチングし、出力可変電源装置17から印加された電圧に基づいて、PWM信号を増幅する。出力フィルタ14は、増幅されたPWM信号を復調し、出力オーディオ信号を生成する。出力可変電源装置17は、出力オーディオ信号と入力オーディオ信号との差分に基づいて、出力段トランジスタ13に印加される電圧を制御する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】ローパスフィルタのインダクターの回生電流に起因するデジタル増幅器の電源雑音を低減する。

【解決手段】半導体集積回路は、ハイサイドとローサイドの出力デバイス31、32とドライバ33を含むデジタル増幅器30と、正の動作電圧Vopが供給され正と負の電源電圧+Vcc、−Vccを生成するチャージポンプユニット50を具備する。デジタル増幅器30の出力端子はインダクター36と容量37を含むローパスフィルタLPFと接続され、ユニット50はスイッチング制御される第1スイッチSW1乃至第6スイッチSW6と第1容量C1乃至第4容量C4を含む。インダクター36とオン状態のハイサイド出力デバイス31またはローサイド出力デバイス32とを介して容量37と正の電源電圧+Vccまたは負の電源電圧−Vccとの間の回生電流を、第6スイッチSW6をオン状態に制御して、第2容量C2で吸収する。

(もっと読む)

半導体集積回路およびその動作方法

【課題】DCオフセットキャンセル動作の動作期間を短縮する。

【解決手段】フィルタ処理と増幅機能を有するアクティブローフィルタ300の差動出力端子に2個の校正抵抗R22の一方の端子が接続され、2個の校正抵抗R22の他方の端子に電圧比較器CMPの2個の入力端子と切り換えスイッチSWIOの2個の端子が接続される。DCオフセット電圧低減のデジタル制御信号DACS、DAC2…DAC0を算出する算出期間で、デジタルアナログ変換器DAC0のアナログ電流による一方の校正抵抗R22の電圧降下に依存する校正電圧を電圧比較器CMPが検出する。DCオフセット電圧を低減する校正期間では、デジタル制御信号に応答したデジタルアナログ変換器の校正アナログ電流が切り換えスイッチSWIOを介してフィルタ300の入力側に流される。

(もっと読む)

受信回路並びにそれを備えた半導体装置及び情報処理システム

【課題】 本発明は、低速信号よりも高速信号を増幅し、かつ、消費電力を抑える受信回路並びにそれを備えた半導体装置及び情報処理システムを実現することを目的とする。

【解決手段】 本発明の受信回路並びにそれを備えた半導体装置及び情報処理システムは、第1の増幅器と、第1の増幅器よりもカットオフ周波数の低い第2の増幅器とを有し、第1の増幅器及び第2の増幅器に受信信号を入力し、第1の増幅器の出力から第2の増幅器の出力を減じて出力する。

(もっと読む)

電力増幅合成回路ならびにそれを用いた電力増幅回路,送信装置および通信装置

【課題】 電源効率の高い電力増幅合成回路ならびにそれを用いた電力増幅回路,送信装置および通信装置を提供する。

【解決手段】 ソース端子に第1入力信号が、ゲート端子に第2入力信号と同相の信号が入力されるトランジスタ33と、ソース端子に第2入力信号が、ゲート端子に第1入力信号と同相の信号が入力されるトランジスタ34と、ゲート端子が第1のトランジスタのドレイン端子に接続され、ソース端子が定電流源6を介してグランド電位に接続されるトランジスタ4と、トランジスタ4のドレイン端子および電源電位を接続する低域通過フィルタ回路8と、トランジスタ4のドレイン端子に接続された出力整合回路16と、第1入力信号および第2入力信号の位相差が増加すると定電流源を流れる電流が減少するように定電流源を制御する電流制御信号を出力する電流制御回路19とを備える電力増幅合成回路とする。

(もっと読む)

電力変換器のための増幅器システム

【課題】寄生スイッチングデバイスのアクティビティを減らす電力変換器の増幅器システムを提供すること。

【解決手段】

電力変換器のための増幅器システムは、少なくとも、半導体の基板における集積回路に形成された第1のスイッチングデバイスおよび第2のスイッチングデバイスを含む。第1のスイッチングデバイスおよび第2のスイッチングデバイスは、ハーフブリッジの構成で形成され得、半導体の出力ノード上に増幅出力信号を生成するために、協働的に切り替え可能であり得る。抵抗器およびコンデンサは、半導体に含まれる、電源入力ノードと基板ノードとの間に並列に連結され得る。コンデンサは、集積回路に現れる寄生スイッチングデバイスのバイアスを逆転させるために、第1スイッチングデバイスおよび第2のスイッチングデバイスのスイッチングサイクルの間に、選択的にバイアスを下げる電圧に充電され得る。

(もっと読む)

ドライバ回路

【課題】単電源駆動で、歪が小さく、大振幅の信号出力電圧が得られるドライバ回路を提供する。

【解決手段】1は入力端子、2、3は出力端子、4は第1の反転型オペアンプ、5は第2の反転型オペアンプ、6は非反転型オペアンプ、7はトランス、8は正電源電圧VCC、9はアナロググランドAGND(VCC/2)、10はグランドGND(0V)を示す。第1の反転型のドライバ用オペアンプの出力を第2の反転型のドライバ用オペアンプと非反転型のドライバ用オペアンプで受け、それらの出力を差動構成とすることで、低電圧での単電源駆動でも大振幅で、歪の小さい出力信号電圧が得られる構成とした。

(もっと読む)

増幅装置及び増幅方法

【課題】増幅後の出力信号の劣化を抑えること。

【解決手段】信号分離部21は入力信号から第1の信号及び第2の信号を分離する。第1の信号生成部22は、第1の信号を処理したときに生じるリンギングを抑圧可能な第1のキャンセル信号を第1の信号に基づいて生成する。第1の合成部23は第1の信号と第1のキャンセル信号とを合成する。第1の増幅部24は第1の合成部23の出力信号を増幅する。第2の信号生成部25は、第2の信号を処理したときに生じるリンギングを抑圧可能な第2のキャンセル信号を第2の信号に基づいて生成する。第2の合成部26は第2の信号と第2のキャンセル信号とを合成する。第2の増幅部27は第2の合成部26の出力信号を増幅する。第3の合成部28は第1の増幅部24の出力信号と第2の増幅部27の出力信号とを合成する。

(もっと読む)

送信装置

【課題】外部機器による送信信号の周波数特性の劣化を低減できる送信装置を提供する。

【解決手段】入力信号を増幅部(117,118)により増幅して出力端子140から出力する送信装置100において、増幅部(117,118)と出力端子140との間の送信経路に接続された反射波分離部130と、反射波分離部130で分離される反射波に基づいて、出力端子140から出力される送信信号の周波数特性の劣化を補償するように入力信号を補正する補正部150と、を備える。

(もっと読む)

歪み補償回路

【課題】 任意の周波数帯域における歪み補償の性能を向上させることができる歪み補償回路を提供する。

【解決手段】 アンプ3からのフィードバック信号をADC5でディジタル変換し、使用周波数帯域を含む特定帯域の通過特性を有するFIRフィルタ12にADC5からの出力を通過させて直交復調器13に出力し、直交復調器13で直交復調し、LUT係数演算部14でLUT係数を演算し、包絡線演算部15で包絡線の値を演算し、LUT係数設定部16でルックアップテーブルから包絡線の値に対するLUT係数を読み出し、乗算器17a,17bに出力し、乗算器17a,17bで送信信号とLUT係数を乗算して歪み補償を行う歪み補償回路である。

(もっと読む)

増幅装置及び信号の増幅方法

【課題】増幅装置及び信号の増幅方法を提供する。

【解決手段】増幅装置は、信号入力(31)と、帰還入力(32)と、信号出力(33)とを備えた増幅器(3)を有する。第1の結合路(FB1)は、第1のインピーダンス素子(R1)を備え、帰還入力(32)を信号出力(33)に接続する。第2の結合路(FB2)は、直列に接続したフィルタ装置(4)と、バッファ回路(5)と、第2のインピーダンス素子(R2)を有し、帰還入力(32)を信号出力(33)または信号入力(31)に接続する。

(もっと読む)

音声再生システム

【課題】PCMデータのAD変換に代えてPWMによるパルス信号を用いて音声再生を行う場合に、PWMカウント周波数をPCMデータのサンプリング周波数の2のべき乗倍に制限することなく歪の小さなPWMパルス信号を生成して音声再生を行う。

【解決手段】前記PCMデータのサンプリング周波数の2の累乗倍以外の倍数の発振周波数をPWMカウント周波数とするPWM回路(15)により、PCMデータを、指定されたPWM分解能とPWMカウント周波数とで決まるPWMパルス周期に同期するPWMパルス信号(PLS)に変換し、変換したパルス信号をスピーカの駆動に用いる。前記PCMデータのサンプリング周波数と前記PWMパルス信号の周波数の整数分の一倍の周波数との差が最も小さいときの前記整数分の一倍の周波数の前記サンプリング周波数に対する誤差率は、PCMデータの半音階上方の音への周波数の変化率の1/10以下とされる。

(もっと読む)

61 - 80 / 792

[ Back to top ]