Fターム[5J500AK42]の内容

Fターム[5J500AK42]の下位に属するFターム

直流通過フィルタ (1)

Fターム[5J500AK42]に分類される特許

81 - 100 / 792

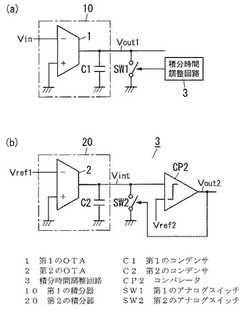

信号増幅回路

【課題】入力電圧に比例した電流を出力するOTAの製造ばらつきおよび周囲温度の変化による利得の変化を抑制することが可能な信号増幅回路を提供する。

【解決手段】入力電圧Vinが入力される第1のOTA1、第1のコンデンサC1を有する第1の積分器10と、第1のコンデンサC1に並列接続された第1のアナログスイッチSW1と、入力電圧Vinの積分時間を調整する積分時間調整回路3とを備える。積分時間調整回路3は、第1の参照電圧Vref1が入力される第2のOTA2、第2のコンデンサC2を有する第2の積分器20と、第2のコンデンサC2に並列接続された第2のアナログスイッチSW2と、第2の積分器20の出力電圧と第2の参照電圧Vref2とを比較するコンパレータCP2とを備え、コンパレータCP2の出力に基づいて第1のアナログスイッチSW1、第2のアナログスイッチSW2それぞれを制御する第1の制御信号、第2の制御信号を出力する。

(もっと読む)

信号処理装置及び信号処理方法

入力信号(x)を処理する信号処理装置が、適応型プレディストータ(110,160)、増幅器(130)、及びダウンコンバータ(150)を備える。増幅器(130)は処理された信号(y’)を増幅して増幅された信号(y’’)を得るように構成されている。ダウンコンバータ(150)は、信号バージョンンの1つが位相シフトである、処理された信号(y’)のバージョンと増幅された信号(y’’)のバージョンとを乗算して、第1のダウンコンバートされた信号(zl,z1’)を取得し、処理された信号(y’)に、増幅された信号(y’’)を乗算して第2のダウンコンバートされた信号(z2,z2’)を取得するように構成されている。プレディストータ(110、160)は、入力信号(x)をプレディストーション特性に従って、予め歪ませて処理された信号(y’)を取得するように構成されている。そしてプレディストータ(110、160)はさらに、第1のダウンコンバートされた信号(zl,z1’)と第2のダウンコンバートされた信号(z2,z2’)に基づいてプレディストーション特性を適応させるように構成されている。  (もっと読む)

(もっと読む)

容量性負荷駆動回路

【課題】容量性負荷の駆動信号にキャリアリップルが重畳することを回避する。

【解決手段】駆動波形信号をパルス変調して変調信号を生成し、電力増幅した後に平滑フィルターを通すことによって生成した駆動信号を容量性負荷に印加する。また、駆動信号に位相進み補償を行って帰還信号を生成し、駆動波形信号に負帰還させる。平滑フィルターと容量性負荷とは取り替え可能な配線によって接続されている。平滑フィルターと容量性負荷とを配線によって接続すると、その配線に関する配線情報が取得され、そして、配線情報に応じたキャリア周波数でパルス変調が行われる。こうすれば、配線に応じたキャリア周波数でパルス変調されるので、駆動信号にキャリアリップルが重畳することを回避することができる。

(もっと読む)

連続時間回路のためのオフセットキャンセレーション

【課題】高速シリアルインターフェイスおよび他の用途のために等化器および他の連続時間回路を改善すること。

【解決手段】マルチステージ増幅器チェーンであって、該マルチステージ増幅器チェーンは、該チェーン内に第1の増幅器ステージと最後の増幅器ステージとを含む、マルチステージ増幅器チェーンと、該最後の増幅器ステージの出力を受信することと、オフセット補正電圧信号を該第1の増幅器ステージに提供することとを行うように構成されているオフセットキャンセレーションループとを備えている、回路。

(もっと読む)

信号増幅回路、電流電圧変換回路、および光受信器

【課題】入力電流の大きさの変化に応じた出力電圧波形の歪みを抑えることができる信号増幅回路、電流電圧変換回路、および光受信器を提供する。

【解決手段】プリアンプ13は、トランジスタ21、及び該トランジスタ21と電源電位線18との間において出力信号を提供するノードAを有し、光電流Iinを受ける信号入力端13aにトランジスタ21のエミッタが接続され、ノードAにトランジスタ21のコレクタが接続されたベース接地回路20と、ノードAに接続され、出力電圧Voutの平均レベルから利得制御信号Vagcを生成する検知回路50と、ベース接地回路20に対して並列に接続されたトランジスタ31を有し、そのベースに利得制御信号Vagcを受ける分流回路30とを備える。検知回路50は、平均レベルの上昇に応じてトランジスタ31を流れる電流が大きくなるように利得制御信号Vagcを生成する。

(もっと読む)

歪補償装置及び無線基地局

【課題】データテーブルの更新期間中も無線基地局の運用を停止する必要がなく、しかも、装置規模及び製造コストの増大を回避しつつ、高精度の歪補償を実現することが可能な、歪補償装置を得る。

【解決手段】DPD処理部2は、HPA6の入出力特性の歪を補償するための、複数の補正データを含むデータテーブル24を記憶する記憶部23と、データテーブル24に基づいてHPA6への入力信号S1を補正することにより、歪補償処理を実行する歪補償部21と、データテーブル24の更新処理を実行する更新部30と、を備え、更新部30が、データテーブル24の一部の領域に関して、補正データの読み出しを制限した状態で更新処理を実行しつつ、歪補償部21が、データテーブル24の他の領域に基づいて歪補償処理を実行する。

(もっと読む)

容量性負荷駆動回路

【課題】電源電圧を超えた電圧の駆動信号を発生させることが可能で、しかも環境温度や

部品の製造ばらつきの影響を受けることなく安定した駆動信号を発生させることが可能な

技術を提供する。

【解決手段】容量性負荷に印加すべき駆動信号の基準となる駆動波形信号を、パルス変調

することによって変調信号を生成し、得られた変調信号を電力増幅した後、平滑フィルタ

ーを用いて駆動信号を復調する。また、こうして得られた駆動信号を負帰還させることに

よって、平滑フィルターの共振ピークを抑制する。このとき、ピークを完全に抑制するの

ではなく、比較的広い周波数帯域でゲインが一定以上(たとえば2以上)となるようにす

ることで、電源電圧を超えた電圧の駆動信号を安定して発生させることが可能となる。

(もっと読む)

容量性負荷駆動回路

【課題】容量成分または誘導成分を有する容量性負荷の駆動信号を、安定してしかも電力

消費を抑制しながら生成する。

【解決手段】容量性負荷に印加すべき駆動信号の基準となる駆動波形信号を、パルス変調

することによって変調信号を生成し、得られた変調信号を電力増幅した後、平滑化するこ

とによって、駆動信号を生成する。また、こうして容量性負荷に印加された駆動信号を、

駆動信号の基準となる駆動波形信号に負帰還させる。このとき、駆動信号に含まれる周波

数帯域でのゲイン特性が平坦となるような所定のアナログ補償処理を駆動信号に対して加

えた後、得られた信号をデジタル信号に変換して、駆動波形信号に負帰還させる。

(もっと読む)

増幅器の位相補償回路及び増幅回路

【課題】増幅器の位相補償精度を向上させることができる増幅器の位相補償回路を提供することを課題とする。

【解決手段】増幅器の位相補償回路は、入力端子及び第1のノード間に接続される第1の容量(404)と、前記第1のノード及び第1の増幅器の入力端子間に接続される第2の容量(405)と、ゲートが前記第1のノードに接続され、ソース及びドレインが第1の電位ノードに接続される第1の電界効果トランジスタ(406)と、前記入力端子の信号のエンベロープを検出するエンベロープ検出回路(411,412)と、前記エンベロープ検出回路により検出されたエンベロープを増幅し、前記第1のノードに出力する第2の増幅器(413)とを有する。

(もっと読む)

スイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器

【課題】所望の信号伝達関数でより一層の出力雑音成分を低減できるスイッチトキャパシター回路、フィルター回路、物理量測定装置及び電子機器等を提供する。

【解決手段】スイッチと、複数のサンプリング容量と、積分容量とを含んで構成されるスイッチトキャパシター積分回路10は、電荷充電期間T1の入力信号に対応した電荷をサンプリング容量の少なくとも1つに充電する。スイッチトキャパシター積分回路10は、電荷転送期間T2において、該電荷を積分容量に転送することで、該電荷に対応した信号を伝搬遅延させる。スイッチトキャパシター積分回路10は、例えばスイッチにより複数のサンプリング容量の接続を切り換えることにより、電荷充電期間T1にて決定される信号伝達関数と、電荷転送期間T2にて決定される雑音伝達関数とを異ならせる。

(もっと読む)

通信装置および歪補償方法

【課題】DPD方式の歪補償機能を有する簡易な構成の通信装置および当該通信装置の歪補償方法を提供することである。

【解決手段】サーキュレータ12は、第1、第2、第3の端子を備える、第1の端子は、送信信号処理部201からの送信信号を受け、第2の端子は、送受信アンテナ10からの受信信号を受けるとともに、送受信アンテナ10へ第1の端子から入力された送信信号を出力し、第3の端子は、第2の端子から入力された受信信号を出力し、かつ第1の端子から入力された送信信号が漏れ出した信号をフィードバック信号として出力する。受信信号およびフィードバック信号処理部204は、受信信号に対して増幅を行なう低雑音増幅器26を含むとともに、受信信号およびフィードバック信号に対して無線周波波数帯から中間周波数帯への周波数変換を行なう。フィードバック信号は、さらに歪補償部56に入力される。

(もっと読む)

電気音響変換器用増幅器

【課題】DCサーボの動作が音声信号回路に影響を及ぼすことがなく、かつ、音声入力時であっても常時DCサーボが動作して、オフセットやドリフトによる直流電流の出力を効果的に防止することができる音響変換器用直流増幅器を得る。

【解決手段】コンプリメンタリー接続された複数のトランジスタTR1,TR2を備えている。出力信号の直流レベルに対応した光量を放射する発光素子1と、発光素子1から放射される光を受光し受光量に応じて抵抗値が変化する受光素子2を備え、受光素子2の抵抗値の変化で複数のトランジスタTR1,TR2のバイアスを変化させオフセットおよびドリフトを制御する。

(もっと読む)

出力スイッチング回路

【課題】アナログ回路の規模をできるだけ小さくした出力スイッチング回路を提供する。

【解決手段】出力スイッチング回路1は,高電源に接続された第1のトランジスタ31と低電源に接続された第2のトランジスタ32とを有し第1,第2のトランジスタ31,32の接続ノードを出力端子33とするスイッチング回路30と,出力端子33の出力信号Voをローパスフィルタ40を介してフィードバックしたフィードバック信号FBと,入力信号Inとを比較し,比較信号Vcompを生成する比較ユニット10と,比較信号Vcompに応じて第1,第2のトランジスタ31,32を駆動する第1,第2の駆動パルスVp,Vnを生成する駆動パルス生成ユニット20とを有する。

(もっと読む)

チョッパスタビライズドアンプ

【課題】演算増幅回路が有限の周波数特性およびスルーレートを有することに起因して発生するグリッチングを抑制し、高調波歪のより少ない出力信号を得ることができるチョッパスタビライズドアンプを提供する。

【解決手段】変調回路MODは、所定の周波数を有する矩形波である変調信号を使って、入力信号をデジタル的に第1の被変調信号に変換する。演算増幅回路AMPは、第1の被変調信号を増幅して、第2の被変調信号に変換する。復調回路DEMODは、第1の被変調信号と第2の被変調信号の周波数成分の違いに対応する波形をもった復調信号を使って、アナログ的に第2の被変調信号を出力信号に変換する。

(もっと読む)

電荷検出回路

【課題】差動アンプの入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動アンプ3の負極入力端子に接続され、他端が前記差動アンプ3の正極入力端子に接続され、前記差動アンプ3の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動アンプの正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動アンプの負極入力端子及び正極入力端子の少なくとも一方に逆バイアス電源7,9によって逆バイアス電位が与えられた可変容量ダイオードD1,D2を接続してゲイン調整を可能とした。

(もっと読む)

集積回路装置及び電子機器

【課題】センサーデバイスのチャネル信号が第1、第2信号で構成される場合に第1、第2信号の差分に対応する信号の精度の高いA/D変換を実現する集積回路装置等の提供。

【解決手段】集積回路装置は、センサーデバイスからの第1信号SG1が第1期間において入力され、第1信号SG1とペアーとなってセンサーデバイスのチャネル信号を構成する第2信号SG2が第2期間において入力され、第1信号SG1と第2信号SG2の差分に対応する信号を出力する増幅回路と、増幅回路の出力信号についてのA/D変換を行うA/D変換器を含む。増幅回路は、増幅回路が有する演算増幅器のオフセット電圧をキャンセルするスイッチドキャパシター回路により構成される。

(もっと読む)

電荷検出回路

【課題】差動増幅回路の入力側のゲイン調整を容易に行うことができる電荷検出回路を提供する。

【解決手段】電荷発生型センサ及び容量変化型センサの何れかで構成される物理量検出センサ1A,1Bの一端が差動増幅回路1の負極入力端子に接続され、他端が前記差動増幅回路1の正極入力端子に接続され、前記差動増幅回路1の出力端子と前記負極入力端子との間にフィードバック抵抗Rf及びフィードバック容量Cfが並列に接続され、且つ前記差動増幅回路1の正極入力端子と基準電圧との間にキャンセル抵抗Rc及びキャンセル容量Ccが並列に接続された差動型の電荷検出回路であって、前記差動増幅回路1の正負の差動入力が個別入力される2つの電界効果トランジスタFET1,FET2の少なくとも一方のドレイン電圧を調整するドレイン電圧調整回路12,13を設け、前記正負の差動入力の少なくとも一方のゲイン調整を可能とした。

(もっと読む)

増幅器及びそれを用いた無線送信機

【課題】元のパルス変調されたパルス信号を、パルス系列を維持した上で増幅することを可能にする。

【解決手段】本開示の一形態に係る増幅器100は、パルス信号を分離する分離部120と、各分離パルス信号に含まれる最も狭いパルス幅の2倍以上のパルス幅を有する第1、第2低速パルス信号を生成する生成部130とを備える。その増幅器100は、第1分離パルス信号に対応する第1と第2低速パルス信号の論理積を第1出力パルス信号として出力する第1スイッチングアンプ群140と、第2分離パルス信号に対応する第1と第2低速パルス信号の論理積を第2出力パルス信号として出力する第2スイッチングアンプ群140とを備える。その増幅器100は、記第1出力パルス信号と前記第2出力パルス信号との論理和を出力する出力部150とを備える。

(もっと読む)

包絡線増幅器

【課題】回路構成を簡素化し、消費電流を削減する。

【解決手段】入力される包絡線信号の振幅に応じて第1の電流(Isense)を出力する第1の出力部(PMOS216、NMOS220が相当)と、第1の電流の電流値に比例し、第1の電流の電流値よりも絶対値が大きな電流値である第2の電流(Imain)を出力する第2の出力部(PMOS218、NMOS222が相当)と、を有する増幅器(206が相当)と、第1の電流の電流値を判断する比較部(208aが相当)と、比較部の判断結果に応じて断続される電流をインダクタ(228が相当)を介し第2の電流と加算して出力端から出力する出力部(210が相当)と、を備え、第1の電流を出力部に供給することなく終端するように構成する。

(もっと読む)

変調電源

【課題】広帯域増幅部に供給するDC電圧幅を大電圧高速変調電源の出力電圧幅よりも低くすることができ、広帯域増幅部における電力損失を低減することができる変調電源を提供すること。

【解決手段】大電圧高速変調電源100は、多値DC電圧源111から供給された複数のDC電圧を入力AM信号に応じて離散的に切り換え出力するDC電圧切換部112と、DC電圧切換部112の出力電圧を基準電位とするフローティング構造のDC電圧源150と、DC電圧源150を電源電圧とし、入力信号を線形に増幅する広帯域増幅部120と、広帯域増幅部120を流れる瞬時電流を検出する電流検出部130と、広帯域増幅部120に流れる瞬時電流に応じて供給されるDC電圧をオン/オフ制御するスイッチング部141とを備える。スイッチング部141は、広帯域増幅部120の動作電流が一定範囲内に収まるようにオン/オフ制御する。

(もっと読む)

81 - 100 / 792

[ Back to top ]