Fターム[5J500AM08]の内容

Fターム[5J500AM08]に分類される特許

1 - 20 / 681

D級増幅器

制御回路および位相変調器

駆動回路、及び、光送信装置

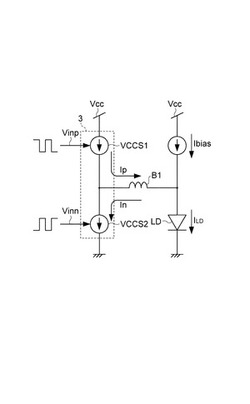

【課題】変調信号の大きさ及び応答速度を向上可能な駆動回路及び光送信装置を提供する。

【解決手段】差動信号の入力に応じて発光素子LDの駆動電流を増減する駆動回路3である。差動信号の正相信号Vinpが入力される端子と、差動信号の逆相信号Vinnが入力される端子と、発光素子LDのアノードに接続されている端子と、正相信号Vinpが入力される端子に接続されている正相信号処理回路と、逆相信号Vinnが入力される端子に接続されている逆相信号処理回路と、アノードが接続されている端子に接続されている第1及び第2の電圧制御電流源回路を備える。第1の電圧制御電流源回路には、正相信号Vinpに対応する電圧及び逆相信号Vinnの逆相に対応する電圧が入力され、第2の電圧制御電流源回路には、逆相信号Vinnに対応する電圧及び正相信号Vinpの逆相に対応する電圧が入力される。

(もっと読む)

可変利得増幅システム

【課題】入力および出力オフセット補正機能を備えたCCD信号処理チャネルを提供する。

【解決手段】本可変利得増幅回路は、入力信号から不要の相関ノイズ成分を除去する相関二重サンプリング回路1202と、相関二重サンプリング回路の下流側に位置する第1プログラマブル利得増幅器104と、入力が前記第1プログラマブル利得増幅器の入力に接続され、出力が相関二重サンプリング回路の入力に接続され、入力信号のオフセットおよび相関二重サンプリング回路のオフセットのうちの少なくともいずれか一方のために第1オフセット補正を提供する第1オフセット補正回路500と、第1プログラマブル利得増幅器の下流側に位置するアナログ/ディジタル変換器106と、第1プログラマブル利得増幅器の下流側に位置し、第2オフセット補正を提供する第2オフセット補正回路502と、相関二重サンプリング回路の下流側であって、かつ、第1プログラマブル利得増幅器の上流側に位置する画素利得増幅器1204を備えている。

(もっと読む)

電力増幅器

【課題】素子ばらつきや周波数特性に対して鈍感であり低損失な電力増幅器を得る。

【解決手段】入力端子INから入力した入力信号を増幅素子Tr1が増幅する。増幅素子Tr1の出力信号を増幅素子Tr2が増幅する。増幅素子Tr2の出力信号は出力端子OUTから出力される。増幅素子Tr2の出力と出力端子OUTとの間に整合回路M3が接続されている。増幅素子Tr1の出力と増幅素子Tr2の入力との間にスイッチSW1が接続されている。増幅素子Tr1の出力にスイッチSW2の一端が接続されている。整合回路M4の一端がスイッチSW2の他端に接続され、整合回路M4の他端が増幅素子Tr2の出力に直接に接続されている。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

同相電圧帰還回路及び全差動演算増幅器

【課題】クロックフェイズの切り替わりにおける電圧スパイクの低減と共に出力電圧の収束速度の向上を図る。

【解決手段】第1及び第2の同相電圧検出器301,302は、ノンオーバーラップ期間が設定された2相クロックで駆動され、第1の同相電圧検出器301は、第1のクロック位相において充電動作し、第2のクロック位相において出力同相電圧の生成と電荷保持動作をし、第2の同相電圧検出器302は、第2のクロック位相において充電動作し、第1のクロック位相において出力同相電圧の生成と電荷保持動作をし、ノンオーバーラップ期間において、第1及び第2の同相電圧検出器301,302は、スイッチ35a〜35f、36a〜36fにより入力段及び出力段と電気的に分離され、同相電圧出力トランジスタのゲート・ソース間寄生容量により電荷保持動がなされる構成となっている。

(もっと読む)

光受信回路用信号増幅器

【課題】受信した光信号を電流信号に変換する受光素子に接続される信号増幅器において、メインアンプの入力段の入力インピーダンスが無視できないときに設けられるレベル調整抵抗の影響を少なくし、広帯域の周波数特性と高い光受信感度特性とを得る。

【解決手段】信号増幅器は、電流信号を電圧に変換して出力するプリアンプと、少なくとも入力段が差動回路からなりプリアンプから出力された電圧信号を増幅するメインアンプと、プリアンプとメインアンプとの間に設けられ電圧信号が供給される2個以上のフォロワ回路と、プリアンプの出力とメインアンプの各入力との間の経路において各フォロワ回路ごとに設けられる抵抗値が等しい抵抗と、抵抗のうちの1つに対して一端が接続し、他端が接地されたコンデンサと、を備えている。コンデンサとそのコンデンサに接続する抵抗とによって、電圧信号の平均電位を検出するローパスフィルタが構成されている。

(もっと読む)

対数/逆対数変換回路

【課題】温度補正を行なわなくても、逆対数変換した際に得られる出力信号が線形性を保つことができる対数/逆対数変換回路を提供する。

【解決手段】対数変換回路1の電流帰還用トランジスタTR2を通過した電流信号Iinを逆対数変換回路2に入力し、電流/電圧変換回路3でこの電流信号Iinをこれに対応した電圧値に変換した後、引算回路4で電流/電圧変換回路3の出力電圧と予め設定された基準電圧との差分を出力する構成とし、かつ引算回路4はその差分出力が電流信号Iinに比例した線形性をもつように回路定数を設定している。

(もっと読む)

出力回路及びデータドライバ及び表示装置

【課題】高速動作に対応可能とし、消費電力を抑制可能とし面積も抑制可能とする出力回路の提供。

【解決手段】出力回路は、差動入力段10と出力増幅段20と増幅加速回路70を備え、増幅加速回路70は、入力対が入力端子1と出力端子2に夫々接続された差動対171、172と、第5の電源端子E5と前記差動対の出力対間にそれぞれ接続された負荷素子対174、175を備え、差動対171、172の入力電位差によって、差動入力段10の第2のカレントミラー40の入力が接続する第4のノードN4への電流供給を制御する第1の電流源回路176と、差動入力段10の第1のカレントミラー30の出力が接続する第1のノードN1への電流供給を制御する第2の電流源回路178を含む。

(もっと読む)

高周波増幅回路および無線通信装置

【課題】低負荷の素子を駆動可能にすることで出力インピーダンスを低く抑えることが可能な増幅回路を提供する。

【解決手段】入力信号を増幅するn段構成の増幅回路と、n段目の前記増幅回路と(n+1)段目の前記増幅回路との間に設けられる(n−1)個のインピーダンス変換器と、を備え、前記(n−1)個のインピーダンス変換器は、前記増幅回路間の電力反射を抑制できるインピーダンス変換を行うことを特徴とする、増幅回路が提供される。かかる構成により、増幅回路は、低負荷の素子を駆動可能にすることで出力インピーダンスを低く抑えることが可能となる。

(もっと読む)

増幅器

【課題】歪の発生を少なくする。

【解決手段】入力信号(IN)を受ける初段増幅回路(PREA)と、ゲートに初段増幅回路(PREA)の出力信号を受けるソース接地の第1のトランジスタ(Tr1)と、ソースを第1のトランジスタ(Tr1)のドレインに接続し、ドレインから出力信号(OUT)を送出すると共にドレインに対して電源供給がなされるゲート接地の第2のトランジスタ(Tr2)と、初段増幅回路(PREA)の電源端と第2のトランジスタ(Tr2)のソースとの間に介在する第1のインピーダンス回路(Z1)と、を備える。第1のインピーダンス回路(Z1)は、直流を通過させると共に、所定の周波数帯域において所定のインピーダンス以上となるように構成された回路である。

(もっと読む)

増幅回路および帰還回路

【課題】反転入力容量Csinが異なる場合、帰還容量Cfが小容量の固定値であっても、周波数特性の肩特性の劣化やピークがほとんど生じない増幅回路および帰還回路を提供する。

【解決手段】個別に負帰還をかけるとともに直列に接続された複数の増幅器と、前記複数の増幅器に含まれる出力側の増幅器の出力側と入力側の増幅器の入力側に接続された帰還手段(帰還回路)とを備え、前記複数の増幅器は奇数個の反転増幅器を含む構成である。

(もっと読む)

差動増幅器

【課題】出力電圧の出力精度に段差が発生していた。

【解決手段】電流源で駆動される第1、第2の差動対と、その電流源を駆動する第1の基準電流発生回路と、を備える第1の差動入力部と、電流源で駆動される第3、第4の差動対と、その電流源を駆動する第2の基準電流発生回路と、を備える第2の差動入力部と、前記第1、第2の差動入力部との出力に応じて、出力する出力部と、を有し、前記第1、第2の基準電流発生回路の第1、第2の電流経路上に接続される第1、第2のトランジスタを入力信号に応じて制御することで、前記第1、第2の差動入力部の出力を制御する差動増幅器。

(もっと読む)

RF電力増幅器およびその動作方法

【課題】ランプアップまたはランプダウンにおいてスイッチングスペクトラムの劣化を軽減すること。

【解決手段】初段と最終段のバイアス回路81、83が、初段と最終段の増幅回路41、43のアイドリング電流を決定する。電力検出回路5、6は、最終段出力信号Poutの信号レベルに応答する電力検出信号VDETを生成する。誤差増幅器7に検出信号VDETと目標電力信号VRAMPが供給され、電力制御電圧VAPCが制御信号増強回路9の入力に供給され、出力から増強制御信号VENを生成する。制御信号増強回路9は、所定の非線型の入出力特性を有する。増強制御信号VENが初段と最終段のバイアス回路81、83とに供給され、初段と最終段の増幅回路41、43のアイドリング電流は増強制御信号VENによって制御され、RF電力増幅器の制御利得の低下が補償される。

(もっと読む)

高速プリアンプ回路、検出電子機器、および放射線検出システム

【課題】高速プリアンプ回路、検出電子機器、および放射線検出システムを提供する。

【解決手段】プリアンプ回路は、放射線検出器から電流信号を受信して、増幅電圧信号を生成するトランスインピーダンス・アンプを備える。トランスインピーダンス・アンプの出力は、第2増幅ステージに接続される。検出電子機器は、検出器上の第1位置から電流信号を受信して第1電圧信号を生成する第1トランスインピーダンス・アンプと、検出器上の第2位置から電流信号を受信して第2電圧信号を生成する第2トランスインピーダンス・アンプとを有する。第2増幅ステージは、第1増幅電圧信号と第2増幅電圧信号とを与える。差動出力ステージは、第1増幅電圧信号と第2増幅電圧信号を受信し、各々から一対の出力を提供する。読取回路類は、一対の出力の各々を処理する処理構造を有する。処理構造は、タイムスタンプを有する単一のデジタル出力を提供する。

(もっと読む)

半導体集積回路装置

【課題】 差動増幅回路の出力信号の特性を改善する。

【解決手段】入力データ信号が‘Low’レベルになると、トランジスタ16に流れる電流I1の電流が減少し、抵抗14と抵抗14aとの接続部(ノードD)の電位が高くなる。この電位は、トランジスタ18にゲートに入力(負帰還)され、該ゲート電位が高くなることによって、テイル電流量I_TAILが増加する方向に調整される。入力データ信号が‘High’レベルになると、電流I1の電流が多く流れ、ノードDの電位が下がる。これによって、トランジスタ18のゲート電位(負帰還)が下がり、テイル電流量I_TAILを絞る方向に調整される、これによって入力波形の立上りと立下りとで、それぞれ出力波形との遅延時間の差が小さくなる。

(もっと読む)

電力増幅回路

【課題】電力増幅回路の周波数特性を広帯域化する。

【解決手段】それぞれが互いに異なる周波数(f1−fn)で整合が取られた差動プッシュプル増幅器(PA1−PAn)の出力を、二次インダクタ(L12−Ln2)で共通に合成して出力する。各差動プッシュプル増幅器は、差動信号入力端子にぞれぞれ接続される増幅器対で構成され、差動プッシュプル増幅器の出力にはキャパシタ(C1−Cn)とインダクタ(L11−L1n)の並列共振回路を接続し、共振周波数を変更して整合周波数を調整する。

(もっと読む)

電力増幅回路

【課題】電源電圧が瞬時低下しても所望の出力波形を出力し続けることが可能な電力増幅回路を提供する。

【解決手段】電力増幅回路は、第1および第2のオペアンプを備える。電力増幅回路は、第1ないし第4の帰還抵抗を備える。電力増幅回路は、非反転入力端子が第1のオペアンプの出力端子に接続され、反転入力端子が第2のオペアンプの出力端子に接続され、非反転出力端子が第1の信号出力端子に接続され、反転出力端子が第2の信号出力端子に接続され、差動利得を一定に保つ全差動オペアンプを備える。電力増幅回路は、第2の帰還抵抗の他端と接地との間に接続されたスイッチ回路を備える。電力増幅回路は、第1の信号入力端子と基準電圧が印加される基準端子との間に接続された第1の入力抵抗を備える。電力増幅回路は、第2の信号入力端子と基準端子との間に接続された第2の入力抵抗を備える。電力増幅回路は、電源電圧を監視し、電源電圧の値に応じてスイッチ回路を制御する中点電位制御回路と、を備える。

(もっと読む)

出力回路

【課題】2つの出力信号間のタイミングのずれを低減すること。

【解決手段】入力信号IN,XINはトランジスタM1,M2のゲートに供給される。トランジスタM1のドレインはトランジスタM3のドレインとトランジスタM4のゲートに接続され、トランジスタM2のドレインはトランジスタM3のゲートとトランジスタM4のドレインに接続される。また、トランジスタM1,M2のドレインは差動対のトランジスタM11,M12のゲートに接続される。トランジスタM3,M4のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM5が接続される。トランジスタM11,M12のソースには、ゲートにバイアス電圧VBが供給されるトランジスタM13が接続される。

(もっと読む)

1 - 20 / 681

[ Back to top ]