Fターム[5J500AM13]の内容

増幅器一般 (93,357) | 接続及び構成 (5,069) | フィードバック(帰還)構成 (1,498) | 負帰還(単なるエミッタ帰還抵抗を除く) (832)

Fターム[5J500AM13]に分類される特許

201 - 220 / 832

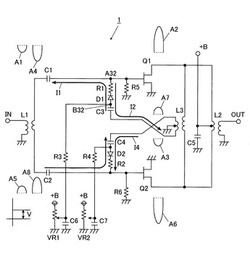

増幅器及び無線機器

【課題】増幅器の入出力特性の直線性が悪化することを防ぐこと。

【解決手段】一対のFET素子Q1,Q2の出力側の各々の間に1次側の両端が接続され、2次側の両端よりFET素子Q1,Q2から出力される信号を降圧した降圧信号を出力する帰還用トランスL3と、FET素子Q1,Q2の入力側の各々と、FET素子Q1,Q2の入力側の位相と同相となる降圧信号を出力する帰還用トランスL3の2次側の各々との間に、FET素子Q1,Q2の入力側に向かって整流する方向に接続された整流用ダイオードD1,D2と、整流用ダイオードD1,D2を介してFET素子Q1,Q2の入力側にバイアス電圧またはバイアス電流を供給するバイアス回路と、を備える。

(もっと読む)

歪補償装置、増幅装置、送信装置および歪補償方法

【課題】信号の歪を精度よく補償すること。

【解決手段】歪補償装置110は、増幅器120による信号の歪を補償する。乗算部111は、歪補償係数を用いて入力信号に歪補償を行う。LUT114aは、歪補償係数を記憶する。アドレス生成部112は、入力信号の電力値に基づいてLUT114aから歪補償係数を取得するための第1のアドレスを生成する。アドレス生成部112は、入力信号の電力値に応じて正規化する範囲を決定した、電力値もしくは入力信号の位相もしくは入力信号の振幅値に基づいてLUT114aから歪補償係数を取得するための第2のアドレスを生成する。

(もっと読む)

D級電力増幅装置

【課題】スイッチング電源を使用したD級電力増幅装置において、回路規模を大きくすることなくビートノイズを低減し、出力レベルが大きいときのTHDの悪化を防止することを目的とする。

【解決手段】D級電力増幅装置は、スイッチング電源と同期信号生成部と自励式D級電力増幅部とを備える。同期信号生成部は、スイッチング電源からスイッチング周波数のn倍の第2周波数のクロック信号を取り出す。自励式D級電力増幅部は、入力信号を帰還信号と比較する比較器と、該比較器の出力に基づき供給電源をスイッチングする第2スイッチング部と、その出力を平滑して出力信号を取り出すフィルタ部と、その出力信号の位相を遅らせるとともに同期信号生成部からのクロック信号と合成して、帰還信号を生成する合成部とを備え、入力信号のレベルが小さいときは前記第2周波数で自励発振する。

(もっと読む)

OFDM変調器

【課題】高出力であっても歪を補償する。

【解決手段】入力信号に応じたベースバンド信号と、増幅器からのフィードバック信号との誤差を抽出する誤差抽出部32と、誤差抽出部32にて抽出された誤差信号を所定のサンプル毎に抽出する平均サンプル選択部33と、平均サンプル選択部33にて抽出された誤差信号の平均値を算出する平均計算部34と、所定のサンプル毎に算出された平均値の間を補間する補間計算部35と、補間計算部35にて補間された誤差信号の平均値に基づいて歪を推定し、その歪から歪補償用のデータを生成する補償データ生成部36とを有する。

(もっと読む)

バンドギャップリファレンス回路および回路を製造する方法

【課題】最低所要供給電圧が低く、小さいチップ領域を占め、電流消費が低く、供給電圧の変動に強いバンドギャップリファレンス回路を提供する。

【解決手段】電圧ジェネレータ(VG)と、供給回路(SC)と、バイアス要素(BB)および制御要素(CB)を含むバイアス回路(BC)とを、バンドギャップリファレンス回路は含む。供給回路(SC)の制御要素(CS)およびバイアス回路(BC)の制御要素(CB)のうちの一つは、擬似格子整合型高電子移動度トランジスタまたはヘテロ接合バイポーラトランジスタを含み、供給回路(SC)のバイアス要素(BS)およびバイアス回路(BC)のバイアス要素(BB)のうちの一つは、ロングゲート擬似格子整合型高電子移動度トランジスタまたは抵抗を含む。擬似構成整合型高電子移動度トランジスタおよびヘテロ接合バイポーラトランジスタは、GaAs BiFET技術プロセスを用いて製造される。

(もっと読む)

電子回路および電子装置

【課題】小容量のキャパシタンス素子を介して信号検出可能な高入力インピーダンスの緩衝増幅回路を、極端に高抵抗値、高容量値の抵抗器やコンデンサーコンデンサーを用いずに実現する。また、誘導ノイズや帯電物の接近等による電位変動等の妨害に強い電子装置を提供する。

【解決手段】第一の非反転増幅回路と、前記第一の非反転増幅回路に入力信号を接続するキャパシタンス素子と、第二の非反転増幅回路と、前記第一の非反転増幅回路の出力信号を前記第二の非反転増幅回路に入力するコンデンサーと、前記第二の非反転増幅回路の出力信号を前記第一の非反転増幅回路に入力する抵抗器と、前記非反転増幅回路の入力と所定の電位間に接続されたスイッチ回路を含んで構成することによって電子回路を構成する。

(もっと読む)

スイッチトキャパシタアンプ

【課題】安定した出力電圧を出力できるスイッチトキャパシタアンプを提供する。

【解決手段】スイッチトキャパシタアンプは入力容量18と出力容量19との充放電時間差が無くなるよう動作できるので、ホールド状態からサンプル状態への移行時、例えば、出力容量19の一端の電圧V2が出力電圧VOUTに急激に高くなっても、出力容量19の他端の電圧Vsは急激に高くならない。つまり、内部アンプ11への入力電圧は急激に高くならない。よって、内部アンプ11の出力電圧が安定するので、出力電圧VOUTも安定する。

(もっと読む)

スイッチトキャパシタ回路

【課題】スイッチトキャパシタ回路におけるシングル/差動変換時の演算増幅器の同相入力変動を抑制し、低電源電圧での変換、または高速の変換にも対応することが可能なスイッチトキャパシタ回路を実現する。

【解決手段】サンプリングモード時とホールドモード時とで演算増幅器110の入力側のキャパシタC1〜C4をスイッチ回路SWで切り換えて単相入力信号を差動出力信号に変換するについて、サンプルモード時にサンプリング用キャパシタC1、C2、C3、C4の一端側に供給する第2の入力信号(電圧VH)を第1の信号入力電圧VIPと第1の参照信号電圧VINの中間の電圧とするような電圧生成部20を設けた。

(もっと読む)

電子回路および電子装置

【課題】小容量のキャパシタンス素子を介して信号検出可能な高入力インピーダンスでかつひずみの少ない緩衝増幅回路を、極端に高抵抗値、高容量値の抵抗器やコンデンサーを用いずに実現する。

【解決手段】非反転増幅回路と、前記非反転増幅回路に入力信号を接続するキャパシタンス素子と、前記非反転増幅回路の出力信号を分圧する分圧回路と、該分圧回路信号を前記非反転増幅回路の入力端子に帰還するインピーダンス素子を含んで構成する。

(もっと読む)

通信装置および電力補正方法

【課題】ユーザ設定される送信周波数において最大送信電力を得ることができる。

【解決手段】演算部6は、送信信号と増幅器2で増幅された送信信号のフィードバック信号とに基づいて歪補償係数を算出する。記憶部4は、通信装置の送信電力の周波数特性を記憶する。補正部5は、記憶部4を参照してユーザ設定される送信周波数の電力を算出し、算出した電力と通信装置に規定された最大送信電力とに基づいて、ユーザ設定の送信周波数で最大送信電力が得られるようフィードバック信号を補正する。

(もっと読む)

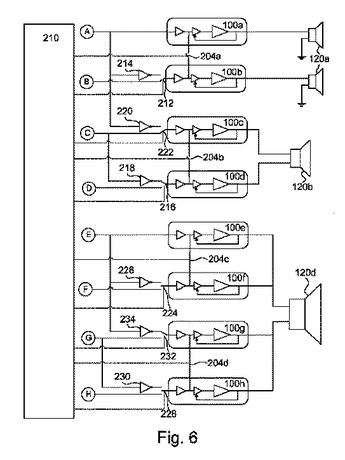

汎用オーディオ電力増幅器

オーディオ電力増幅器が、第1および第2の増幅ユニットを含み、それぞれが、スイッチング電圧増幅器と、出力フィルタと、電流補償器と、出力インダクタにおいて測定された電流の測定値を電流補償器の加算入力にフィードバックする内側電流フィードバックループと、電流補償器の加算入力に結合された電圧補償器と、外側電圧フィードバックループとを備えている。制御された信号経路が、第1の増幅ユニットの電圧補償器の出力を、第2の増幅ユニットの電流補償器に提供する。第1および第2の増幅ユニットは、別々の負荷と共に、共通の負荷を並列に駆動するように、またはブリッジ接続された負荷にわたって動作可能である。増幅ユニットの第2の対を追加して、第1の対と共に動作させて、ブリッジ接続された負荷のそれぞれの側で並列の対の増幅器を用いて単一のスピーカを駆動することができる。  (もっと読む)

(もっと読む)

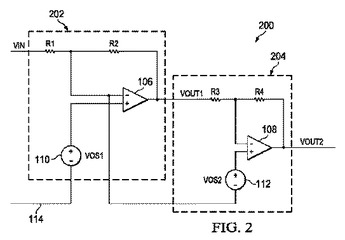

マルチステージシステムにおける増幅器オフセット及びノイズ低減

マルチステージ増幅器システム(200)が、一層良好な整合構成要素及び/又はトリム回路の必要性を低減する、ノイズ及びオフセット寄与を提供する。入力(VIN)を受け取り、出力(VOUT1)を供給する第1の増幅器(106)を有する第1の増幅器ステージ(202)が、第1のオフセット電圧(VOS1)を第1の増幅器ステージに提供し、供給レール(114)に結合される、第1のオフセット電源(110)を含む。出力(VOUT1)を入力として受け取り、出力(VOUT2)を提供する第2の増幅器(108)を有する第2の増幅器ステージ(204)が、第2のオフセット電圧(VOS2)を第2の増幅器ステージに提供する第2のオフセット電源(112)を含む。第2のオフセット電源は、第1のオフセット電圧からのノイズ寄与を低減するように第1の増幅器ステージに結合される。  (もっと読む)

(もっと読む)

交流信号発生装置

【課題】簡単な構成で減衰交流信号を発生させることが可能な交流信号発生装置を提供すること。

【解決手段】交流信号発生装置は、周波数が僅かに異なる2つの矩形波を発生させる矩形波発生手段として機能するマイクロコンピュータと、2つの矩形波を入力し、一方の矩形波の電圧値から他方の矩形波の電圧値を減算した差を出力する両極性の差動増幅回路と、アクティブフィルター回路によって構成され、交流信号を出力する低域通過型フィルター回路とを備える。マイクロコンピュータは、2つの矩形波の初期の位相差が180度であり、2つの矩形波の位相差が0になる時点で矩形波の発生を終了する。特に減衰のための回路を必要とせず、外付け部品等による影響を殆ど受けずに安定した減衰信号が得られる。

(もっと読む)

バイアス回路、LNA、LNB、通信用受信機、通信用送信機、およびセンサーシステム

【課題】温度依存性の低減、電源電圧依存性の低減、電源電圧および負電圧に重畳されている雑音の十分な減衰、製造プロセスの選定自由度の向上、を実現することができるバイアス回路、LNA、LNB、通信用受信機、通信用送信機、およびセンサーシステムを提供する。

【解決手段】ソース端子4が接地されたHEMT1のためのHEMTバイアス回路11であって、両電源型のオペアンプAMP1と、抵抗素子RIと、第1基準電圧源VXと、第2基準電圧源VYとを備え、オペアンプAMP1は、正入力端子がHEMT1のドレイン端子3に接続され、負入力端子が第2基準電圧源VYに接続され、出力端子がHEMT1のゲート端子に接続され、抵抗素子RIは、一方の端子がHEMT1のドレイン端子3に接続され、他方の端子が第1基準電圧源VXに接続されている。

(もっと読む)

光受信器

【課題】バランスド受光入力に対応し、入力光電力によらず、出力振幅が入力振幅によらず常に一定振幅であり、ファイバ伝送状態により変化する入力に対し、自動利得制御が追従する広帯域な動作ができる光受信器を提供する。

【解決手段】受信した光信号を電気信号に変換する光受信手段と、この光受信手段からの電気信号を増幅する増幅手段と、この増幅手段で増幅された信号に対して線形動作を行い、線形動作を行った後に、入力振幅に対して一定の振幅を出力する利得制御手段を備えることを特徴とする。

(もっと読む)

増幅装置

【課題】 音声入力端子とアンプ回路との間に入力音声信号の有無を検出する検出回路を設けることなく、無音時に消費電力を低減すること。

【解決手段】 AVアンプ1は、入力音声信号を増幅し、出力音声信号を出力するアンプ回路4と、アンプ回路4から出力される出力音声信号の信号レベルを検出する信号レベル検出手段と、信号レベル検出手段によって検出された、アンプ回路4から出力される出力音声信号の信号レベルが、無音判断基準値未満である状態が、所定時間以上継続したか否かを判断する第1信号レベル判断手段と、アンプ回路4から出力される出力音声信号の信号レベルが無音判断基準値未満である状態が所定時間以上継続した場合に、AVアンプ1を電源オン状態から電源オフ状態に移行させる電源制御手段とを備える。

(もっと読む)

広帯域高出力増幅器

【課題】広帯域増幅器の出力不整合と周波数切り替え回路で発生する不整合を調整し、高効率化を図ることができる広帯域高出力増幅器を得る。

【解決手段】少なくとも2倍高調波が広帯域増幅器1自身の帯域に含まれる広帯域高出力増幅器において、広帯域増幅器1の後段に、周波数帯域に応じた信号出力の切り替えを行う周波数切り替え回路2と、インピーダンス不整合を調整する整合回路5と、周波数帯域に応じて高調波成分を抑制するフィルタ回路4とを順次接続し、インピーダンス調整用整合回路5は、広帯域増幅器1の出力不整合と周波数切り替え回路2で発生する不整合を調整する。

(もっと読む)

高パワー広帯域増幅器及び方法

【解決手段】実施形態によれば、高い供給電圧源と、低い供給電圧源と、2つの並列信号パスとを具備する増幅器を提供する。それぞれの信号パスは、前記高い供給電圧源及び前記低い供給電圧源に接続され、第1増幅器と第2増幅器とを具備する。前記2つの信号パスは共通の入力ノード及び共通の出力ノードでのみ互いに接続され、その結果前記それぞれの第1増幅器は互いに独立に動作する。前記第1増幅器は、入力電圧信号の少なくとも一部を信号電流へ変換する。複数の前記信号パスは、使用中の前記信号電流がそれぞれの前記第2増幅手段を駆動して増幅された出力電流を前記共通の出力ノードへ提供する。 (もっと読む)

ピーキング回路、ピーキング回路制御方法、波形測定装置、情報処理装置

【課題】ピーキング量を変化させるときに低周波域の増幅度に与える影響を抑えたピーキング技術を提供する。

【解決手段】本発明に係るピーキング回路は、多段接続された増幅回路と、入力側から見た増幅度が異なる2以上の出力点から入力側へフィードバックするフィードバック回路とを備え、フィードバック回路のフィードバック量を変化させることができるように構成されている。

(もっと読む)

半導体集積回路およびそれを用いた差動増幅器およびバッファアンプ

【課題】バイアス信号を切りかえに伴う動作特性の悪化を低減した半導体集積回路を提供する。

【解決手段】半導体集積回路10は、入力電流Iinを受け、それに応じた出力電流Iout1を別の回路に供給する。第1可変抵抗R1の第1端子は、入力端子P1と接続される。第1トランジスタM1および第2トランジスタM2は、電源端子と第1可変抵抗R1の第2端子の間に順に直列に設けられる。第3トランジスタM3および第4トランジスタM4は、電源端子と出力端子P2との間に順に直列に設けられる。第1トランジスタM1および第3トランジスタM3それぞれのゲートは第1可変抵抗R1の第2端子に接続される。第2トランジスタM2および第4トランジスタM4それぞれのゲートは入力端子P1に接続されている。第1可変抵抗R1は、その抵抗値が入力電流Iinに応じて切りかえ可能に構成される。

(もっと読む)

201 - 220 / 832

[ Back to top ]