Fターム[5K029AA18]の内容

直流方式デジタル伝送 (8,390) | 目的、効果 (1,587) | ハードウェアの簡単化 (195)

Fターム[5K029AA18]に分類される特許

1 - 20 / 195

符号化方法、復号化方法、伝送方法、符号化装置、復号化装置及び伝送システム

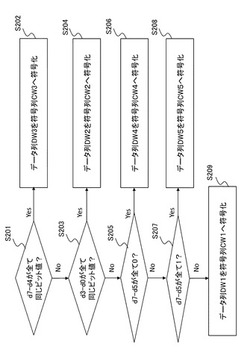

【課題】クロックエンベデッドシリアルデータ伝送を可能にするとともに、簡易な構成で符号化または復号化することを可能にする。

【解決手段】本発明に係る符号化方法は、入力されるデータ列の上位4ビットまたは下位4ビットにおいて同じビット値が連続するか否か判定し(S201、S203)、連続しないと判定された場合、隣接ビットと異なるビット値である反転ビットを中間ビットに有する符号列CW1へ、データ列を変換し(S209)、連続すると判定された場合、隣接ビットと同じビット値である連続ビットを中間ビットに有するとともに、反転ビットを上位ビット列または下位ビット列に有する符号列CW2,CW3へ、前記データ列を変換するものである(S202、S204)。

(もっと読む)

車両内通信システム

【課題】メーターECUと車両後端に配置した通信ECUとの間で直流電源の供給と信号の送受信を単一回路上で行なうことで車両後端に配置された複数のランプを操作する。

【解決手段】車両内通信システムは、インストルメントパネルに配置され、直流電源を供給するメーターECU(親機)1と、車両後端部に配置される通信ECU(子機)2と、メーターECU(親機)1および通信ECU(子機)2間を接続する単一の伝送路Lとを備える。メーターECU(親機)1は、スイッチの信号に応じて直流電源(バッテリー3)の電圧をパルス状列の電圧に変換する手段を備える。通信ECU(子機)2は、パルス状列の電圧を監視する手段を備える。

(もっと読む)

容量性通信回路及び通信方法

【課題】電気自動車、モータドライバのような分野では、高電圧領域と低電圧領域とが採用されており、安全性の理由から、それぞれの電圧領域を互いに分離(絶縁)させ、高電圧から高感度回路を保護する。

【解決手段】デジタルデータ信号の周波数とは異なる周波数を有するキャリア信号を用いてこのデジタルデータ信号を通信する通信回路は、第1の組のキャパシタと、第2の組のキャパシタと、第1の回路と、第2の回路とを有する。第1の回路は、キャリア信号及びこのキャリア信号の反転とそれぞれ混合された混合データ信号を発生させ、キャリア信号及びこのキャリア信号の反転とそれぞれ混合された混合反転データ信号を発生させ、混合データ信号を第1の組のキャパシタに供給し、混合反転データ信号を第2の組のキャパシタに供給する。第2回路は、混合信号からデータ信号を再生させる。

(もっと読む)

メモリカードとホストデバイスとの間で通信を実現するための回路および方法

【課題】UHS-IIモードと従来のモードのいずれかで信号を伝送するための、簡素かつ効率的な回路および方法。

【解決手段】インターフェース回路は、メモリカードとホストデバイスとの間の通信を実現する。インターフェース回路は、ピンの第1のセットと、ピンの第2のセットと、制御ユニットとを含む。制御ユニットは、ピンの第1のセットを介して第1のモードで信号の第1のセットを伝送する場合、ピンの第1のセットを有効にしてピンの第2のセットを無効にし、ピンの第2のセットを介して第2のモードで信号の第2のセットを伝送する場合、ピンの第1のセットを無効にしてピンの第2のセットを有効にする。制御ユニットは、ピンの第2のセットのクロックピンを介して、第2のモードで、差動シグナリングによって、信号の第2のセットのクロック信号を伝送する。第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。

(もっと読む)

信号授受方法、ビット列の伝送方法及びパック電池

【課題】認証機能を有するパック電池に接続される信号線を削減することが可能な信号授受方法、ビット列の伝送方法及びパック電池を提供する。

【解決手段】1及び0の夫々を伝送するパルスの幅が200μs及び100μsとされる伝送符号形式によって制御部から認証ICに伝送すべき第1ビット列(図3B参照)を、NRZ形式によって伝送されるべき第2ビット列(図3C参照)に変換し、変換した第2ビット列のMSBと、該第2ビット列が格納されたレジスタのMSBとが一致するようにしておく。そして、NRZ形式によって1及び0を伝送するパルス幅の計時を繰り返し、計時の開始毎に、レジスタのMSBに格納されているビットの値を、認証ICに出力される信号の伝送レベルに対応させた後に、レジスタを1ビット分左シフトさせる。

(もっと読む)

バイフェーズ符号化データの復号化方法

【課題】バイフェーズ符号化データの復号化方法を提供する。

【解決手段】本発明のバイフェーズ符号化データの復号化方法は、バイフェーズ符号化データ中の立下りエッジ変換を検出することによって、隣り合う2つの立下りエッジ変換の間の時間差値及び前1ビットの論理値に基づき、相応する復号化を行い、時間差値が1個ビット周期であり且つ前1ビットが論理1である時、現在のビットが論理1であると判定し、時間差値が1個のビット周期であり且つ前1ビットが論理0である時、現在のビットが論理0であると判定し、時間差値が1.5個のビット周期であり且つ前1ビットが論理1である時、現在及び後1ビットが何れも論理0であり、時間差値が1.5個のビット周期であり且つ前1ビットが論理0である時、現在のビットが論理1であると判定し、時間差値が2個のビット周期であり且つ前1ビットが論理1である時、現在及び後1ビットがそれぞれ論理0及び1であると判定する。

(もっと読む)

バスシステム

【課題】共通バスに接続された複数の電子機器の動作確認が短時間でできる安価なバスシステムを提供する。

【解決手段】車両ネットワークシステム1の下位ネットワークN2では、共通データ信号線43aに、電子機器33〜36と、中継コネクタユニット22と、が接続されている。各電子機器33〜36は、中継コネクタユニット22からの動作確認命令信号を受信したとき、共通データ信号線43aから所定時間にわたり電流を引き込む。各電子機器は、それぞれ同一の基準引込量の電流を引き込むように構成されている。中継コネクタユニット22は、各電子機器に対して動作確認命令信号を同報送信したのち、共通データ信号線43aから引き込まれる電流量を測定して、この電流量及び基準引込量から電子機器の応答数を算出し、この応答数及び電子機器の接続数に基づいて、各電子機器が正常に動作しているか否かを判定する。

(もっと読む)

通信システム

【課題】比較的安価な構成でリンギング現象を効果的に抑制可能な通信システムを得る。

【解決手段】幹線20の分岐点N1及びN3からそれぞれ放射状に6本の支線21、分岐点N2から図中上下に2本の支線22、合計14本の支線21及び22が接続される。なお、12本の支線21はそれぞれ第1の長さで設けられ、2本の支線22は上記第1の長さより長い第2の長さで設けられる。14本の支線21の端部に14個の非終端ECUであるECU2〜ECU15が接続される。ECU2〜7及び10〜15はそれぞれ抵抗値1800Ωの抵抗R2を有している。さらに、ECU8及び9はそれぞれ抵抗値600Ωの抵抗R3を有している。これら抵抗R2及び抵抗R3はリンギング現象抑制用の補助抵抗として機能する。

(もっと読む)

信号伝送システムおよび信号伝送方法

【課題】 伝送線路による信号伝送を行う伝送システムであって小型化が実現可能な信号伝送システムを実現する。

【解決手段】 誘電体層(1a)上の同一面内に配置された信号用号導体(2p1、2n1)と誘電体層(1a)を挟んで対向して配置された信号用導体(2p2、2n2)とを備えた伝送線路(201)において、誘電体層(1a)を挟んで対向する信号用導体同士が異なる極性同士の電圧となるよう差動信号源(3)から差動信号を伝送線路に出力し、上記4つの信号用導体により差動信号を伝送線路(201)を同一方向に信号伝送させることにより、伝送される差動信号により誘電体層(1a)の中央部に電気壁と等価とみなせる電界分布を形成させる。

(もっと読む)

情報伝達装置

【課題】簡素な構成で複数のデータを確実に伝達できる情報伝達装置を提供する。

【解決手段】送信回路は、1つの信号ラインを介して信号長が基準時間の2倍であり所定のパルス期間を有するとともに基準時間より長い連続したパルス休止期間を有するヘッダパルス信号を送信する。その後、信号長が基準時間でありデータに応じたパルス期間を有するとともにパルス期間の前後にパルス休止期間を有するデータパルス信号を複数連続して送信する。マイクロコンピュータは、1つの信号ラインを介して送信回路の送信したパルス信号を受信し、受信したパルス信号からパルス休止時間に基づいてヘッダパルス信号を認識し、ヘッダパルス信号以降のパルス信号のパルス期間に基づいて複数のデータを求める。1つの信号ラインを介して複数のデータを送受信できる。従来のように、データ毎に回路を複数設ける必要がない。そのため、簡素な構成で複数のデータを確実に伝達できる。

(もっと読む)

通信方法、通信システム及びそのデバイス

【課題】第1デバイスと第2デバイスの間で1本の信号線だけを用いて双方向のシリアル通信を行うことができ、第2デバイスにて第1デバイスから送信された情報の誤りを検出できる通信方法、通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11から第2デバイス12に第1の通信フォーマットで情報をクロックと共に送信する第1モードと、第2デバイスから第1デバイスに第2の通信フォーマットで情報を送信する第2モードを有し、第1の通信フォーマットは、スタートビットに続いて、複数のデータビット及び複数の反転データビットと、複数のデータビットから生成したチェックビット及び反転チェックビットを有し、第2の通信フォーマットは、スタートビットに続いて、複数のデータビットと、複数のデータビットから生成したチェックビットを有する。

(もっと読む)

通信システム及びそのデバイス

【課題】1本の信号線を用いて双方向のシリアル通信を行う通信システム及びそのデバイスを提供することを目的とする。

【解決手段】第1デバイス11と第2デバイス12間を1本の信号線で接続し、互いにレベルの異なる第1レベルと第2レベル、及び前記第1レベルと第2レベルの中間レベルを用いてシリアル通信を行う通信システムであって、第1デバイスは、第1レベルと中間レベルを繰り返すことで第2デバイスにクロックを送信し、第2デバイスは、受信したクロックの中間レベルの期間に第2レベルを出力するか否かで第1デバイスに情報を送信し、第1デバイスは、第2デバイスが情報を送信していない場合に、クロックの中間レベルの期間に第2レベルを出力するか否かで前記第2デバイス12に情報を送信する。

(もっと読む)

伝送装置及びネットワークシステム

【課題】TDMデータをパケット化し伝送するネットワークシステムにおいて、パケットネットワーク上で発生する遅延変動を吸収するために、伝送装置内に具備した遅延変動吸収バッファにユーザデータを格納している時間を最適化し、エンド・ツー・エンドでの遅延時間によるリソースの過剰消費を抑止する。

【解決手段】伝送装置1は、TDMネットワーク7から受信したTDMフレームをパケット化してパケットネットワーク8へ送信し、また、パケットネットワーク8から受信したパケット信号をTDM化して前記TDMネットワークへ送信するものであり、パケットネットワーク上の伝送遅延時間を測定する手段106〜108、113と、測定した遅延時間から遅延変動時間を算出する手段109と、算出した遅延変動時間に基づいて、パケットネットワーク8から受信した信号をTDM化してTDMネットワークに送信するまでの時間を制御する手段112とを備える。

(もっと読む)

送信回路

【課題】出力するシリアルデータのビット位置を容易に特定することが可能な送信回路を得ること。

【解決手段】本発明にかかる送信回路は、シリアルクロックと当該シリアルクロックに同期したシリアルデータとを出力する送信回路1aであって、シリアルデータのビット位置を特定するためのパルス信号を、所定の間隔で生成し出力するシリアルデータ計数部3a、を備え、その回数を数えることにより、シリアルデータのビット位置を容易に特定可能な構成とした。

(もっと読む)

送受信装置及び信号伝送装置

【課題】一対の信号線からなる差動信号線に接続された送受信部が差動信号線を介して送信側又は受信側の何れに接続された場合にも通信を行うことが可能な送受信装置、及びそれを備えた信号伝送装置を提供する。

【解決手段】送受信装置1は、第1の信号線21及び第2の信号線22からなる差動信号線20を介して送信側又は受信側に接続され、送信側に接続されたときは第1の信号線21によって信号を受信し、受信側に接続されたときは第2の信号線22によって信号を送信する送受信部10と、送受信部10によって送信又は受信される信号を処理する信号処理部14とを備える。

(もっと読む)

超広帯域無線通信装置

【課題】10GHz程度の超広帯域を簡易な構成で利用可能とすることで、短距離高速通信を低価格で実現可能とする超広帯域無線通信装置を提供する。

【解決手段】 クロック153aをクロック152aより所定時間だけ遅らせることで、入出力処理部153は入出力処理部152より所定時間だけ遅れて動作するようにしている。バイアス手段154は、入出力処理部153からトリガ信号22が入力されると、これに一定のバイアスを付加している。コンパレータ155は、入出力処理部152からトリガ信号21を入力するとともに、バイアス手段154からバイアスが付加されたトリガ信号22を入力し、トリガ信号21がトリガ信号22よりも大きいときだけ、所定の出力を行うよう構成されている。

(もっと読む)

既存のネットワークケーブルを使用してネットワークを同期させるための方法およびシステム

【課題】既存のケーブルを使用してネットワークを同期させる。

【解決手段】ローカルエリアネットワーク102の第1のエンドシステム104のマスタ物理インタフェースデバイス131のメッセージ送信機134およびメッセージ受信機138に通信で結合された同期用送信機112と、ローカルエリアネットワークの第2のエンドシステム10)のスレーブデバイス132のメッセージ送信機136およびメッセージ受信機140に通信で結合された同期用受信機118とを含み、同期用送信機は、第1の差動ツイストペア接続108および第2の差動ツイストペア接続110を使用して、同期用受信機にタイミングメッセージを送信するように構成され、同期用送信機は、第1の差動ツイストペア接続および第2の差動ツイストペア接続を使用して、同期用受信機に同期用パルスを送信する。

(もっと読む)

単一導体上のデータの非同期通信のための方法と装置

【課題】 単一導体上のデータの非同期通信のための方法と装置を提供する。

【解決手段】 本発明は、集積回路チップ内部または集積回路チップ間、例えば小型積層チップ内に存在する複雑な集積システムにおけるデータの非同期通信に関する。本発明によると、送信は単一交換導体上で行われる。データは、送信データ項目の第1の値を表す第1のレベル(0)、送信データ項目の第2の値を表す第2のレベル(Vdd)、および非活性レベルを表す第3のレベル(Vmed)の少なくとも3つのレベルの電位の形式でこの導体Cech上に送信される。確認応答信号がデータと同じ交換導体上に送信される。この信号は好ましくは、受信器により交換導体を非活性電位レベルに強制設定する形式で、受信器により生成され、送信器はこの強制設定を検出する。

(もっと読む)

メモリ制御回路及びそれを用いたデータ伝送システム

【課題】送信機、受信機の双方において新たな入力端子を設ける必要がないデータ伝送システムを提供すること。

【解決手段】本発明に係るメモリ制御回路は、それぞれが第1及び第2の入力端子を備え、各前記第1の入力端子に外部メモリから受信したデータ信号が入力される複数のコンパレータと、前記外部メモリから受信した差動ストローブ信号の正相及び逆相の双方から、各前記第2の入力端子に入力される複数の基準電圧を生成する基準電圧発生回路と、を備えるものである。

(もっと読む)

受信回路

【課題】ビット幅の広いデジタル演算を必要とせずに、小さい回路面積及び消費電力で適応等化処理を実現できる受信回路を提供する。

【解決手段】受信回路は、等化係数に応じた等化処理を受信信号に施して等化された信号を出力する等化回路と、等化された信号と第1閾値との大小関係に応じた0及び1の信号値を有する第1の信号を求め、等化された信号と第2閾値との大小関係に応じた0及び1の信号値を有する第2の信号を求め、第1の信号中に現れる所定の0及び1のパターンの出現回数と第2の信号中に現れる所定の0及び1のパターンの出現回数との差分を計算する誤差計算回路と、差分に応じて等化係数を調整する適応等化制御回路とを含む。

(もっと読む)

1 - 20 / 195

[ Back to top ]