Fターム[5K029DD23]の内容

直流方式デジタル伝送 (8,390) | 伝送システム構成 (1,787) | 伝送路の構成 (708) | 並列伝送路 (120)

Fターム[5K029DD23]に分類される特許

1 - 20 / 120

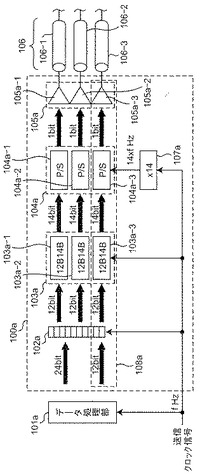

送信装置、受信装置及びシリアル伝送システム

【課題】24ビット、36ビットのデータを送信する場合に効率的なデータ符号化及び復号化方式を行うシリアル伝送システムを提供する。

【解決手段】自然数n×12ビットのパラレルデータをn個のシリアルデータに変換して各自然数mビットの送信信号を送信する送信装置であって、入力されるパラレルデータを12ビット毎のn個の12ビットのパラレルデータに分割する分割手段と、分割されたn個の12ビットのパラレルデータをそれぞれ14ビットのパラレルデータに12B14B変換して出力する符号化回路と、12B14B変換されたn個の14ビットのパラレルデータをそれぞれ1ビットのシリアルデータにパラレルシリアル変換して出力するパラレルシリアル変換回路と、パラレルシリアル変換されたn個の1ビットのシリアルデータを増幅してmビットの送信信号としてそれぞれn個の伝送路に送信するmビットドライバ回路とを備える。

(もっと読む)

半導体システムのための無線信号送受信装置、無線信号送信方法、及び無線信号受信方法

【課題】本発明は、制限された面積から充分なインダクタンスを確保して安定的に送受信できる半導体システムのための無線信号送受信装置を提供することを目的とする。

【解決手段】無線信号送受信装置100は、並列入力信号を直列信号に変換して出力し、直列入力信号を並列信号に変換して出力するサーデス信号およびサーデス回路105から出力される直列信号によりインダクタンスを発生し、外部装置と誘導結合現象によって発生した信号をサーデス回路105の直列信号に提供するカップリングパッド111を備える。

(もっと読む)

出力回路、信号伝送回路及び信号伝送方法

【課題】電源ノイズの低減を図ることができる出力回路を提供する。

【解決手段】本発明の実施の形態に係る出力回路Oは、論理信号を出力するCMOS回路OAと、CMOS回路OAと同じ論理信号を出力する、CMOS回路OAと並列に設けられた電流一定回路OBと、入力される選択信号Sに応じて、CMOS回路OAと電流一定回路OBのいずれか一方にデータDを入力し、データDに応じた論理信号を出力させる選択回路SLとを備え、電源ノイズを許容値以下に抑える必要がある場合に、電流一定回路OBを選択する。

(もっと読む)

容量性通信回路及び通信方法

【課題】電気自動車、モータドライバのような分野では、高電圧領域と低電圧領域とが採用されており、安全性の理由から、それぞれの電圧領域を互いに分離(絶縁)させ、高電圧から高感度回路を保護する。

【解決手段】デジタルデータ信号の周波数とは異なる周波数を有するキャリア信号を用いてこのデジタルデータ信号を通信する通信回路は、第1の組のキャパシタと、第2の組のキャパシタと、第1の回路と、第2の回路とを有する。第1の回路は、キャリア信号及びこのキャリア信号の反転とそれぞれ混合された混合データ信号を発生させ、キャリア信号及びこのキャリア信号の反転とそれぞれ混合された混合反転データ信号を発生させ、混合データ信号を第1の組のキャパシタに供給し、混合反転データ信号を第2の組のキャパシタに供給する。第2回路は、混合信号からデータ信号を再生させる。

(もっと読む)

集積回路チップ及びこれを含む送受信システム

【課題】 伝送チップ上でのデータピン配列と、伝送チップと受信チップとの間のライン配列とが互いに異なってもクロストークを防止できる技術を提供すること。

【解決手段】伝送チップと、受信チップと、前記伝送チップから前記受信チップにデータを伝送するための複数のラインとを備え、前記伝送チップは、前記複数のラインに伝送されるデータパターンと前記複数のラインの配列情報とに応じて、前記複数のライン上で発生するクロストーク防止動作を行うことを特徴とする。

(もっと読む)

メモリカードとホストデバイスとの間で通信を実現するための回路および方法

【課題】UHS-IIモードと従来のモードのいずれかで信号を伝送するための、簡素かつ効率的な回路および方法。

【解決手段】インターフェース回路は、メモリカードとホストデバイスとの間の通信を実現する。インターフェース回路は、ピンの第1のセットと、ピンの第2のセットと、制御ユニットとを含む。制御ユニットは、ピンの第1のセットを介して第1のモードで信号の第1のセットを伝送する場合、ピンの第1のセットを有効にしてピンの第2のセットを無効にし、ピンの第2のセットを介して第2のモードで信号の第2のセットを伝送する場合、ピンの第1のセットを無効にしてピンの第2のセットを有効にする。制御ユニットは、ピンの第2のセットのクロックピンを介して、第2のモードで、差動シグナリングによって、信号の第2のセットのクロック信号を伝送する。第2のモードでの信号伝送は、第1のモードでの信号伝送よりも高速である。

(もっと読む)

信号伝送回路

【課題】低コストかつ実装密度が高い回路基板を用いて、信号線間のクロストークノイズを低減するとともに、スタブによる反射ノイズを低減することのできる信号伝送回路を提供する。

【解決手段】本発明に係る信号伝送回路において、電子部品のリード端子と貫通ビアは表層配線で接続され、貫通ビアの途中に分岐を設けないように構成されている。さらに、第2電子部品を接続する第2配線間に、第1電子部品を接続する第1配線を配置し、第1配線と第2配線の間で信号をインターリーブ送信する。

(もっと読む)

データ伝送回路及びデータ送受信システム

【課題】データを伝送するにあたって発生するクロストーク及びSSOによるノイズを減らすことが可能なデータ伝送回路及びデータ送受信システムを提供する。

【解決手段】ニブルデータD0〜D3が2攻撃者1被害者パターンを有するか、全て同じ値を有する場合、反転信号をINV活性化するパターン感知部310と、ニブルデータD0〜D3を複数の伝送ラインLINE0〜LINE3に伝送し、反転信号INVに応じて、ニブルデータD0〜D3のうち一部のデータD2,D3を反転してまたは非反転で伝送するデータ伝送部320とを備える。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

通信システムおよび通信機

【課題】2つの通信機が同じ通信線を共用して共通の制御装置と通信するシステムにおいて、混信を許しつつも、混信によって正しくなくなってしまったデータを制御装置が通常通り扱ってしまう可能性を低減することを目的とする。

【解決手段】TPMS受信機3は、1つのフレームをボデーECU5へ送信する際、当該1つのフレームに含まれる複数のデータビットに基づく信号を上り信号線9a、9cに送出開始し、当該信号の送信中、上り信号線9a、9cに送出した信号と、自己チェック用配線9eから入力されるFB信号とを比較し、比較の結果、両者が一致しない場合は、当該1つのフレームをボデーECU5に破棄させるため、上り信号線9a、9cの信号レベルを所定の無効化期間だけ強制的に所定の信号レベルとするための所定の無効化信号(ローレベル信号)を、上り信号線9a、9cに送出する。

(もっと読む)

半導体集積装置およびそれを備える表示装置

【課題】電磁波の不要輻射および伝送欠陥を低コストで低減することができる、半導体集積装置およびそれを備える表示装置を提供することを目的とする。

【解決手段】タイミングコントローラIC400が含む出力インターフェース回路420_1は、出力バッファ422と、出力バッファ422の後段に設けられた減衰部424とを有している。出力バッファ422は、正側画像信号DV1(+)および負側画像信号DV1(−)からなる差動信号を出力する。減衰部424は、1対のローパスフィルタ425Aおよび425Bを有している。ローパスフィルタ425Aおよび425Bにより高周波成分がそれぞれ減衰された正側画像信号DV1(+)および負側画像信号DV1(−)は、それぞれ伝送線路610Aおよび610Bに与えられる。

(もっと読む)

電子機器、電子機器の制御方法および電子機器システム

【課題】ビデオ信号などのデジタル信号を他の電子機器との間で双方向に効率よく伝送可能とする。

【解決手段】シンク機器130とシンク機器140は例えば別部屋に配置されたテレビ受信機である。シンク機器間はケーブル300により接続される。このケーブル300には、Data0〜Data5の6本の差動信号レーンが用意され、機器間でデジタル信号の双方向伝送が可能である。また、ケーブル300には、双方向通信ラインが用意されている。この双方向通信ラインは、例えば、HDMIのCECラインと同等の双方向制御ライン、あるいは、双方向差動通信ラインとして構成される。機器間でデジタル信号を伝送する際、機器間で双方向通信ラインを利用して通信が行われ、使用レーン数、使用レーン番号、伝送方向、搬送クロック周波数などの伝送路構成が決定される。この決定に基づいて、各機器のデータ送受信部132,142における伝送路構成が制御される。

(もっと読む)

半導体デバイス、画像処理装置

【課題】複数のデータ伝送路のタイミングを低コストで同期可能な半導体デバイスを提供すること。

【解決手段】送信側から受信側にデータをシリアル送信する半導体デバイス100であって、データ転送の合間に、同期判定用のコードを送信する同期判定コード送信手段301,302と、送信側と受信側に共通のクロック信号を提供するクロック信号提供手段103と、クロック信号に同期して同じデータを送信する複数の伝送路117と、受信側に提供されたクロック信号の位相を、それぞれ異なる所定量遅延させ複数の遅延クロック信号を生成するクロック生成手段110と、遅延クロック信号に同期して伝送路を介して送信されたデータを取り込む複数の受信バッファ111と、コードを予め定められた規則に基づき検証して複数の受信バッファから1つの受信バッファを、複数の遅延クロック信号から1つの遅延クロック信号をそれぞれ選択する選択手段113、115と、を有する。

(もっと読む)

長距離光伝送装置、及び長距離光伝送システム

【課題】長距離伝送路区間における通信速度がより高速化しても、比較的簡素な構成で安定した通信を実現する。

【解決手段】40Gbpsで通信を行うメディアコンバータ6,8は、光トランシーバ20、フレーム処理部22、FEC24〜30、長距離TR32〜38、及び波長フィルタ40を備えている。また、これらの間では、電気信号を4本のレーンでパラレル転送する。FEC24〜30、及び長距離TR32〜38は10Gbpsの通信速度に対応しており、各レーン別に転送された電気信号に対してFECを生成し、電気信号を光信号に変換する。

(もっと読む)

信号伝送回路、スイッチング素子駆動回路及び電力変換装置

【課題】送信側の異常、ノイズの混入など送信側動作状態の安否を随時に確認することができるとともに、スイッチング時の基準電位の変動による誤動作ついても確実に防止する。

【解決手段】送信信号に基づいて正論理と負論理の相補信号を出力する相補信号駆動回路と、この相補信号をそれぞれ独立したチャンネルで伝送する相補信号伝送路と、相補信号伝送路の信号を受信して、両者の排他的論理和に基づいて、両者が相補信号であるか否かを判定する相補信号判定回路を設け、相補信号判定回路の出力信号と送信信号との論理積を受信信号とする。

(もっと読む)

信号送受信手段

【課題】矩形波信号の伝達遅れを補償できる信号送受信手段を提供する。

【解決手段】第1矩形波信号U_H等と第2矩形波信号U_L等を、送信装置4から送信し、伝送路6を伝送させ、受信装置5で受信し、送信装置4と受信装置5では、第1矩形波信号U_H等の立ち上がりのタイミングと、第2矩形波信号U_L等の立ち下がりのタイミングとが同期している送受信システム3に用いられる信号送受信手段9において、伝送路6より送信装置4側で、第1矩形波信号U_H等又は第2矩形波信号U_L等について、立ち上がりと立ち下がりの相互間の反転を行い、伝送路6より受信装置5側で、第1矩形波信号U_H等又は第2矩形波信号U_L等について、その反転を行い、伝送路6では、第1矩形波信号U_H等と第2矩形波信号U_L等の両方の立ち上がりのタイミング、又は、両方の立ち下がりのタイミングが同期している。

(もっと読む)

先頭レーン検出回路及び方法並びにデスキュー回路及び方法

【課題】本発明は、アライメントマーカの検出順序に依存しない先頭レーン検出回路及び方法並びにデスキュー回路及び方法の提供を目的とする。

【解決手段】本願発明の先頭レーン検出回路は、基準レーンを設定する基準レーン設定部12と、アライメントマーカのタイミング信号T0〜T19が入力され、基準レーン#0のタイミング信号T0の時点から基準レーン#0以外のレーンのタイミング信号T1〜T19の時点までの遅延時間ΔT1〜ΔT19を測定する時間測定部11と、全てのレーンの遅延時間ΔT1〜ΔT19を測定する前に所定時間を経過すると基準レーンを順次変更する基準レーン変更部14と、所定時間内に全てのレーンの遅延時間ΔT1〜ΔT19を測定すると、基準レーンのレーン番号#0を先頭レーンのレーン番号に決定する先頭レーン決定部13と、を備える。

(もっと読む)

アライメントマーカ重複判定回路、アライメントマーカ重複判定方法およびプログラム

【課題】データを複数のレーンに振り分け、レーン毎にアライメントマーカを挿入して行われるデータ通信における、アライメントマーカの誤設定を検出する。

【解決手段】受信装置に含まれる整列同期回路において、アライメントマーカ検出回路110−0〜110−(n−1)がライン0〜ライン(n−1)に含まれるアライメントマーカを検出する。そして、検出されたアライメントマーカの示すレーン番号が複数のラインについて同一であると判定した場合に、レーン番号重複判定回路130がアライメントマーカ重複を示す信号を出力する。

(もっと読む)

データ受信装置および適応等化回路

【課題】回路規模を抑制し、消費電力を低減する。

【解決手段】複数の受信回路2a〜2dは、伝送線路に接続され、伝送線路からデータ信号を受信する。受信回路2a〜2dは、受信したデータ信号の波形を整形するための等化器を具備している。適応等化回路3は、複数の受信回路2a〜2dの全部または2以上の所定数ずつに対して1つ設けられ、対応した受信回路2a〜2dの等化器の、波形整形をするための等化係数を算出し、対応した受信回路2a〜2dに出力する。

(もっと読む)

データ伝送システムと装置と方法

【課題】高速なデータ伝送を可能としながら、CMOS素子の消費電力の低減を可能とするシステム、装置、方法の提供。

【解決手段】前後して入力される二つのNビット幅データを並列配置したビット幅が2×NのビットのN+Nビット幅データを出力する送信装置において、検出回路(トグル検出器)2は、前記二つのNビット幅データを予め定められた正順で上位側と下位側に配置した第1の配置と、前記二つのNビット幅データを、前記第1の配置とは上位側と下位側を交換した逆順で配置した第2の配置とのうち、前回並列出力したN+Nビットデータから反転するビットの個数が小さい方の配置はいずれであるかを検出して前記配置情報(A)として出力し、ビット幅変換回路3は、前記検出回路2からの前記配置情報(A)にしたがって、前記前後して入力される二つのNビット幅データを配置してN+Nビットデータを並列に出力するとともに配置情報を出力する。

(もっと読む)

1 - 20 / 120

[ Back to top ]