Fターム[5K047AA01]の内容

デジタル伝送方式における同期 (12,489) | 目的、効果 (2,701) | 同期品質の向上 (1,344)

Fターム[5K047AA01]の下位に属するFターム

同期確立時間の短縮 (150)

高精度の同期維持 (163)

疑似同期引込み防止 (35)

タイミング品質の向上 (665)

Fターム[5K047AA01]に分類される特許

61 - 80 / 331

情報処理装置又は情報処理方法

【課題】 外部デバイスコントローラの外部デバイスから受信するデータが、外部デバイスコントローラの出力クロックに対して1サイクル以上遅延する場合、従来の構成では遅延の有無を検出できないことがある。

【解決手段】 外部デバイスコントローラのデータ取り込みタイミングを調節する際に、所定のゲーティング情報に基づいて外部デバイスコントローラの出力クロックをゲーティング又はゲーティング解除することで、データ取り込みタイミングを調節するためのキャリブレーションの精度を向上させる。

(もっと読む)

情報処理装置又は情報処理方法

【課題】 外部デバイスから情報処理装置の受信するデータが、情報処理装置のクロックに対して1サイクル以上遅延する場合、情報処理装置側でデータを取り込むタイミングを調節する処理が増加してしまう。

【解決手段】 受信することになるキャリブレーションパターンとサイクル遅延量との関係を示す遅延情報を予め記憶しておくことで、サイクル遅延量(情報処理装置側のデータをラッチする機構の停止制御をする信号を遅延させる量に相当する)を検出する処理を短縮する。

(もっと読む)

通信ネットワークのネットワーク要素

そのローカルクロックを基準クロック信号に同期するように構成された、通信ネットワーク用のネットワーク要素が開示される。ネットワーク要素は、内部同期トランスポートプロトコルをサポートするように構成された内部モジュールおよび内部モジュールに接続されたコネクタを備えるメインボードと、コネクタに取り外し可能に接続されるように構成されたプラグ着脱可能モジュールとを備える。プラグ着脱可能モジュールは、コネクタに接続されたときに、他のネットワーク要素と外部同期情報を交換し、外部同期情報は、内部同期トランスポートプロトコルとは異なる外部同期トランスポートプロトコルに従ってフォーマットされ、内部同期トランスポートプロトコルに従ってフォーマットされた内部同期情報を内部モジュールと交換し、内部同期トランスポートプロトコルと外部同期トランスポートプロトコルとをインターフェースするように構成される。  (もっと読む)

(もっと読む)

映像信号とセンサー信号の同期化システム及び方法

本発明は、カメラから入力される映像信号と、それぞれの映像信号に対応するセンサー信号に対して、それぞれのセンサーモジュールとカメラ装置に同期用時計が内蔵されており、同期化装置でそれぞれの装置に同期信号を伝送して同期用時計を同期化させた後、それぞれのセンサーモジュールとカメラ装置で獲得した信号に取得時間を付加し、中央制御装置及びコンピューター装置に伝送して映像信号とセンサー信号の同期化を行うことができる映像信号とセンサー信号の同期化システム及び方法に関する。本発明による映像信号とセンサー信号の同期化システムは、 第1同期用時計が内蔵されており、被写体を撮影して映像信号を獲得し、前記獲得した映像信号に前記第1同期用時計による取得時間情報を付加して出力するカメラ装置と、第2同期用時計が内蔵されており、前記映像信号に対応したセンサー信号をセンシング動作によって生成し、前記生成されたセンサー信号に前記第2同期用時計による取得時間情報を付加して出力するセンサー装置と、前記センサー装置から前記取得時間情報の付加されたセンサー信号を受信してコンピューター装置に伝送するように制御する中央制御装置と、基準時計を内蔵し、前記第1同期用時計と前記第2同期用時計の同期のための基準時間を所定の間隔で前記カメラ装置及び前記センサー装置に同時に伝送する同期化装置と、前記中央制御装置から前記取得時間情報の付加されたセンサー信号を受信し、前記カメラ装置から前記取得時間情報の付加された映像信号を受信してそれぞれの信号の取得時間情報を確認し、それぞれの信号を同じ時間帯に再構成して前記映像信号と前記センサー信号を同期化するコンピューター装置と、を備える。 本発明によれば、周辺環境によって収集された映像信号及びセンサー信号の同期性を確保することができる。また、多チャンネルであり、高速である映像信号とそれに対応したセンサー信号の同期化を通じてユーザーに向上したサービスを提供することができる。さらに、映像信号及びセンサー信号を獲得して有線または無線で伝送する通信手段に関係なく、両信号の同期化を容易に具現することができ、それにより、映像信号とセンサー信号を正確かつ便利に分析することができる。 (もっと読む)

クロック異常検知システム

【課題】シリアル通信を用いてクロックの異常動作を検知することで、クロックの異常動作によるシステムの誤作動を防止するクロック異常検知システムを提供する。

【解決手段】クロック異常検知システムの受信機2は、送信機1から送信されたシリアル通信(調歩同期)で受信した信号を周期的に読み込み、各ビットの区切りの直後に読み込んだビット値がその次の区切りの直前に読み込んだビット値と異なる場合、クロック異常検知装置23はクロック異常と判定して警報を出力する。

(もっと読む)

データ伝送速度の1/2周波数クロックを用いる光受信機のタイミング抽出回路及び光送受信機のデューティずれ対応回路

【課題】光送受信機に関し、特にデータ伝送速度の1/2周波数クロックを用いる光受信機の改良されたタイミング抽出回路及び光送受信機のデューティずれ対応回路を提供する。

【解決手段】タイミング抽出回路は、ビットレートB(bit/s)のデータ信号とB/2(Hz)のクロック信号との位相比較を2/B(sec)間隔で行う位相比較回路を含むPLL回路を用い、所定パタ―ンのデータ信号の受信により位相比較回路からの位相比較情報出力が無くなったことを検出する検出回路と、その検出により同期を保持するためにクロック信号の位相を制御する制御回路と、を有する。さらに、デューティずれ対応回路は、PLL回路が同期した点前後の入力データ間のデューティの判定結果にもとづいて前後のデータ識別位相を制御する。

(もっと読む)

スレーブ装置、ホスト装置、ハブ装置、および通信システム

【課題】複数のスレーブ装置を同時に初期化すると、ピーク電流が通信システムの最大定格電流を超過する恐れがある。

【解決手段】スレーブ装置は、STB−Lシンボルを受信したときは同期シンボルの受信を待ってバックエンドモジュールの起動を開始し、STB−Hシンボルを受信したときはPLLロックと同時にバックエンドモジュールの起動を開始する。ホスト装置は電源投入直後、システムの特性に応じてSTB−LまたはSTB−Hのいずれかのシンボルを送信する。

(もっと読む)

半導体集積回路装置

【課題】外部のデバイスに接続される回路とLSI内部の回路との間におけるタイミング設計を不要とすること。

【解決手段】半導体集積回路装置は、外部デバイスに対して接続されるインタフェース回路であって第1のクロック信号が供給される第1の回路と、第1のクロック信号を分周した第2のクロック信号が供給される第2の回路と、第2のクロック信号を第1のクロック信号に基いて遅延させた送受信タイミング信号を生成するタイミング生成回路と、第2の回路から受信した信号を第1のクロック信号に同期してサンプリングする複数段のシフトレジスタと該複数段のシフトレジスタに対する入出力信号に含まれるハイレベルの信号とロウレベルの信号の多数決を送受信タイミング信号に同期して行うとともに多数決により決定された信号を第1の回路に出力する多数決回路とを有する第1の位相調整回路とを備えている。

(もっと読む)

スペクトル拡散クロックの同期捕捉および同期追跡

【課題】シリアルデータストリームに組み込まれたスペクトル拡散クロックの同期捕捉および同期追跡方法を提供する。

【解決手段】対応する方法およびコンピュータ読み込み媒体を有する装置は、回復したスペクトル拡散クロック信号と、スペクトル拡散クロック信号を含むシリアルデータストリームとの間の位相差を表す誤差信号を生成するように構成された位相検出器と、スペクトル拡散クロック信号の現在のスペクトル拡散サイクルからの誤差信号と、スペクトル拡散クロック信号の以前のスペクトル拡散サイクルからの誤差信号とに基づいて、回復したスペクトル拡散クロック信号を提供するように構成された位相選択器とを備える。

(もっと読む)

時刻情報取得装置、および、電波時計

【課題】 送信局を適切に判別するとともに、標準時刻電波の秒の先頭位置を精度良く特定できる。

【解決手段】 相関値算出部25は、予測波形データ生成部23において生成された複数の予測波形データのそれぞれと、波形データ切り出し部24からの入力波形データとの間の相関値を算出する。送信局判別部27は、相関値算出部25において算出され累算された相関値の累算値に基づいて、標準時刻電波を送信する送信局の種別を判別する。また、相関値比較部26は、累算値を比較し、かつ、送信局判別部27により判別された送信局の種別に基づいて、累算値の最適値を特定し、CPU11が、最適値を示した予測波形データに基づいて、タイムコードにおける秒パルス位置を特定する。

(もっと読む)

データ処理装置及びデータ処理システム

【課題】信号受信から信号送信までのタイミング誤差を小さくする。

【解決手段】複数のデータ処理ノードが所定のトポロジで通信路に接続されたデータ処理システムにおいて、データ処理ノードのデータ処理装置は、受信信号に基づいて受信クロック信号を再生し、再生された受信クロック信号に同期して受信データ再生部(122)で受信信号から受信データを再生すると共に、再生された受信データに対する送信データを送信データ生成部(123)で生成し、送信部(125)で送信データから送信信号を生成して送信クロック信号に同期して通信路に送信する、通信機能を備える。データ処理ノードは更に、受信データ再生部による信号の受信から送信部による送信信号の送信までに許容される時間に対して処理時間が短いとき、その誤差時間を検出する検出部(124)を有する。送信部は検出部による誤差時間の経過を待って送信データの送信を開始する。

(もっと読む)

半導体集積回路

【課題】広い周波数範囲で高調波電流成分を削減して高周波ノイズを低減することのできる半導体集積回路の提供を図る。

【解決手段】クロック信号CKに同期して動作する複数のデジタル回路11,12を含む半導体集積回路であって、前記各デジタル回路は、周波数が同じで位相が異なる第1および第2クロック信号CKa,CKbの一方を受け取り、前記第1および第2クロック信号の位相差は、m,nを自然数として、ほぼ[2m−1]/2nであるように構成する。

(もっと読む)

通信システム

【課題】受信装置が、送信装置から受信した通信データにおけるフレームの位置をより高い精度にて特定することが可能な通信システムを提供すること。

【解決手段】通信システム300は、互いに通信可能に接続された送信装置310及び受信装置320を含む。送信装置310は、デリミタシンボルと、当該デリミタシンボルに後続する補助シンボル及びデータシンボルを含むフレームと、を含む複数のシンボルからなる通信データを送信する送信部311を備える。受信装置320は、送信装置310により送信された上記通信データを受信し、当該受信した通信データのうちの、上記デリミタシンボル及び上記補助シンボルからなる位置検出用シンボルの予め設定された基準値と一致する程度が予め設定された閾値よりも高い部分を検出することにより、当該通信データにおける上記フレームの位置を特定する同期処理実行部321を備える。

(もっと読む)

光通信装置

【課題】デジタルコヒーレント受信において、立ち上げ時および信号断復帰時のライン側同期に時間がかかったり、同期がかからなかったりというリスクを回避する。

【解決手段】デジタルコヒーレント受信方式を採用し、受信信号のサンプリングおよびデジタル信号処理の内部クロックを、立ち上げ時もしくは信号断時には外部クロックに同期させ、通常動作時には受信信号のラインクロックに同期させる光通信装置であって、デジタル信号処理過程の信号からサンプリングのずれを示す位相信号を生成する位相検出部と、前記位相信号の振幅が所定の閾値を超えている場合に、前記外部クロックから前記ラインクロックへの切替を指示するクロック切替判定部とを備える。

(もっと読む)

通信システム、基地局装置及び通信制御方法

【課題】 複数の基地局間の送信タイミング及び受信タイミングの同期を、簡易かつ確実に自律的に確立する通信システムを提供する。

【解決手段】 複数の基地局装置を備えた通信システムにおいて、基地局装置は、自局を示す識別情報と自局の同期の階層レベルを示す情報とを含む基地局情報を他の基地局装置へ通知する通知手段を有する。

(もっと読む)

オーディオ同期装置、オーディオ同期方法

【課題】マルチ・ストリームの同期を正確に行うこと

【解決手段】アプリケーションは、第1のストリームと第2のストリームとを同期させるためのタグを生成し、タグを第2のストリームに付加する。タグ処理部103はアプリケーションから入力されたタグを第1のストリームのタイムスタンプに基づいて第1のストリームに付加する。ミキサーB50は、第1のストリームに付加されたタグと、第2のストリームに付加されたタグとを比較する。タグの値が一致する場合、ミキサーB50は第1のストリームと第2のストリームとをミキシングして出力する。タグの値が一致しない場合、ミキサーB50は前記第1のストリームを出力する。

(もっと読む)

GEPONシステム、局側装置及び端末側装置

【課題】局側装置の基準クロックを端末側装置において再生可能にする。

【解決手段】GEPONシステムは、局側装置10と端末側装置20とを含む。局側装置10は、網基準クロックを受けて装置クロックを生成する装置クロック生成部11と、装置クロックを動作クロックとし、入力データにタイムスタンプ情報を付加して送信データを生成するPON−OLTブロック13と、網基準クロックとタイムスタンプ情報との間の相関を表す相関情報を生成し、下りデータに多重する基準位相検出制御部12とを備える。端末側装置20は、局側装置10から送信された送信データに含まれるタイムスタンプ情報及び相関情報に基づいて、網基準クロックを再生する基準位相情報受信制御部23及び網基準クロック再生部24を備える。

(もっと読む)

クロックデータ再生回路

【課題】VCOの発振周波数のばらつきを補償し、低ジッタで電源電圧・温度変動耐性が大きいクロックデータ再生回路を提供する。

【解決手段】再生クロックを出力する第1の発振回路と、第1の発振回路と同一周波数のクロックを出力する第2の発振回路と、第2の発振回路が出力するクロックと参照クロックを周波数比較し、その周波数誤差に応じた周波数制御信号Aで第1〜第2の発振回路の発振周波数を制御するPLL手段とを備えたクロックデータ再生回路において、第1〜第2の発振回路の回路間ばらつきによる発振周波数のずれを調整する回路間ばらつき調整信号Cを入力する端子と、周波数制御信号Aと回路間ばらつき調整信号Cを加算する加算器とを備え、第1〜第2の発振回路はそれぞれ1つの制御端子を備え、第2の発振回路の制御端子に周波数制御信号Aを入力し、第1の発振回路の制御端子に加算器の出力信号を入力する構成とする。

(もっと読む)

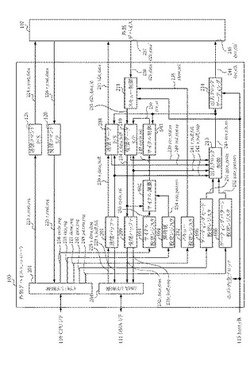

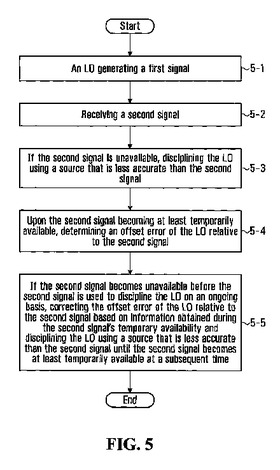

局部発振器を調整する装置及び方法

装置は、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第1信号を生成する局部発振器(LO)と、タイミング情報、周波数情報、位相情報及びそれらの組み合わせの内の少なくとも1つを有する第2信号を受信する入力を有するLOエラー補正部とを有し、第2信号はLOを調整するために使用され、LOエラー補正部は、第2信号がLOを調整するために利用可能でなくなった場合に、第2信号より精度が低いソースを用いてLOを調整し、第2信号が少なくとも一次的に利用可能になった場合に、第2信号に対するLOのオフセットエラーを判定し、当該装置が継続的にLOを調整するために第2信号を利用する前に、第2信号が利用可能でなくなった場合、第2信号が一次的に利用可能であった期間内に取得された情報に基づいて、第2信号に対するLOのオフセットエラーを補正し、第2信号が以後に少なくとも一次的に利用可能になるまで、第2信号よりも精度が低いソースを用いてLOを調整する。  (もっと読む)

(もっと読む)

クロックを並列データに整列させるための回路

【課題】クロック信号を並列データに整列させるための方法を提供する。

【解決手段】クロックシフティング回路10は、入来クロック信号8を入来データ信号16に対してシフトし、データクロッキング回路20は、シフト済みクロック信号を使用して、入来データ信号16を再クロックする。クロックシフティング回路10は、位相ロックループ回路2に直列に接続されている複数のDフリップフロップ回路4,6を連結して備える。データクロッキング回路20は、それぞれの入来データビット16を受信し、ミキサ22に対するローカルオシレータとして働く真−補数ブロック50,58を備える。複数のシフト済みクロック信号62,54,64,56は、入来クロック信号16に対して90度、180度、及び270度シフトされたものなど、が生み出される。

(もっと読む)

61 - 80 / 331

[ Back to top ]