Fターム[5K047LL05]の内容

デジタル伝送方式における同期 (12,489) | 通信制御 (259) | 速度変換 (147) | S/P変換 (44)

Fターム[5K047LL05]に分類される特許

1 - 20 / 44

シリアル同期検出回路及び同期検出方法

【課題】異なるプロトコルのシリアル通信に対応可能であって、より回路規模を抑制したシリアル同期検出回路及び同期検出方法を提供する。

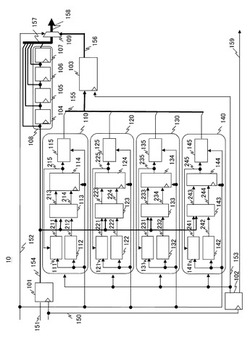

【解決手段】本実施の形態にかかるシリアル同期検出回路10は、それぞれ異なるビット長の同期コードを有する複数のプロトコルに対応可能なシリアル同期検出回路である。シリアル同期検出回路1は、同期コードを含むシリアル信号を所定ビット数単位のパラレル信号に変換するシリアルパラレル変換回路101と、変換されたパラレル信号と、複数のプロトロコルに含まれる任意のプロトコルの同期コードを前記所定ビット数に分割した同期期待値とを、所定ビット数単位で順に繰り返し比較して、同期コード全体を比較することにより、同期を検出する同期検出回路110〜140とを備えている。

(もっと読む)

シリアル通信回路

【課題】低消費電力モードから復帰時にその受信シンボルでスキュー調整を実施することができ、通常通信状態への迅速な復帰を行う。

【解決手段】符号化された複数のレーンのシリアル受信信号からクロックの再生を行い、受信シンボルを各レーン毎に再生し、バイトアライン及びSP変換後、復号化して複数のレーンの受信シンボルを同一のクロックに同期した受信シンボルに変換して出力する物理層受信回路と、複数のレーンの受信シンボルに対してレーン間のシンボルスキューを調整するレーン間スキュー調整回路とを備えたシリアル通信回路において、所定の検出基準シンボルを受信シンボルからレーン毎に検出し、カウンタ回路により検出信号に応答して検出信号の計数を開始し、カウンタ値の選択信号に対応する遅延量だけ、物理層受信回路から出力される複数のレーンの受信シンボルに対して遅延させてレーン間のシンボルスキューを調整する。

(もっと読む)

受信装置

【課題】パターン検出回路の回路規模を削減し、コストダウンすることができる受信装置を提供する。

【解決手段】Mビット長の特定パターンを含むシリアルデータをNビット(N<M)幅のパラレルデータに変換する変換回路と、パラレルデータの、連続するNビットの範囲のそれぞれのビットを先頭とするLビット(N≦L<M)の部分と特定パターンの対応する部分とを比較する比較回路と、比較回路が、連続するNビットの範囲の先頭からKビット目(K=0〜N−1)を先頭とするLビットの部分と特定パターンの先頭からLビットの部分との一致を検出し、さらに、L/Nの商をq、余りをrとして、Nビットの範囲およびK、N、q、rによって決まる特定の周期内に、特定のビットを先頭とするJビット(J≦M−L)の部分と特定パターンのL+1ビット目からJビットの部分との一致を検出する検出回路とを備える。

(もっと読む)

受信装置

【課題】特定パターンの連続検出を効率良く行い、かつ連続検出回数を正しく判断することができる受信装置を提供する。

【解決手段】受信装置は、Mビット長の特定パターンを含むシリアルデータをNビット(N<M)幅のパラレルデータに変換するシリアルパラレル変換回路と、所定のビット幅のパラレルデータを格納するレジスタ群と、所定のビット幅のパラレルデータのうちの連続するMビットの複数の格納パターンのそれぞれと特定パターンとを比較する比較回路と、比較回路が、パラレルクロックの第1の周期内に、Nビットの範囲の先頭からKビット目(K=0〜N−1)を先頭とする格納パターンと特定パターンとの一致を検出し、さらに、M/Nの商をQ、余りをRとして、Nビットの範囲およびK、N、Q、Rによって決まる特定の周期内に、特定のビットを先頭とする格納パターンと特定パターンとの一致を検出して、特定パターンを含むシリアルデータの受信を検出する検出回路とを備える。

(もっと読む)

シリアル−パラレル変換回路、クロックデータリカバリ回路、表示装置用駆動回路及びシリアル−パラレル変換方法

【課題】クロックの動的消費電力及びデータの動的消費電力を低減することが可能なシリアル−パラレル変換回路を提供する。

【解決手段】シリアル−パラレル変換回路1は、入力されるシリアルデータを出力するデータ出力モードと、一定の値の固定データを出力するデータ固定モードとのいずれかの動作モードで動作する複数のデータ固定回路13と、複数のデータ固定回路13から出力されたシリアルデータ及び固定データが入力され、マルチクロックに基づいて、複数のデータ固定回路13から出力されたシリアルデータをビットデータ毎に記憶しパラレルデータとして出力する複数のフリップフロップ11と、を備えるものである。

(もっと読む)

パラレルデータ出力制御回路及び半導体装置

【課題】常に信頼性の高いパラレルデータ出力制御が行えるをパラレルデータ出力制御回路を得る。

【解決手段】CPU12はバッファ13からのリクエストRQに応答して内蔵RAM11よりデジタルデータをバッファ13に出力する。バッファ13は複数段構成のFIFOを有し、FIFOの各段は1単位(10ビット)のデジタルデータを格納可能であり、バッファ13全体としてFIFOの構成段数単位分のデジタルデータを格納することができる。レジスタ14は出力制御クロックCK15に同期して、バッファ13内部に格納したデジタルデータを1単位ごとに取り込む。レジスタ14に格納されたデジタルデータがD/A変換用データDataとしてパラレルDAC2に出力される。WR信号出力タイマ17は出力制御クロックCK15に同期して“L”の1ショットパルスを有する書き込み制御信号WRを生成する。

(もっと読む)

光パケットスイッチ装置

【課題】伝送路の帯域利用効率を向上できる光パケットスイッチ装置を提供する。

【解決手段】光パケットスイッチ装置10は、光カプラ13と、光スイッチ部12と、光スイッチ制御部14とを備える。光スイッチ制御部14は、光電変換部16と、シリアル/パラレル変換部18と、並び検出部17と、並び換え部19と、フレーム同期部20と、方路検出部24と、制御信号生成部26と、並び検出部17からのフレーム同期パターンの並び情報に基づいて、光スイッチ部12に光スイッチ制御信号を出力するタイミングを調整するタイミング調整部27とを備える。

(もっと読む)

位相調整回路、受信装置、および通信システム

【課題】回路構成の複雑化、消費電力の増大を抑止しつつ、複数チャネル間の同期化が可能となり、高速シリアル通信に適用することが可能な位相調整回路、受信装置、および通信システムを提供する。

【解決手段】位相調整回路310は、クロックに応答して所定の位置に同期パターンが挿入されているシリアルデータをパラレルデータに変換するシリアルパラレル変換部313と、シリアルパラレル変換部313によるパラレルデータの同期パターンの位置を検出する同期パターン位置検出部316と、同期パターン位置検出部316で検出された同期パターン位置情報により、同期パターン位置に合わせてパラレルデータおよびクロックの位相を調整する調整部315とを有する。

(もっと読む)

通信インタフェース装置及び該通信インタフェースを備えた半導体装置

【課題】複数のレーンを有する通信インタフェースにおいて消費電流の増大を抑制し各レーン間でパラレルクロック信号を同期させる装置の提供。

【解決手段】シリアルクロック線21にシリアルクロック信号が供給され、レーン1はシリアルクロック線からシリアルクロック信号を入力して第1のレーン内に分配し、該シリアルクロック信号サンプリングクロック信号とするカスケード接続されたフリップフロップ(FF)12、13を有し、FF13の出力の反転信号がFF12に帰還入力される分周回路を備え、FF13の出力信号がパラレルクロック信号としてレーン1内に分配され、レーン2ではシリアルクロック信号を入力してレーン内に分配し、レーン1のFF12の出力を受け、レーン2の前記シリアルクロック信号でサンプルするFF13を備え、FF13の出力がパラレルクロック信号としてレーン2内に分配されると共にレーン2のFF12に帰還入力される。

(もっと読む)

送信回路および通信システム

【課題】複数送信レーン間の同期を行うために分配する制御信号のタイミング制約を緩和でき、設計工数を削減することが可能な送信回路および通信システムを提供する。

【解決手段】並列に配置され、供給されるパラレルデータをシリアルデータに変換して出力する複数のレーン部330−0〜330−3と、基準クロックに位相同期した駆動クロックを、イネーブル信号CLKENに応じた駆動クロックの複数サイクル分経過してから複数のレーン部に出力するクロックイネーブラ部320とを有し、複数のレーン部330−0〜330−3の各々は、クロックイネーブラによる駆動クロックを分周して分周クロックおよびロード信号を生成する分周器331−0〜33−3と、分周器による分周クロックおよびロード信号、並びに駆動クロックに同期してパラレルデータをシリアルデータに変換するパラレルシリアル変換器332−0〜332−3と、を含む。

(もっと読む)

アライメントマーカ重複判定回路、アライメントマーカ重複判定方法およびプログラム

【課題】データを複数のレーンに振り分け、レーン毎にアライメントマーカを挿入して行われるデータ通信における、アライメントマーカの誤設定を検出する。

【解決手段】受信装置に含まれる整列同期回路において、アライメントマーカ検出回路110−0〜110−(n−1)がライン0〜ライン(n−1)に含まれるアライメントマーカを検出する。そして、検出されたアライメントマーカの示すレーン番号が複数のラインについて同一であると判定した場合に、レーン番号重複判定回路130がアライメントマーカ重複を示す信号を出力する。

(もっと読む)

シリアル受信装置並びにシリアル受信装置の制御方法及びプログラム

【課題】EBからのコードの読み出しを一時的に止めることができ、かつEBからのコードの読み出しを止めてもRDチェックが正しく機能するシリアル受信装置を提供する。

【解決手段】制御部30は、パラレルコードのうちSKPシンボルを除いた残りのパラレルコードを記憶手段21に書き込むように書き込み手段22を制御する機能と、記憶手段21に書き込まれたパラレルコードがあるときにのみ当該パラレルコードを読み出すように読み出し手段23を制御する機能と、記憶手段21からパラレルコードを読み出す際にコード有効信号Validを出力する機能とを有する。8B/10Bデコーダ40は、コード有効信号Validが出力されたときに、パラレルコードの復号化及びRD検出を実行し、当該RDと前回のコード有効信号Validが出力されたときに検出したRDとの規則性をチェックする。

(もっと読む)

シリアル転送装置及び方法

【課題】受信側でのデータの待ち合わせ時間を短くし、送信側と受信側との間に生ずるレイテンシを小さくする。

【解決手段】シリアル転送装置1は、データを送信する送信部2と、データを受信する受信部3と、送信部2と受信部3とを接続し、データを伝送する複数のシリアル伝送路4と、受信部3において、各シリアル伝送路4のスキューに関するレーン間スキュー情報を生成し、レーン間スキュー情報を送信部2に送信するレーン間スキュー情報生成部5と、送信部2において、レーン間スキュー情報に基づいてデータの各シリアル伝送路4への振り分けを決定する変換ルールを生成するデータ変換ルール生成部6とを備える。

(もっと読む)

シリアルパラレル変換回路

【課題】N倍(Nは、2以上の整数)の関係にある複数の伝送レートに対応しつつ、回路規模の削減を図ることが可能なシリアルパラレル変換回路を提供する。

【解決手段】シリアルパラレル変換回路1は、シリアル入力される伝送信号をS/P変換してパラレルデータIndtを生成するS/P変換部2と、S/P変換部2で生成されたパラレルデータIndtからフレーム同期信号を検出する同期検出部5と、Aレート及びBレートに対応する第1及び第2のクロック信号CLKA、CLKBを順次に選択して出力するクロック選択部3とを備える。同期検出部5は、Aレート及びBレートのうちの最速のレートに対応するクロック信号に従って動作する。また、S/P変換部2は、変換ビット数が固定されつつ、変換速度が動作クロックにより変更可能に構成され、クロック選択部3から出力されるクロック信号CLKを動作クロックとして用いる。

(もっと読む)

受信装置及びその受信方法

【課題】従来の受信装置は、精度良くデータを受信できないという問題があった。

【解決手段】本発明にかかる受信装置は、位相が異なる複数のクロックCLK_1,CLK_2,CLK_3を生成する多相クロック生成回路3と、複数に分岐された外部データとクロックCLK_1,CLK_2,CLK_3とが入力され、複数に分岐された外部データをそれぞれ異なるクロックでラッチすることによりクロックタイミングの異なるデータDATA_1,DATA_2,DATA_2を同時に複数取得するラッチ部と、各データDATA_1,DATA_2,DATA_2の誤り検出を行うエラーチェック部と、誤り検出結果に基づいてエラーがないと判定されたデータを選択して受信データとして出力するセレクタ回路7と、を備える。このような回路構成により、精度良くデータを受信することができる。

(もっと読む)

クロックリカバリ回路およびデータ再生回路

【課題】クロックジッタを低減可能なクロックリカバリ回路およびデータ再生回路を提供する。

【解決手段】シリアル入力信号を第1のクロック信号に同期させてサンプリングしたサンプリングデータを出力するサンプラ13、サンプリングデータに基づき、第1のクロック信号とシリアル入力信号のクロックとの位相関係を表すシリアル位相情報信号を出力する位相比較回路14、シリルア位相情報信号を第2のクロック信号に同期させてシリアルパラレル変換したパラレル位相情報信号を出力するシリアルパラレル変換回路17、パラレル位相情報信号に基づき、位相偏差信号と位相遅進信号を演算するデジタルフィルタ回路16、位相偏差信号と位相遅進信号とに基づいて生成した位相制御信号を第2のクロック信号より高速の第3のクロック信号に同期して出力する位相制御量処理回路20および、位相制御信号に基づき、外部から入力する基準クロック信号の位相を調整した第1のクロック信号を出力する位相補間回路12を備える。

(もっと読む)

信号処理装置、及び信号伝送方法

【課題】バスシステムにおいて伝送遅延による受信不良を回避することが可能な信号処理装置を提供すること。

【解決手段】第1のバスに接続されたマスター機器から供給されるクロックと、当該クロックに同期して前記マスター機器から送信されるデータとを受信するマスター側受信部と、前記第1のバスとは異なる第2のバスに接続されたスレーブ機器に対し、前記マスター側受信部により受信されたクロック及びデータを送信するスレーブ側送信部と、前記スレーブ側送信部により送信されたクロックに同期して前記スレーブ機器から送信されたデータを受信してバッファに格納するスレーブ側受信部と、前記マスター側受信部によりクロック及びデータが受信されるタイミングで、当該クロックに同期して前記バッファに格納されているデータを前記マスター機器に送信するマスター側送信部と、を備える、信号処理装置が提供される。

(もっと読む)

直列信号の受信装置、直列信号の受信方法、直列伝送システムおよび画像形成装置

【課題】直列伝送システムにおいて、直列信号を伝送するクロックのジッタを含めた補正処理を実現できるようにする。

【解決手段】受信装置21は、受信部71、検出部72、サンプリングポイント決定部73およびサンプリング部74を備える。検出部72は、受信部71で受信した伝送クロックRX_CLKについて複数のデューティ比で、受信部71で受信した補正パターン信号RX_DATAに対する位相関係を検出する。サンプリングポイント決定部73は、検出部72による複数のデューティ比での検出結果を基に、受信部71で受信したシリアル信号に対するサンプリングポイントを決定する。サンプリング部74は、サンプリングポイント決定部73で決定されたサンプリングポイントで、受信部71で受信したシリアル信号をサンプリングする。

(もっと読む)

シリアル通信装置

【課題】マスターとスレーブ間で制御信号のシリアル通信を行う際に、システムに応じた最適な通信レートで通信を行うことが可能なシリアル通信装置を提供する。

【解決手段】シリアル通信装置に、制御信号のサンプリングクロックを入力とし、当該サンプリングクロックに位相同期した逓倍クロックを生成する位相同期回路と、外部設定された分周比を用いて前記逓倍クロックを分周して転送クロックを生成する分周回路と、前記制御信号を前記転送クロックを用いてパラレル/シリアル変換して出力するP/S変換器とを設ける。

(もっと読む)

シリアル通信装置

【課題】制御信号に適したシリアル伝送によって配線数を削減することが可能なシリアル通信装置の提供する。

【解決手段】複数の送信制御信号を送信シリアル信号に変換して外部に出力するP/S変換器と、外部から入力された受信シリアル信号を外部から入力された受信転送クロックを用いて複数の受信制御信号に変換するS/P変換器と、送信シリアル信号に同期した送信転送クロックを外部に出力するクロック出力回路と、受信シリアル信号に同期した受信転送クロックをS/P変換器に出力するクロック入力回路とを具備する。

(もっと読む)

1 - 20 / 44

[ Back to top ]