Fターム[5M024PP01]の内容

Fターム[5M024PP01]に分類される特許

1 - 20 / 1,958

半導体装置及び半導体装置の動作方法

半導体装置

半導体装置

半導体装置

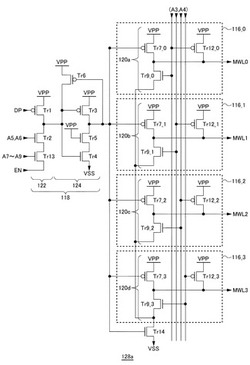

【課題】ワード線の選択回路のサイズを縮小することにより、半導体装置のサイズを縮小する。

【解決手段】メインワード線は、複数のグループに分類され、メインワードドライバはアドレス情報にしたがってメインワード線を選択する。4本のメインワード線MWL0〜MWL3から構成される1つのグループが、1つのレベルシフタ118を共有する。アドレス情報は、グループ選択のための第1アドレスとメインワード線選択のための第2アドレスを含む。メインワードドライバは、第1アドレスにしたがって、第1グループ選択回路や第2グループ選択回路128aを選択し、選択された第2グループ選択回路128aのレベルシフタ118は活性電位(ローレベル)を出力する。そして、選択された第2グループ選択回路128aに所属する複数のメインワード線MWL0〜MWL3のうちの1本が第2アドレスA3,A4により選択される。

(もっと読む)

半導体装置

【課題】複数個のメモリチップが積層された構造を有する半導体装置の信頼性を向上させる。

【解決手段】半導体装置は、複数のビットラインと複数のワードラインとの交差点に複数個のメモリセルが配列される複数個のメモリチップが垂直方向に積層され、いずれか一つのメモリチップには複数個のメモリチップの各々に配列された複数のビットラインと連結されアクティブにされるメモリチップのビットラインをイネーブルさせるためのビットラインセンスアンプと、複数個のメモリチップの各々に配列された複数のワードラインと連結されアクティブされるメモリチップのワードラインをイネーブルさせるためのサブワードラインドライバを含み、ビットラインセンスアンプとサブワードラインドライバがいずれか一つのメモリチップに備わる。

(もっと読む)

半導体装置

【課題】半導体装置が動作状態から待機状態に移行するとき、内部電源電圧の目標電圧からの上昇を抑制する。

【解決手段】非動作状態の負荷回路への電源電流の供給に用いられる電源回路15において、トランジスタPTRS1は、外部電源電圧を受ける電源ノードと出力ノード18との間に接続される。比較器50は、第1の入力端子および参照電圧が入力される第2の入力端子を有し、第1および第2の入力端子間の電圧差に応じた制御電圧をトランジスタPTRS1の制御電極に出力する。分圧回路40は、出力ノードの電圧を分圧した電圧を比較器50の第1の入力端子に出力する回路であり、分圧比を変更可能である。電源回路15は、負荷回路が動作状態のときに、分圧回路40の分圧比を第1の分圧比から第1の分圧比よりも高い第2の分圧比に変更する。

(もっと読む)

半導体メモリ装置

【課題】本発明は、リフレッシュ動作の時、電流消耗を減らすことができる半導体メモリ装置を提供する。

【解決手段】第1ビットライン分離信号に応答してビットラインとセンスアンプとを連結及び分離させる第1スイッチと、第2ビットライン分離信号に応答してビットラインバーとセンスアンプとを連結させる第2スイッチと、及びリフレッシュ動作の時、第2ビットライン分離信号のイネーブル区間の長さよりイネーブル区間が短いリフレッシュ用ビットライン分離信号を生成して第2スイッチに提供する制御部を備える。

(もっと読む)

半導体メモリ装置およびその駆動方法

【課題】従来のDRAMでは微細化と共にデータの読み出しエラーが発生しやすくなる。

【解決手段】第1のビット線BL_1の微弱な電位の変動はNチャネル型トランジスタTNRとPチャネル型トランジスタTPRで構成される第1のインバータで反転され、第1のスイッチである第1の選択トランジスタST1を介して、第2のビット線BL_2に出力される。第2のビット線BL_2の電位は、第1のビット線BL_1の電位とは反転した電位であるため、第1のビット線BL_1と第2のビット線BL_2の電位差は拡大する。この拡大した電位差を公知のセンスアンプSA_1/2あるいは、第2のインバータ(Nチャネル型トランジスタTNLとPチャネル型トランジスタTPLで構成される)と第1のインバータで構成されるフリップフロップ回路等で増幅する。

(もっと読む)

半導体装置

【課題】メモリに入力される外部データが、内部のメモリの処理速度に対して高い場合でも、データの書込みミスなく処理でき、消費電力を抑える半導体装置を提供する。

【解決手段】メモリアレイ制御回路12A〜12Nは、第1の動作として、記憶部に格納されたデータであって、メモリ100の処理速度のうち第1の処理速度で処理可能なデータを読出し、複数のメモリアレイ10A〜10Nへ書込みし、メモリアレイ制御回路12A〜12Nは、第2の動作として、残余データのうちメモリ100の処理速度のうち第2の処理速度で処理可能なデータを読出し、複数のメモリアレイ10A〜10Nへ書込みを行う。

(もっと読む)

半導体装置

【課題】回路ブロックの数が2のべき乗で表すことのできない数であっても、簡単な回路構成でプリデコード動作を行う。

【解決手段】それぞれ異なるロウアドレスが割り当てられた複数のワード線WLを含む複数のメモリマットと、メモリマットにそれぞれ含まれるワード線WLの最小アドレスMINADDとアドレス信号のビットとを比較することによって、メモリマットのいずれかを選択するマットセレクタ12aと、アドレス信号のビットに基づいて、選択されたメモリマットに含まれるワード線WLのいずれかを選択するワードセレクタ12bとを備える。

(もっと読む)

メモリインターフェースおよび画像処理装置

【課題】 フレームメモリにすでに書き込まれた直前のフレームを構成する画素の画素値を示すデータの出力を開始するまでの遅延時間の短縮化が図られたメモリ制御回路、および回路規模の削減化が図られた画像処理装置を提供する。

【解決手段】 垂直同期信号VSYNCの立ち下がりエッジをSDRAMコントローラ22で検知して、初期アドレスにクリアされたアドレス信号A,読み出しを指示するコマンドCを生成してSDRAM10に供給し、SDRAM10から所定の範囲の過去データを先読みして読み出し用FIFO23に格納しておき、現在データの入力が開始された後に読み出し用FIFO23から読み出して出力する。

(もっと読む)

アドレスデコーディング方法とこれを用いた半導体メモリ装置

【課題】半導体メモリ装置の読み出し動作および書き込み動作フェイルを防止することができる半導体メモリ装置を提供する。

【解決手段】読み出し信号または書き込み信号に応答して、選択的にイネーブルされる第1テストモード信号ないし第3テストモード信号に応じて遅延量が調整されるストローブクロックを生成するストローブクロック生成部10と、ストローブクロックの第1レベルに応答してアドレスをラッチし、ストローブクロックの第2レベルに応答して、アドレスをデコーディングして内部アドレスを生成する内部アドレス生成部20と、内部アドレスをデコーディングして選択的にイネーブルされる出力イネーブル信号を生成する出力イネーブル信号生成部30と、を備える。

(もっと読む)

半導体装置

【課題】不要にリフレッシュ周期が変更されることによる無駄な消費電流を削減する。

【解決手段】複数の半導体チップを備え、複数の半導体チップのうちの第1の半導体チップは第1の温度センサを有し、第1の半導体チップとは異なる第2の半導体チップはリフレッシュ動作を必要とする半導体チップであって、第1の半導体チップの第1の温度センサの出力結果に応じて第2の半導体チップのリフレッシュ周期が変更される。

(もっと読む)

メモリにおけるピーク電力管理のためのメカニズム

【課題】メモリにおけるピーク消費電力管理のためのメカニズムを提供する。

【解決手段】サブ・アレイ・ブロックを含むメモリ・ストレージ・アレイにおけるピーク電力を管理するためのメカニズムが、サブ・アレイ・ブロックの各々に対するワードライン信号の起動を互い違いにすることにより、読み出し動作及び書き込み動作と関連したピーク電流を削減することができる。具体的には、1つのサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの書き込みワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、各々のサブ・アレイ・ブロックに対してワードライン信号を生成することができる。さらに、ワードライン・ユニットは、所与のサブ・アレイ・ブロックの読み出しワードライン信号が、別のサブ・アレイ・ブロックの読み出しワードライン信号と同時に1つの論理レベルから別の論理レベルに遷移しないように、ワードライン信号を生成することができる。

(もっと読む)

メモリ制御装置

【課題】メモリ書き込み時の消費電力を削減できるメモリ制御装置を提供する。

【解決手段】メモリ制御装置は、データバスを介してメモリ装置にデータをバースト転送するデータ出力バッファ回路390と、データのうちのメモリ装置内のメモリセルへの書き込みを禁止するデータを示すマスク信号をメモリ装置に出力するマスク信号出力バッファ回路190とを具備し、データ出力バッファ回路390は、マスク信号が書き込み禁止を示すときに出力ノードをハイインピーダンスにする。

(もっと読む)

昇圧回路及びその給電方法

【課題】簡略化された回路構成でノイズ低減効果を持つ多相駆動型の昇圧回路を実現する。

【解決手段】昇圧回路は、所定周期のクロック信号を出力する発振回路と、前記クロック信号の1本の配線に直列接続され、トータル遅延時間が前記所定周期よりも長い複数の遅延回路と、前記複数の遅延回路に対応して前記1本の配線に接続された複数の分割昇圧回路と、を含む。

(もっと読む)

半導体装置

【課題】小規模な論理回路によって基準レイテンシとオフセットレイテンシを用いた演算を行う。

【解決手段】例えば、基準レイテンシCLの値を示す複数のビットA0〜A3のそれぞれと、オフセットレイテンシSRLの値を示す複数のビットC0〜C2のそれぞれと、を論理合成して複数の制御信号E0〜E3を生成する論理回路100と、複数の制御信号E0〜E3をデコードして複数の制御信号ULPCL4〜ULPCL15を生成する論理回路200とを備える。本発明によれば、基準レイテンシCLの値とオフセットレイテンシSRLの値をデコードする前に演算していることから、より小規模な論理回路によって調整レイテンシULPCLを算出することが可能となる。

(もっと読む)

半導体装置

【課題】スタンバイ状態時における第1導電型のトランジスタでの劣化を抑制可能な半導体装置を提供する。

【解決手段】半導体装置は、第1導電型のトランジスタを含み縦列接続された複数の回路と、複数の回路の其々の入力端子のうち他の回路と接続された接続入力端子と接続し接続入力端子の電圧を制御するための制御信号の活性化に応じて、接続入力端子に、該接続入力端子から電圧を受け付ける回路内の第1導電型のトランジスタを非導通状態とする第1の電圧を供給する制御回路と、を備える。

(もっと読む)

マルチバンクメモリデバイスのメモリバスアウトプットドライバ及びそのための方法

【課題】マルチバンク構成のメモリにおいて、選択バンクの読み出しデータを低面積、低電力、高速に出力可能な方法を提供する。

【解決手段】第1バス128に結合された第1トライステートデバイスにおいて、センスアンプの第1センスアウトプットおよび第2センスアウトプットを受け取ることと、第2バス130に結合された第2トライステートデバイスにおいて、センスアンプの第1センスアウトプットおよび第2センスアウトプットを受け取ることと、バス選択インプットに応じて第1バスまたは第2バスを駆動するために第1トライステートデバイスおよび第2トライステートデバイスの1つを選択的にアクティブにする。

(もっと読む)

半導体記憶装置

【課題】オープンビット線方式における電源ノイズの影響を低減した半導体記憶装置を提供する。

【解決手段】半導体記憶装置は,列方向に両側に延びる一対のビット線に接続するセンスアンプを列方向に直交する行方向に複数配置したセンスアンプ群が列方向に複数配置され,列方向に隣接するセンスアンプ群それぞれに接続される複数のビット線が互いに平行に配置され,列方向の両端に配置されたセンスアンプ群に接続された一対のビット線のうち列方向の両端側の複数のビット線にそれぞれ平行に配置された複数の未使用ビット線を有し,複数のワード線が行方向に配線され,複数のビット線及び複数の未使用ビット線と複数のワード線との交差位置にメモリセルが配置されたメモリセルアレイと,メモリセルアレイの列方向の一端に配置され,複数のセンスアンプ群に内部電源を内部電源線を介して供給する内部電源回路とを有し,未使用ビット線は内部電源配線に接続されている。

(もっと読む)

1 - 20 / 1,958

[ Back to top ]