国際特許分類[G06F1/24]の内容

物理学 (1,541,580) | 計算;計数 (381,677) | 電気的デジタルデータ処理 (228,215) | グループ3/00〜13/00および21/00に包含されないデータ処理装置の細部 (14,213) | リセット手段 (409)

国際特許分類[G06F1/24]に分類される特許

11 - 20 / 409

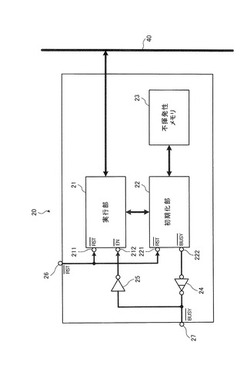

画像形成装置、情報処理装置および機能モジュール

【課題】動作可能になるまでの所要時間を短くした情報処理装置等を提供する。

【解決手段】機能モジュール20は、予め定められた機能を実行する実行部21、実行部21を初期状態に設定する初期化部22、実行部21を初期化するためのデータを保持する不揮発性メモリ23、オープンドレインバッファ24、インバータ25を備えている。初期化信号51(/RST)がアサートになると、実行部21は動作状態から停止状態に移行し、初期化部22は停止状態から動作状態に移行する。そして、初期化信号51(/RST)がネゲートになると、初期化部22は、不揮発性メモリ23に保持されていたデータを読み出し、実行部21を初期化する。実行部21の初期化が完了すると、実行部21は停止状態から動作状態に移行する。

(もっと読む)

情報処理装置及びその起動方法

【課題】本発明は、優先順位の高い機能の初期化時間を遅延させることなく、全機能の初期化時間を短縮することが可能な情報処理装置、及びその起動方法の提供を目的とする。

【解決手段】本発明は、初期化により利用可能となる機能を複数有する情報処理装置である。本発明の情報処理装置は、前記機能をそれぞれ初期化する複数の初期化手段1〜nと、前記初期化手段1〜nの実施順序を決定する初期化順序決定手段12と、装置処理負荷を監視する装置処理負荷監視手段13と、実施中の前記初期化手段が1つ以上ある場合、当該1つ以上の初期化手段の処理に遅延が生じない第1の閾値に基づいて前記装置処理負荷を判定することにより、次の前記初期化手段Iの実施タイミングを決定する初期化タイミング決定手段15とを備える。

(もっと読む)

起動時の信頼性とPOST時間の短縮を図る方法およびコンピュータ

【課題】動作の安定化とPOST時間の短縮の両立を図ったコンピュータの起動方法を提供する。

【解決手段】BIOS_ROM33は第1のPOSTコードと第1のPOSTコードよりも短い時間で処理を終了する第2のPOSTコードを格納する。プロセッサ11がリセットされてからOSのロードを開始するまでの間に、開放センサ39がカバー蓋の開放の有無を検出して内部デバイスに対する物理的なアクセスが行われた可能性を判断する。物理的なアクセスの可能性が高いと判断したときに第1のPOSTコードを実行し、物理的なアクセスの可能性が低いと判断したときに第2のPOSTコードを実行する。

(もっと読む)

リセット回路

【課題】ウォッチドッグのための特殊な構成を追加することなく、マイコンラッチ時に自動的かつ確実にマイコンにリセットをかける

【解決手段】水晶振動子Xtalを用いた水晶発振回路からクロック信号を入力されるマイコン200のリセット回路100であって、マイコン200は、出力がHighとLowとで周期的に変動するGPIO端子201を備え、クロック信号の入力が停止されたときに自動的にリセット状態となる構成とされ、リセット回路100は、GPIO端子201の出力をコンデンサを用いて平滑し、平滑電圧がHighとLowの中間電位のときは水晶振動子Xtalの負性抵抗より小さい抵抗を発生して水晶振動子Xtalに印加し、平滑電圧がHighとLowのいずれかになると水晶振動子Xtalの負性抵抗以上の抵抗を発生して水晶振動子Xtalに印加する。

(もっと読む)

リセット回路

【課題】複数の電源電圧を駆動電圧とするSoC IC(System on a Chip Integrated Circuit)に対し、負荷変動やノイズに影響されること無く、複数の電源電圧の供給とリセット解除タイミングとのシーケンスを守ってリセットを行う。

【解決手段】供給ラインL1とリセット端子16との間においてエミッタを供給ラインL1に向けつつコレクタをリセット端子16に向けて介挿されたトランジスタTr1と、トランジスタTr1のベースとグランドとの間においてコレクタをトランジスタTr1のベースに向けつつエミッタをグランドに向けて介挿されたトランジスタTr2と、トランジスタTr1のコレクタとグランドとの間においてコレクタをトランジスタTr2のコレクタに向けつつエミッタをグランドに向けて介挿されたトランジスタTr3とを備える。

(もっと読む)

電子機器

【課題】瞬断等による従来見られた不具合発生を防止する。

【解決手段】リセット端子を備えるメインICと、リセット端子に接続された追加回路とを備え、追加回路は、メインICへ供給される電源電圧を入力する第1入力端子と、メインICが稼働状態にあるときにメインICから出力される制御信号を入力する第2入力端子と、第2入力端子からの制御信号の入力があり且つ第1入力端子における電源電圧のレベルが上記所定レベルより高い所定のしきい値を下回ったときにオン状態となるスイッチ素子とを備え、スイッチ素子がオン状態となったときにリセット端子にリセット信号を与え、メインICは、リセット端子にリセット信号が与えられたときにリセット状態へ移行する。

(もっと読む)

記録装置及びその動作の制御方法

【課題】記録装置が省電力モードからの復帰する時に、SDRAMに関する不要な初期化処理を省略して高速な復帰処理を行うことである。

【解決手段】動作状態から停止状態に遷移する際、SDRAMをセルフリフレッシュ動作させるかどうかの情報をフラグに保持する。停止状態からの復帰時にフラグを参照し、停止状態においてSDRAMがセルフリフレッシュ動作を行っていた場合は初期化処理を省略する。

(もっと読む)

電子制御装置及びリセット制御方法

【課題】電力消費量の低減化に優れた電子制御装置を提供する。

【解決手段】電子制御装置は、リセット信号出力手段と、制御手段とを備える。前記リセット信号出力手段は、リセット解除状態において電力を消費するデジタル回路に対して、リセット信号を出力する。前記制御手段は、前記リセット信号の第1の出力形態により前記デジタル回路をリセット状態に制御してから前記リセット状態を解除する第1のリセット制御、及び前記リセット信号の第2の出力形態により前記デジタル回路を継続的に前記リセット状態に制御する第2のリセット制御を選択的に実行する。

(もっと読む)

端末装置並びにフリーズ検出方法及び端末装置の制御方法

【課題】細かい設定をすることなく、自動的にフリーズ状態を検出し、リセット処理等を行う端末装置の提供。

【解決手段】端末装置は、電源からCPUに供給される電流値を測定する電流測定部と、前記CPUをリセットするリセット制御部と、前記CPUと独立して動作し、動作モードに反した電流値の定常状態が観測された場合、前記リセット制御部に前記CPUをリセットさせる電流監視部と、を備える。

(もっと読む)

半導体装置

【課題】本発明は、第1状態と第2状態との二つの状態のうち、第1状態に初期化し、初期化した第1状態に対応する電位の信号を生成することが可能な半導体装置を提供する。

【解決手段】本発明は、“0”(第1状態)と“1”(第2状態)との二つの状態のうち、“0”に初期化し、初期化した“0”に対応する電位の信号Aを生成することが可能な半導体装置10である。半導体装置10は、並列に複数接続され、“0”と“1”との二つの状態を保持することが可能なフリップフロップ回路2と、複数のフリップフロップ回路2と接続し、複数のフリップフロップ回路2のうち、少なくとも一つのフリップフロップ回路2で保持する状態が“0”の場合、“0”に対応する電位の信号を生成し、出力するAND回路3とを備える。

(もっと読む)

11 - 20 / 409

[ Back to top ]